与多疑人共事,事必不成。

与好利人共事,己必受累。

-- 曾国藩

开始前请大家回忆一下动态功耗的公式。工作电压和翻转频率会直接影响动态功耗值,那么是不是可以在这两个参数上做做文章来降低芯片功耗呢?其实很多低功耗设计方法就是基于这个基础。

一个思路是通过降低工作频率来降低所有cell的翻转频率,需要注意的是,这并不能减少能量(energy)的消耗。也就是说相同的电路,仅仅是工作频率不同,完成同样的功能,每个cell翻转的次数是一样的,只不过所需的时间长短不同。因此消耗的能量是一样的,只是功耗(能量/时间)不一样。

第二个思路是通过降低工作电压来降低功耗,这种方法会直接减少消耗的能量。

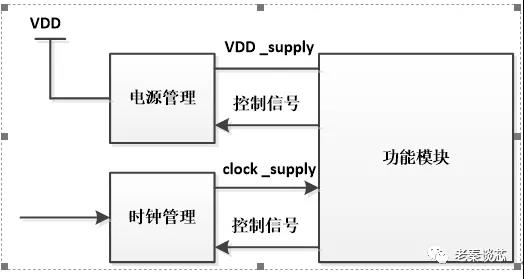

我们在做SoC设计时,一般都会在保证满足最大工作负载的前提下,选择最慢的时钟频率和工作电压。那么还有机会来降低电压和时钟频率吗?其实只有很少一部分芯片会一直工作在满负载(比如挖矿),大部分芯片会时而满负荷,时而空闲(比如手机SoC,CPU等)。所以我们可以通过一些方法来根据芯片工作负荷,相应调整工作电压和时钟频率。在芯片负荷大时候工作在高频高压,负荷小时工作在低频低压。这就是今天要讲的动态电压/频率调节,DVFS(Dynamic Voltage Frequency Scaling)。其实电压和频率调节并不是一定关联的,可以根据SoC实际情况选择只做DVS或者DFS。所以接下来会分别讲电压和频率调节的技术方法。

图1 DVFS示意图

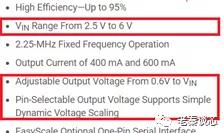

目前有两种方式能够支持DVS:片内调节和片外调节。片内调节就是通过调节芯片内部的电源管理IP;片外调节就是通过芯片的管脚来控制片外的电源管理芯片。片外调节方式需要的稳定时间比较长,一般需要几十微秒到几十毫秒,优点是电源转换效率相对较高;针对片外调节时间过长的缺点,人们又研究出片内调节的方法,一般调节时间会在几十到几百纳秒,但是相对转换效率低。采用片内调节带来的另外一个问题是,把电源管理IP做在片内会提高设计复杂性,增大芯片面积。

图2 电源管理芯片TPS62400特性列表

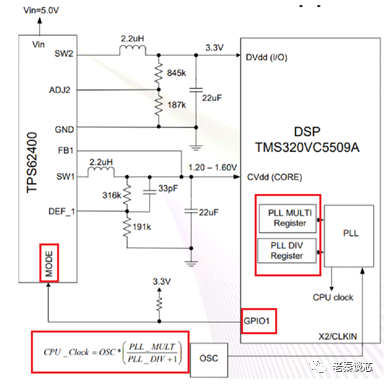

同样时钟频率调节也有两种主要办法:一种是通过重新配置PLL,另一种是通过数字分频模块。一般PLL会有数字接口来配置,说简单点就是把PLL的输入时钟通过几次乘/除运算来得到想要的稳定输出频率,而乘数和除数就是通过PLL的数字接口给进去的。这种方法需要的调节频率时间较长,因为重新配置后PLL需要一定时间才能稳定(PLL会有lock信号指示是否稳定),而且设计需要的相关设计较复杂。如有必要时可以考虑双PLL切换。

图3 PLL结构和配置示意图

第二种方法是数字分频,这种方法不需要重新配置PLL并等待,缺点是可能分频出来的时钟其占空比不是50%。另外,使用数字分频可以提供细粒度的频率调节,而通过PLL只能实现粗粒度的调节。在实际设计中可以根据要求搭配使用。

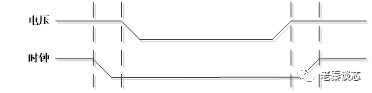

如果要在芯片中同时实现电压和频率调节,一定要注意调节的顺序。对于降频降压来说,要先降频再降压;反过来必须是先升压再升频。其中的道理大家仔细想想便知。

图4 DVFS降压/降频和升压/升频的顺序示意图

以上讨论的都是DVFS的调节方法,还有一个重要的方面是DVFS的判定,可以基于软件,也可以基于硬件。简单说,就是核心处理器通过软件方式来收集主要模块的工作负荷以及内部温度传感器等等信息,还是设计一个硬件模块来收集信息并判定芯片工作状态。不论哪种方式,现在都有不少算法和文章可以参考借鉴,如果大家感兴趣可以自行翻阅。如果芯片设计较为复杂,还是建议采用软件方式,可以灵活调整,而且现在的主流OS都有支持DVFS的软件框架,用起来也比较方便。最后贴一张TI的DVFS参考设计图帮大家直观感受一下。

图5 DVFS参考设计

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/57Ad-d4U\_-gmYLQFul1HjA

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。