忍耐是痛的,但是它的结果是甜蜜的。

-- 卢梭

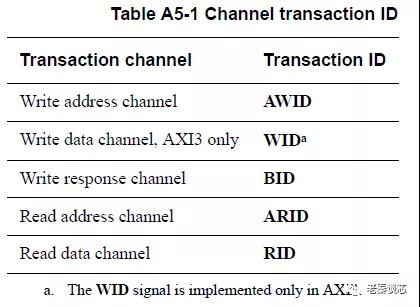

今天先来看一下传输标识(transaction identifier)的概念,主要是ID信号。

开始之前先讲几个概念,首先是outstanding(想不好怎么翻译,有的人译为超前)传输。如果没有outstanding能力,或者说outstanding=1时,主机的读操作顺序是:读地址命令->等待读数据返回->读地址命令->等待读数据返回->…如此往复。主机的写操作行为是:写地址->写数据->等待写响应返回->写地址->写数据->等待写响应返回->…如此往复。每一次新的传输要等上一次传输结束,总线的利用率不高。而如果outstanding能力为N>1的话,则读操作时,可以连续发N个读地址命令,在这期间如果读数据没有返回,则需要等待读数据返回,如果有读数据返回,则返回了几个,那么仍然可以接着发几个。也就是说,“在路上” 的读命令(或者读数据)最多可以是N。对于写操作,可以连续发出N组写地址(写数据)命令,这期间如果写响应没有返回,则必须等待写响应返回才能接着发写地址(写数据)命令,如果有写响应返回,则返回了几个,那么仍然可以接着发几组。也就是说,“在路上” 的写响应最多可以是N。

还有一个概念是乱序(out of order)传输。如果不支持乱序,那么返回的读数据必须按照读事务的顺序返回。如果是一次突发传输,返回数据中间不能插入其它的读事务数据。如果中间允许插入其它事务的数据,就是支持交织。

换种说法,outsatanding是对地址而言,一次突发还没结束,就可以发送下一个地址。而乱序和交织则是相对于传输事务,out-of-order说的是发送transaction和接收的cmd之间的顺序没有关系,如先接到A的cmd,再接到B的cmd,则可以先发B的数据,再发A的数据;交织指的是A的数据和B的数据可以交错,如A0->B0->A1->B1->B2->B3。

如果SoC中是多主机多从机的结构,支持上述的传输特性无疑会极大的提高总线互连的利用率,主机可以对不同地址或从机进行连续访问,而从机返回数据的先后可以不按照主机的发出事务顺序。当然,这也对设计提出了挑战。

一般从机的数据准备时间不由主机控制,数据就绪顺序与事务到达顺序不一致是可能的。因此需要相应的机制来标识数据所属的事务。而这,就是通过ID信号来实现的。

首先从读事务的 ARID 来看,主机为发出的读事务设定 ARID。

对于给定ID值的所有事务都必须保持有序,但对具有不同ID值的事务的顺序没有限制。单个物理端口支持乱序(out of order)事务,这样看起来有多个逻辑端口,每个逻辑端口按顺序处理其事务。通过使用AXI ID,主机可以无需等待前一个事务完成,就可以发出下一个事务。这可以提高系统性能,因为它支持事务的并行处理。

对于读数据排序,从机要保证RID的值与对应的ARID值匹配。互连必须确保从具有相同ARID值的事务序列中读取的数据以不同的从机为目标,由主机按其发出地址的顺序接收。从设备的读取数据重新排序深度(read data reordering depth)由从设备自己决定,不受主设备影响。

对于写数据排序,主设备必须保证写数据与发出的事务地址顺序相同。互连必须保证不同主设备的写数据与事务地址同序。也就是说,主设备保证自己的写事务顺序,互连保证不同主设备的顺序。

AXI3支持不同ID的写数据交织(interleaving)。但是,Write interleaving增加了系统总线设计的复杂度,而且很容易造成死,所以AXI4中不支持了。

这就有了一个新的概念,排序模型(ordering model)。相同ID和目的地的事务请求必须保证顺序;返回的相同ID的事务响应要与请求顺序相同。Ordering model不保证下列间的顺序:

- 不同主机的事务

- 读和写事务

- 不同ID的事务

- 到不同外设区域(peripheral regions)的事务

- 到不同存储空间(memory location)的事务

AXI4中除去那些重要的信号,还有一些可选信号,也可称为边带(sideband)信号。接下来简单过一下。首先是AxQOS,AXI4通过这些信号支持QOS(Quality of Service),AWQOS和ARQOS都是4bit的信号。协议里面并没有规定具体的用法,只是建议用AxQOS信号作为区分优先级使用,数值越大表示优先级越高。看到这,我们大概也明白了什么是QOS了,说白了,就是在资源有限的情况下,尽可能的保证高优先级的模块或组件获得足够的资源,比如内存带宽。举个例子就好理解了,比如去银行办业务,VIP客户的需求会被优先处理,普通客户都在拿号排队,VIP客户去了可以直接加塞儿。所以,所谓的服务质量就是优先级排队,看人下菜碟儿,哈哈。回到我们的芯片设计,还是以内存带宽为例,对于手机SoC或通用的图像GPU而言,显示接口模块显然需要稍高一些的优先级,否则打游戏时显示图像不流畅会极大的影响用户体验。不同的SoC中拥有的系统资源各不相同,需求也各不相同。对于SoC来说,QOS是一个系统问题,所以AXI协议中没有规定具体的实施,这要依赖于系统架构设计。也正是因为这样,协议规定AXI的事务排序优先于QOS排序。

另外一组信号是AWREGION和ARREGION,4bit宽度,用于支持多区域接口(multiple region interface)。AxREGION用于唯一标识多个不同的区域,提供高阶地址位的解码。区域标识符(region identifier)必须在任何4K字节的地址空间内保持不变。使用AxREGION意味着从机上的单个物理接口可以提供多个逻辑接口,每个接口在系统地址映射中具有不同的位置。从机不必支持不同逻辑接口之间的地址解码。

AXI4也提供了一组称为USER的用户自定义信号,对应5个通道,分别是AWUSER,ARUSER,WUSER,RUSER,BUSER。同样的,协议没有规定这些信号的具体用法,甚至都没规定这些信号的宽度。而且协议也不要求同时实现5个通道的USER信号。可以看出,USER信号的存在感很弱。在一些SoC设计中,可以利用USER信号来传输一些边带信息。要注意的是,如果是不同厂家的IP,在集成时千万要看好了USER信号的具体用法,很有可能不兼容,不能直连。

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/K9cjczMNI3k3vtlk2uIYag

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。