继续码综合这一趴,相关文章回顾:《综合 | 挑战与应对》《综合 | SDC 的读入与检查》《综合 | 设计读入与检查》《综合 | LEF\, QRC\, DEF》《综合 | 概述及 library 检查》。综合需要的输入,除了以上罗列的library, lef, QRC, RTL, SDC, DEF 之外,如果是多电压域设计还需要读入power intent 文件,也就是CPF/UPF, 对于多电压域设计,通常需要执行两次power intent commit, 即执行两次low power cell 插入:

- 第一次在优化前,插入需要的低功耗cell ;

- 第二次在DFT 之后,因为通常插入DFT 会引入额外的跨domain 信号,需要对这些信号补插一次低功耗cell.

此外,如果需要在综合时带仿真波形做动态功耗优化,还需要在优化前读入波形文件,如Saif, FSDB, VCD, TCF 等。

在将所有需要的输入文件读入后,下一步就是对工具行为的控制,通常需要做:

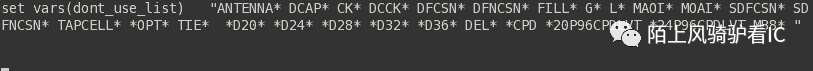

- dont use: 需要将不希望工具优化用到的lib cell 设成dont use. 如CK cell, CK cell 通常有CK buffer, CK inverter, CK MUX, ICG 等,除了ICG 之外其他cell 都需要在综合时禁用,为了保证时钟信号占空比,CK cell 的上升下降时间最好对称,而相同大小的PMOS 管跟NMOS 管,由于PMOS 管的沟道导通电阻更大速度更慢,所以如果要使一个cell 的上升下降时间对称,就需要用更大的PMOS 管,从而CK cell 相较于普通Cell 的面积跟功耗都更大,而在综合时除了插clock gating 之外是不会动clock path 的,data path 对信号上升下降时间的对称性要求又没那么高,所以将CK cell 用在data path 上,纯属瞎子点灯。通常其他需要禁用的cell 还有:Delay cell, size 过大或过小的cell, 特殊功能的cell, 对于congestion 敏感的设计还需要将多pin 的小size cell 禁用掉,如用7个pin X1 的*OAI222D1B* *AOI222D1B*.

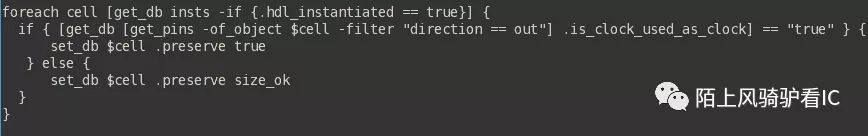

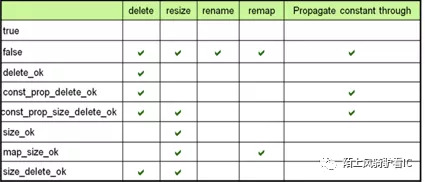

- dont touch: 通常在设计里都会有一些手工例化的std cell 或特殊的寄存器,不期望工具在优化时动到,所谓的动到包括但不限于:由于不驱动primary output 或其他时序逻辑被优化掉、优化成常值、逻辑合并、逻辑等价代换等。对于这类cell, 如果是std cell 可以将其preserve 属性设成dont\_touch 或size\_ok; 如果是未map 的逻辑,需要注意:工具只能对未map 的时序逻辑设preserve 属性,无法dont touch 未map 的组合逻辑。如果设计有特别需求,需要保留某些组合逻辑的原始形态,请直接将其例化成对应的std cell. 如下是在Genus 中,将RTL 中实例化在clock path 的cell 设成preserve true, 即完全保留原样;同时将RTL 中实例化的不在clock path 的cell 设成preserve size\_ok, 即允许工具做size up/down. 在Genus 中preserve 有多个值,可以根据需求灵活设置。

- ungroup, boundary 优化:这部分内容以前写过一篇短文,请查看《综合点聊:ungroup && boundary optimize》。

:BLANK\_LINE:

- 时序逻辑优化:综合工具默认,会将不驱动primary output 或其他时序逻辑的寄存器优化掉、会将功能相似的寄存器合并,会将常值寄存器替换成常值,强烈建议保持工具的默认行为,如果有某些寄存器不能被优化请用preserve 属性控制。在Genus 中可用如下命令得到所有被优化掉的寄存器及被优化掉的原因:

report\_sequential -deleted

- Clock gating: 通常,在RTL 中会例化一些root ICG cell, 其他ICG 都需要在综合时插入,Genus 在syn\_gen 时插入ICG cell. 故需要在优化前设置对应的变量以:选择要用的ICG cell 类型,设置ICG 的min/max fanout, 确定ICG cell TE pin 的连接关系,过约ICG 路径等。关于clock gating 可回顾文章《clock gating | 从ICG cell 在 library 中的定义说起》《clock gating | clock gating 的timing check》《clock gating | Gating 的插入与验证》《clock gating | ODC-based Clock Gating》.

:BLANK\_LINE:

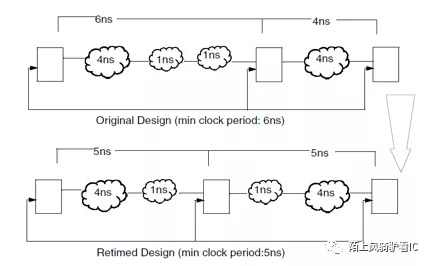

- Retiming: 将需要做retime 的module 的retime 属性打开,工具会在需要时对其做retime, 这部分内容后续会单独写一篇文章阐述。建议在做retime 之前执行一下retime -prepare 检查是否已万事俱备。

- DFT 设置:哪些寄存器要被映射成Scan DFF, 哪些寄存器不能映射成Scan DFF, 是否让工具自动识别shifter 寄存器,如何连接Scan DFF 的SE 和SI 等. DFT 其他设置,通常在DFT insertion 这步做。

:BLANK\_LINE:

- Multibit设置:是否要做Mulitbit merge, 要用哪些Mulitbit cell, 是否可以跨bus 做merge, 是否可以忽略对timing 的影响做merge, 是否带着物理信息做merge, 哪些寄存器不能被merge 等,可回顾文章《论功耗:动态功耗优化》。

:BLANK\_LINE:

- 复位端优化:在老流程中,复位端会留到后端去优化,但是如果做的是phyiscal 综合,强烈建议综合时就优化复位端。在Genus 中要在综合时优化复位信号,需要设置如下变量:

\_timing\_recovery\_arcs true \_

ideal\_seq\_async\_pins false

除以上罗列的设置,还有一些跟设计本身无关的全局变量设置,如information level, 各种naming style, 遇到error 是否停掉,遇到latch/ blackbox 是否停掉,是否优化leakage, 是否优化Dynamic, 是否优化TNS 优化多少等等,对于这些全局变量设置,每家design house flow 一旦稳定,变动的可能性很小,此处就不一一展开。

作者:陌上风骑驴

原文链接:https://mp.weixin.qq.com/s/yrmC2rMXTfkXpbyxwYljcA

微信公众号:

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。