前文《跟老驴一起学PR | Innovus 输入》阐述了 Innovus 所需要的输入数据有哪些,今天来学习如何将这些数据读入Innovus. 以前熟悉的工具,不论是综合、formal 还是STA 读入数据大多都是read_xxx 命令读入,思维定势之前以为Innovus 也是用一坨read_xxx 的命令读入,然而并不是。

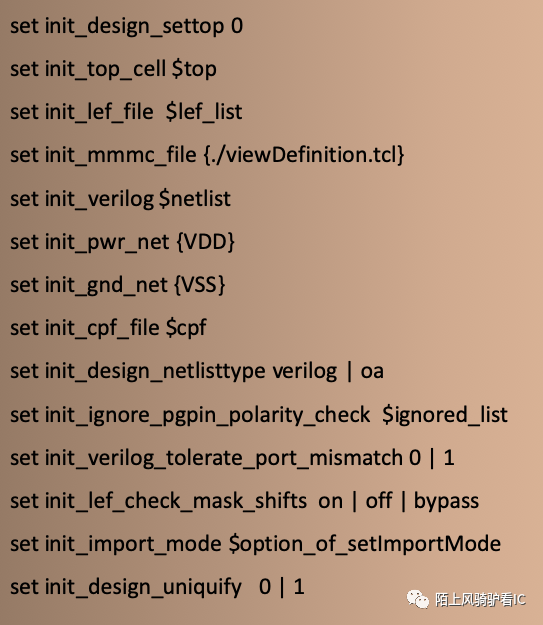

在Innovus 中预定义了一坨init_XXX 的变量,用户需要将对应输入文件指定给对应的变量,然后执行init_design 工具就会将所有文件依次读入,对于verilog netlist 老驴扒拉了几个flow 关键的init 变量有:

- init_design_settop, 这个变量默认值是1,意思是要求客户指定当前设计的top 名字给变量init_top_cell; 如果将该变量设成0, 则让工具自己识别top. 建议,用默认值,用户自己指定top.

- init_lef_file, 将tech-lef + other lefs 指定给这个变量,这里有个问题,如果某个lef file 在init_design 之前没加上,要增量读入该怎么办?在Innovus common ui 中用命令: read_physical -add_lefs XX 可以增量读入lef.

- init_mmmc_file, 指定viewDefinition.tcl, viewDefinition 中的library_set 指定了所有要用的library, rc_corner 指定了对应的QRC file, constraint_mode 指定了SDC 文件。

- init_verilog, 指定网表文件。

- init_pwr_net, 指定 global power nets.

- init_gnd_net, 指定 global ground nets.

- init_cpf_file, 如果是多电压域设计,用于指定CPF 文件,如果power intent 是用1801 描述的,则不能用该变量指定1801 文件,需要用命令read_power_intent -1801 $1801_file 读入,如果在viewDefinition 中用到了power domain 则应该在init_design 之前读入,init_design 之后再执行 commit_power_intent. read_power_intent 这个命令的使用方式跟Genus 一致,在Genus 中多了一步apply_power_intent, 用于将设计跟power domain 绑定,commit_power_intent 用于插入low power cell.

至此,所有输入文件都指定完毕,执行init_design 就会将对应文件读入,init_design 读取文件的顺序还没看,按照逻辑猜测一下读入顺序:library -> tech-lef -> lef -> QRC -> cpf -> netlist -> SDC.

除了上面那一坨指定输入文件的init_XXX 变量之外,还有一坨用于控制输入过程的init_OOO 变量:

- init_design_netlisttype, 用于指定netlist 的format 是verilog 还是OA, 老驴目前只学习verilog 部分,所有OA 相关的都忽略掉。

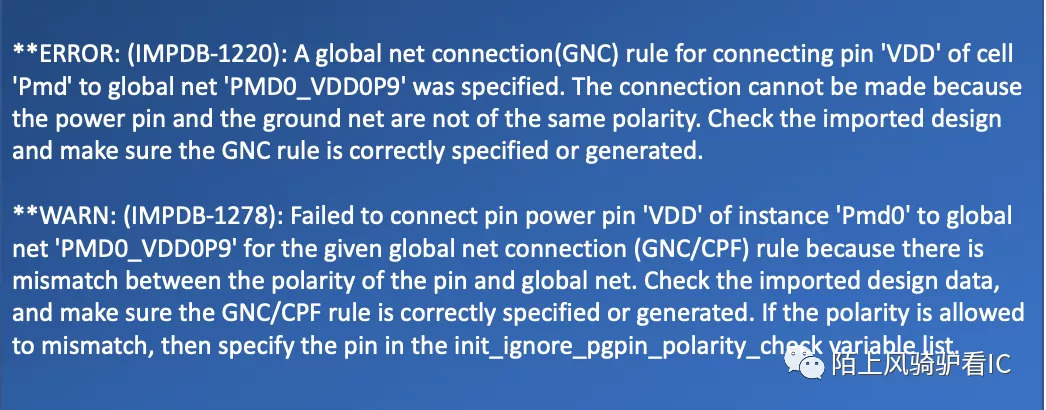

- init_ignore_pgpin_polarity_check, 用于指定一个leaf cell pin name 的list, 告诉工具在globalNetConnect 或在CPF 中connect supply net 时忽略极性检查. 这货好像对1801 flow 没用,正好这周一解了个相关的问题,当时遇到的问题是1801 flow, 在commit_power_intent 时工具报Error: IMPDB-1220 跟WARN: IMPDB-1278, 对于这种问题在Innovus 中先用命令dbGet [dbGet top.nets.name PMD0\_VDD -p].isPwr 来检查工具将对应的supply net 认成了什么。在老驴遇到的case 中,是在1801 中用connect_supply_net 要将一个analog Ground 连到一个analog IP 上,但是在1801 中只定义了supply net 并没有指定该net 用于Ground 所以工具将其认成了Power. 解的办法是在1801 中为其create 一个supply set 并将其指定为ground.

- init_verilog_tolerate_port_mismatch, 这个变量默认值是0, 不能容忍module 定义的port 比实例化时的port 少,如果将其设为1 工具在解析netlist 时如果发现module 的port 比实例化时的port 少,工具会在module 上创建一个port, 老驴以为这个变量在设计脏的时候特别有用。

- init_lef_check_mask_shifts, 用于检查tech-lef 和MACRO sections 中 FIXEDMASK 跟LAYERMASKSHIFT 是否冲突,该变量默认值是off 就是不检查,如果设为on 工具发现冲突会报错并停掉,如果设为bypass 工具发现冲突只报错不停止,其实老驴还不知道FIXEDMASK 跟LAYERMASKSHIFT 在不同工艺中有多重要,先放到这里,万一以后发现重要呢,方便找。

- init_import_mode, 用于指定setImportMode 的option, 如 set init_import_mode {-discardFloatingVNets true -keepEmptyModule true},此处留个问题:是不是默认innovus 会将empty module 删掉?如果是,那综合netlist 中有没有empty module 应该都无所谓吧?如果是,为什么有的后端一定要求把empty module 删掉?

- init_design_uniquify, 控制innovus 解析netlist 时是否做uniquify, 既然innovus 要求netlist 是unique 的,那为毛不把该变量的默认值设为1?

作者:陌上风骑驴

原文链接:https://mp.weixin.qq.com/s/ehF7ze4qXYPLwOJFTanaRQ

微信公众号:

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。