前面的文章我们对DFT做了一个整体介绍,本文我们对DFT的基本概念--缺陷和故障模型做一个全面的介绍,所有的DFT工作都是为了检测这些缺陷的。

01 什么是缺陷和故障模型?

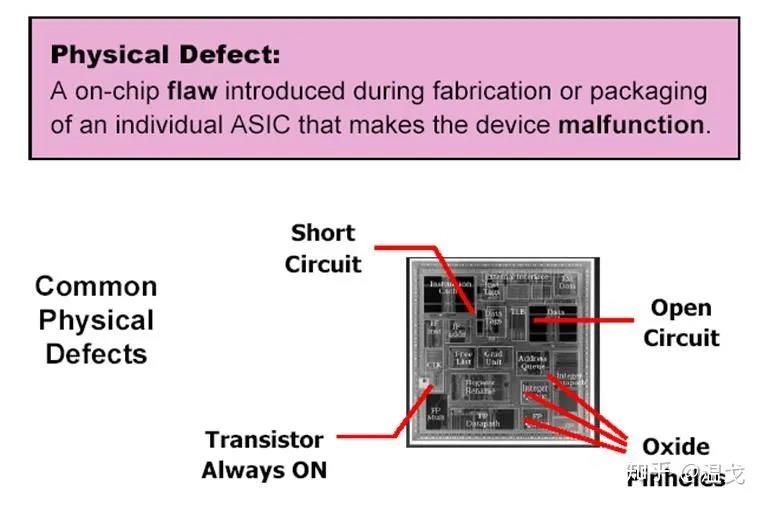

缺陷是指电路因物质方面的原因而改变了其本来的结构,它出现在器件制造或使用阶段,通常是指因制造加工条件的不正常和工艺设计有误等造成电路不正常的物理结构,例如引线的开路、短路等。

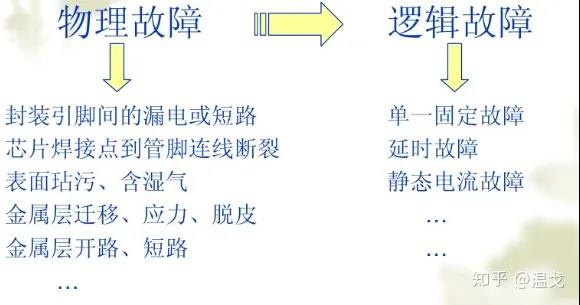

故障是缺陷抽象级的表示,由于引起芯片发生故障的制造缺陷原因多种多样,为了便于分析和判断故障,需要将故障的特征进行抽象和分类,把呈现同样效果的故障归并成同一种故障类型,并使用同一种描述方法,这种故障描述方式称为故障模型。

CMOS 工艺中常见的制造缺陷或曰物理缺陷对地和对电源的短路:

- 对地和对电源的短路

- 由尘埃引起的连线断路

- 金属穿通引(Metal Spike-through)体管源或漏的短路

- 静电击穿

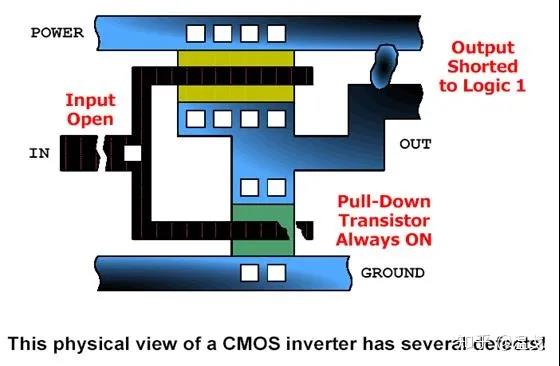

下面用这个CMOS反相器来图示来看一下这几种缺陷:

制造过程中的物理故障便会导致逻辑故障。

02 四种常见的故障模型

固定型故障模型(stuck-at fault model)、时延故障模型(delay fault model)、桥接故障模型(Bridging Fault Model)、固定开路故障模型(Stuck-Open Fault Model)。

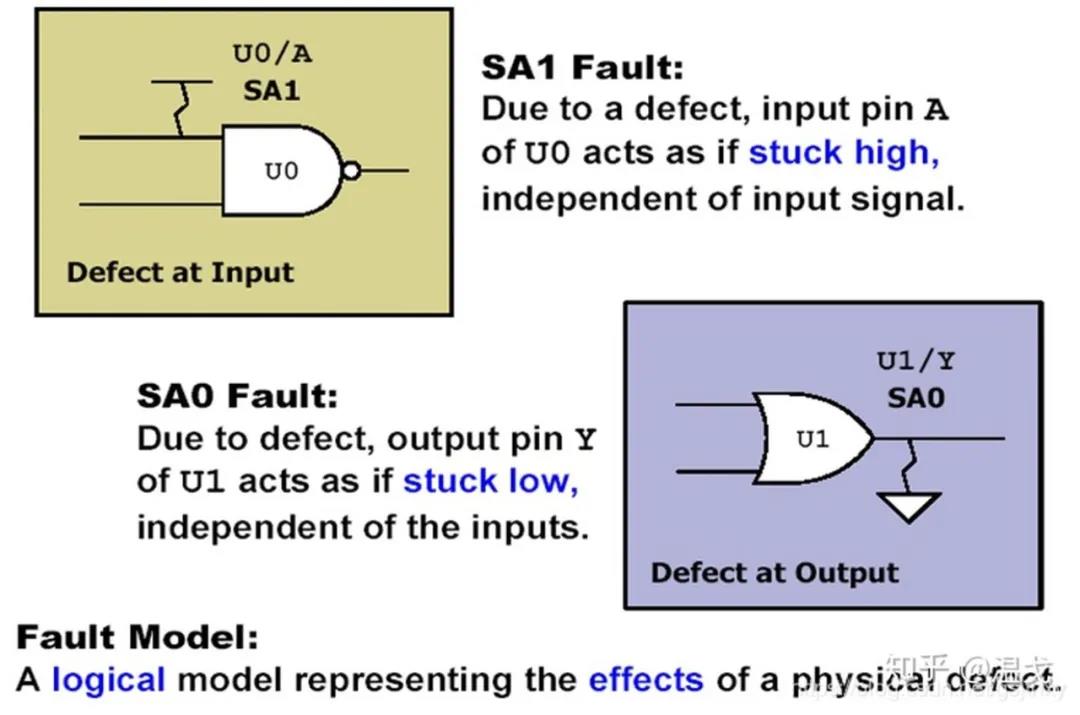

Stuck-at fault model

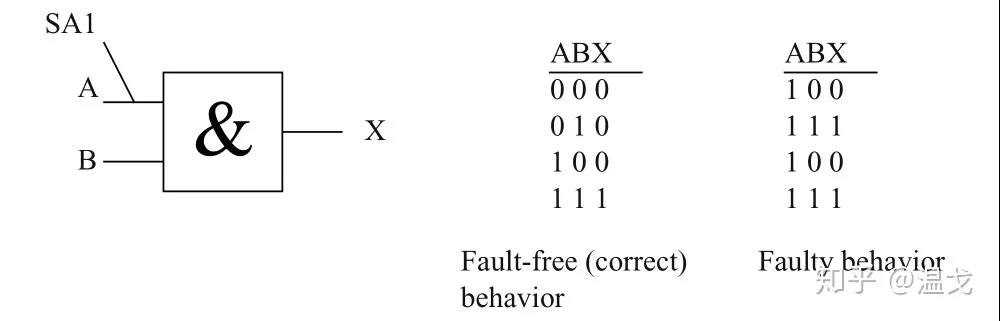

在stuck-at故障模型中,最常见的故障模型是single stuck-at (SSA) 模型。SSA指的是这个故障stuck-at 0或者1.

stuck-at 0的话我们通常考虑发生故障的地方直接接地端。stuck-at 1的话,通常是接到了VDD,也就是供电端。

当我们为SSA故障模型生成测试向量时,我们认为系统中只有一个故障,当同时有多个故障的时候,我们就要用到多故障模型 Multiple stuck-at (MSA)。

举个例子,stack-at 1 的module逻辑真值表如下:

delay fault model

利用延时故障模型我们可以测到一些timing的故障。有些时候一些轻微的timing delay对系统是完全没有影响的,但是长时间的delay就会出现问题,尤其是在一些高速系统中,时钟的频率都很高。

通常延时故障模型分为两种

1)跳变延时故障模型(gate delay faults)

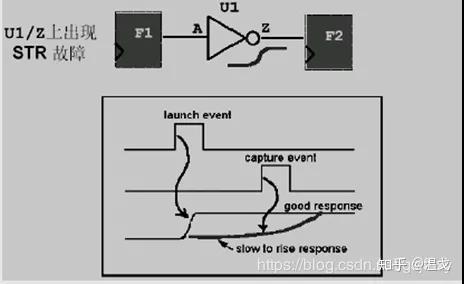

增加了对时域特性的约束,在这种故障测试中,先强制驱动测试点电平到故障值,然后在输入点加上一个跳变的激励,经过给定时间后检测测试点是否跳变至正确值,该模型可以检测出门级电路上的上升跳变过慢(STR,slow -to-rise)或者下降跳变过慢(STF,slow-to-fall)故障。

2)路径延时故障模型

对指定路径上所有组合门电路的跳变延时之和的故障判断。与跳变延时故障模型所不同的是,这里以整个路径上的各个门的管脚与连线节点的连接,取代了跳变延时模型中单个节点作为考察对象。

下面是STR故障的时序示意图:

Bridging Fault Model

桥接故障模型通俗的讲就是两根不应该接到一起的信号线意外的连接到了一起。最常见的桥接故障就是两根信号线短路。

桥接故障可分为三种类型:输入桥接故障,反馈桥接故障,非反馈桥接故障。

好的routing可以有效的减少桥接故障,两根信号线如果routing比较远的话,就不会发生桥接故障,如果距离近,就有可能发生。

Stuck-Open Fault Model

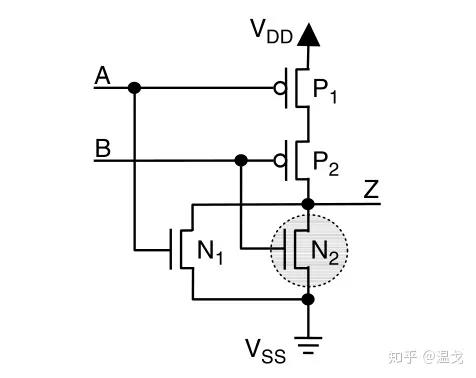

在CMOS 里,有些时候 stuck-at故障模型并不能探测到Stuck-open/Stuck-on的故障。

断路有可能发生在两个门之间的连线,信号线,门电路内部的信号线。

因为这些故障可能发生在门电路内部,而一个逻辑门有可能是由多个晶体管搭建起来的,所以我们用晶体管级的故障模型。

为了说明这一点,我来举个例子:

下图是一个NOR门,正常情况下,当我们在AB端输入01时,Z端会得到一个逻辑0.

但如果N2点是stuck-open,此时Z端和VSS形成开路,P2和N1的值此时也无法传到,Z端会保持之前的状态,0或者1.

除了以上四种故障模型外,还有一种基于电流的故障模型,指的是电路中的缺陷可能会导致过大的漏电流。

尽管有些人认为不导致逻辑错误的缺陷不能被称为故障,但这些缺陷却显示了出现可靠性方面的问题。

pseudo-stuck-at 故障模型:主要建立在SA 故障模型上:在单纯的SA模型中,观察代表逻辑值1 或者0 的电压值;而在pseudo-stuck-at 故障模型中,则是先将故障效应加到指定点,然后观察电源对整个芯片输出的电流大小。

这种故障模型是基于在CMOS逻辑中,非翻转状态的门只消耗静态或者二极管反向电流,故静态情况下芯片的漏电流是非常小的。而任何导通的桥接,短路和断路故障都将导致静态电流上升一个数量级以上。

以上便是对故障模型的全面介绍,了解故障模型是DFT工作必备的基础概念,也是为后面做ATPG,打下坚实的基础,可以说,所有的DFT工作都是为了发现这些故障,筛选出有问题的芯片。

作者:温戈

原文链接:https://mp.weixin.qq.com/s/XGyC2XpggUZ4XIQ05t2p2w

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。