导语

通过对比国内外半导体与 EDA 行业发展历史与现状,我们认为在国内半导体设计 /制造等全链条加速发展的背景下,EDA 在国内半导体产业的渗透率有望从 0.6%提升至 2.6%,产值望超 300 亿元,其中国产化比例有望大幅提升。

一、创新之处

1、本报告系统梳理了 EDA 企业崛起规律,提出核心产品能力及方案完整度、IP 能力 储备、产业链协同是龙头公司三大壁垒,其背后是持续的政策/人才/资金支持。

2、通过对比国内外半导体与 EDA 行业发展历史与现状,我们认为在国内半导体设计 /制造等全链条加速发展的背景下,EDA 在国内半导体产业的渗透率有望从 0.6%提升至 2.6%,产值望超 300 亿元,其中国产化比例有望大幅提升。

3、本报告梳理了海外与国内产业的生态格局,不同厂家在不同功能点上竞争优劣差 异,为未来研究跟踪公司产品竞争力指明了方向。

二、 EDA:半导体产业皇冠上的明珠

EDA 概述:芯片设计必备工具,绘制半导体国产化新蓝图

分类:EDA 属工业软件类研发设计软件。工业软件是在工业领域应用的软件,包括系 统软件、编程语言、应用软件和中间件等。按照产品形态、用途和特点的不同,工业软件 市场可进一步细分为研发设计软件、生产控制软件、信息管理软件以及嵌入式软件。在多 类工业软件中,研发设计软件位于“卡脖子”环节,价值高,研发难度大。研发设计软件 对人才素质要求高、产品可靠性需求强、行业 know how 知识需求大。

概念:EDA 软件面向电子设计领域,提供电路设计、布线、验证、仿真等功能。EDA 是电子设计自动化软件,其前身是计算机辅助设计 CAD 和计算机辅助工程 CAE。CAD 的 研发起源于 20 世纪 60 年代,旨在通过计算机及相关设备辅助设计人员工作。电子设计领 域中,设计师起初通过 CAD 软件进行 IC 版图设计、PCB 布线布局等。随着电路逐渐复杂, 仿真需求日渐凸显,CAE 通过增加模拟、仿真、时序分析等功能辅助设计者在设计阶段预 知产品功能。EDA 软件面向电子设计领域的超大规模集成电路(VLSI),进一步完善电路 设计、布线、验证、仿真等功能,提供芯片设计解决方案。

功能:EDA 帮助设计师实现自抽象到具体的全流程设计,同时提供多层级仿真验证, 确保功能可靠。

1) 架构设计:根据客户需求提出具体设计架构,划分模块功能;

2) 设计实现:通过硬件描述语言(VHDL、Verilog HDL 等)对模块功能进行描述, 实现 RTL 级代码;

3) 逻辑综合:将 HDL 代码转换为门级网表 netlist;

4) DFT 实现:为后续测试进行测试电路实现;

5) 物理设计:为实际布局布线。

与芯片设计不同阶段对应,EDA 软件提供不同层级的验证、仿真等功能,包括设计规 则、布局布线、版图检查等。根据 Synopsys 数据,设计流程中仿真验证步骤占约 70%时 间。以 7/5nm 以下工艺的设计规则检查 DRC(Design Rule Check)检测为例,DRC 检 测需数天完成一次迭代,其中包括 10 万次 DRC 计算操作和 1 万条复杂规则。仿真验证功 能至关重要,仿真验证在芯片设计阶段估计芯片性能,确保半导体芯片成品满足用户需求。

EDA 特点:软件质量、生态建设构筑壁垒,知识产权拓展产品边界

EDA 软件的三大评估维度是可靠性、及时性和功能模块的丰富性,软件质量、生态 建设、半导体知识产权分别体现了可靠性、及时性、丰富性,构筑 EDA 壁垒。可靠性指 的是基于 EDA 软件进行的芯片设计、模拟仿真等步骤是否能帮助芯片设计者在设计阶段 解决芯片设计问题,预知芯片表现。及时性指的是 EDA 软件能否及时更新下游代工的最 新工艺,从而保证芯片设计人员能够根据下游代工厂的生产工艺进行布局布线。丰富性指 的是 EDA 厂商提供的半导体 IP 的丰富程度能否满足芯片设计师的需求。我们认为,软件 质量的高低决定了软件可靠性,生态建设的程度决定了 EDA 软件工艺更新的及时性,半 导体 IP 的数量和质量决定了 EDA 软件的丰富性。

从软件质量层面看,高素质人才、用于研发并购的资金是决定软件质量的重要因素。

高素质人才:EDA 软件开发难度大,需要具备高素质复合型人才。根据 Synopsys 公 司官网,EDA 工具的复杂性和开发难度对于人才质量需求较高,掌握数学、物理、计算机、 芯片设计等多行业知识的复合型人才备受青睐。根据 Synopsys 官网资料,培养一名成熟 的 EDA 研发人员往往需要十年时间,期间经历高校培养、企业实习、项目实践、不断精 进等。EDA 软件的发展离不开高素质人才,EDA 厂商是否有足够的高素质研发人员是衡 量 EDA 企业竞争力的重要标准之一,芯片设计产业的发展决定于高校的人才梯队建设。

用于研发、并购的资金:并购成就 EDA 巨头,研发维持龙头地位。国际 EDA 龙头厂 商 Synopsys 和 Cadence 2020 年营收分别为 36.9、26.8 亿美元,研发费率分别为 35%、 39%,近年来龙头企业持续进行高研发支出。EDA 厂商通常难以以一己之力构建全流程 EDA 软件,国际 EDA 三巨头的发展过程中共并购 200 余次。从零打造具有全流程解决方 案的 EDA 软件厂商,其成功的必要条件之一为用于研发和并购的资金充裕。由于半导体 产业特点为投资的回报周期较长,因此具有国家或者相关产业基金支持的厂商更有底气进 行高研发投入和大规模并购。

从生态建设层面看,产业链上下游的双向迭代是生态建设重要方式,帮助 EDA 软件 提升工艺更新的及时性。与下游代工厂的深度结合有助于 EDA 厂商加快软件革新。芯片 设计厂商根据下游代工厂提供的 PDK(Process Design Kit)工具进行布局设计,复杂芯 片的流片成本以百万元计价,时间以月为单位,稳定的 EDA 软件可保证流片成功率。和 下游代工厂进行深入绑定的 EDA 厂商生态体系完善,有能力提供更加稳定和及时的工艺 革新,为芯片设计公司提供及时的工艺制程。

从知识产权层面看,半导体 IP 提供成熟的功能模块,帮助芯片设计人员提升芯片设 计效率,拓宽 EDA 产品边界。为了简化芯片设计难度,EDA 厂商将固定的功能模块化为 半导体 IP(SIP, Semiconductor Intellectual Property),降低芯片设计难度,半导体下游 新场景如 5G 等催发面向 EDA 软件的新需求,促进 EDA 软件提供面向新场景的相关功能 实现。相关产业发展对半导体需求增加,下游新场景催生面向新业务 SIP 模块,推动 EDA 软件市场规模持续增长。芯片设计公司根据需求进行芯片设计,成熟的功能可通过采购 SIP 实现高效、可靠的芯片设计。以 Synopsys 为例,公司在接口、存储器、处理器、安全性 等多领域具有丰富的 SIP 经验积累。

EDA 的历史与未来:产品功能由点及面,四大驱动力引领未来

EDA 软件历史进程:EDA 软件的发展历经三个大阶段,第一阶段是 CAD 阶段,第 二阶段是 CAED 阶段,第三阶段是 EDA 系统设计阶段,第四阶段是现代化 EDA 阶段。

第一阶段:计算机辅助设计(CAD)阶段。上世纪七八十年代,由于芯片复杂度低, 芯片设计人员可以通过手工操作完成电路图的输入、布局和布线。七十年代中期,可编程 逻辑设计技术的出现使得芯片设计自动化成为可能,交互图形编辑、晶体管版图设计、规 则检查等功能提升了芯片设计的自动化程度。

第二阶段:计算机辅助工程(CAE)阶段。20 世纪 80 年代,EDA 技术进入发展和完 善阶段,推出的 EDA 工具以逻辑模拟、定时分析、故障分析、自动布局和布线为核心, 重点解决功能检测等问题,利用这些工具,设计师能在产品制作之前预知产品功能和性能。80 年代后期,EDA 工具已可以进行设计描述、综合与优化和设计结果验证。

同时期,EDA 商业化雏形显现。1980 年,Mead, C.和 Conway, L.出版《超大规模集 成电路系统导论》,论文提出使用编程语言进行芯片设计,从而启发了 VHDL 和 Verilog 等 工具的诞生。使用编程语言进行芯片设计进一步降低了芯片设计师工作的复杂程度,是 EDA 商业化中的重要推动力。

第三阶段:电子系统设计自动化(EDA)阶段。二十世纪九十年代,随着芯片设计流程的标准化发展以及集成电路设计方法论的完善,EDA 芯片设计工具百花齐放:可编程逻 辑阵列、标准单元库、全/半定制设计、专用集成电路设计等。通过抽象封装,芯片设计师 从底层的布局布线的繁杂工作中解脱出来,根据芯片应用需求通过自顶向下,自抽象到具 象的设计方法成为主流。

第四阶段:现代 EDA 技术。进入 21 世纪后,EDA 工具快速发展,并已贯穿集成电 路设计、制造、封装、测试的全部环节。在仿真验证和设计两个层面支持标准硬件语言的 EDA 软件工具功能更加强大,更大规模的可编程逻辑器件不断推出,系统级、行为级硬件 描述语言趋于更加高效和简单,EDA 工具的发展加速了集成电路产业的技术革新。

四大因素驱动 EDA 软件未来发展:摩尔定律、设计方法学创新、AI 赋能、EDA 上云。随着集成电路的发展,芯片的复杂性、集成度日益增加,EDA 工具有效保证芯片设计中不 同层次设计的可靠性,提升设计效率,从而缩短设计周期。

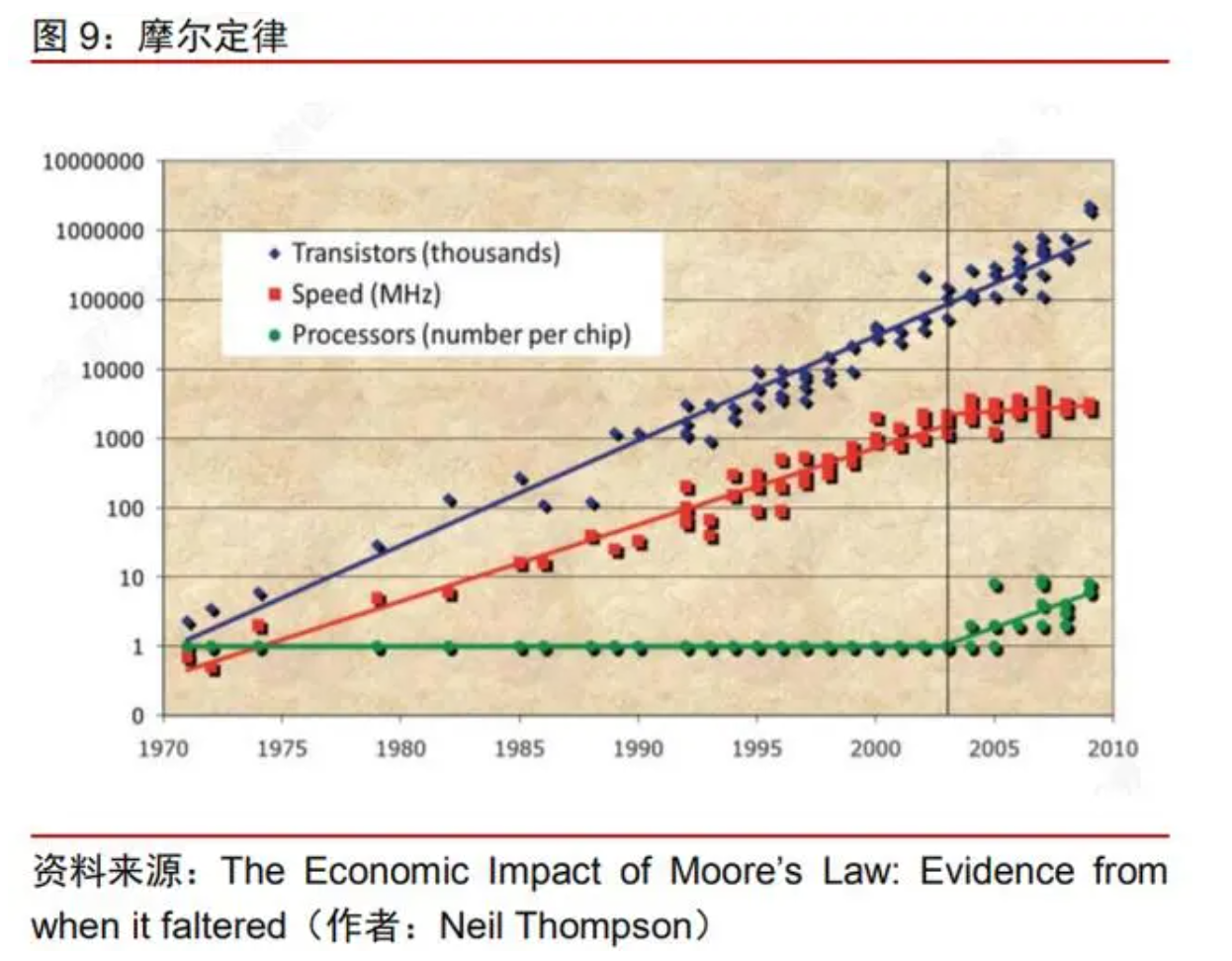

1)摩尔定律:硬件工艺革新趋缓,EDA 软件重要性凸显,引领摩尔定律实现。英特 尔公司创始人戈登摩尔于 1975 年在 IEEE 国际电子组件大会上提交论文,预言每两年半 导体芯片上集成的晶体管和电子数量翻一倍。半导体工艺制造制程进步使得芯片每单位面 积可布置更多的晶体管,目前常用的集成电路通常集成数十亿晶体管。半导体制造厂商、 芯片设计厂商从硬件、软件两方面推动摩尔定律预言实现。受到研发成本高、量子效应等 因素影响,半导体制造厂商的生产工艺革新趋缓,对摩尔定律驱动力减弱,从而导致 EDA 软件重要性愈发凸显。

以 Intel 研发模式为例,半导体制造工艺、芯片架构设计合力驱动芯片性能提升。根据 Intel 官网资料,为实现摩尔定律预言,英特尔采取 Tick-Tock 的研发模式,在研发的 Tick 周期以芯片制造工艺的进步实现摩尔定律预言,在 Tock 周期以芯片架构的革新实现摩尔 定律预言。受研发成本高、量子效应等影响,制程工艺革新趋缓,硬件革新出现瓶颈,因 此 EDA 软件重要性凸显,帮助实现芯片架构快速升级。

我们认为,制程革新的趋缓主要有研发成本、量子效应两点因素,对应凸显了 EDA 软件的价值:

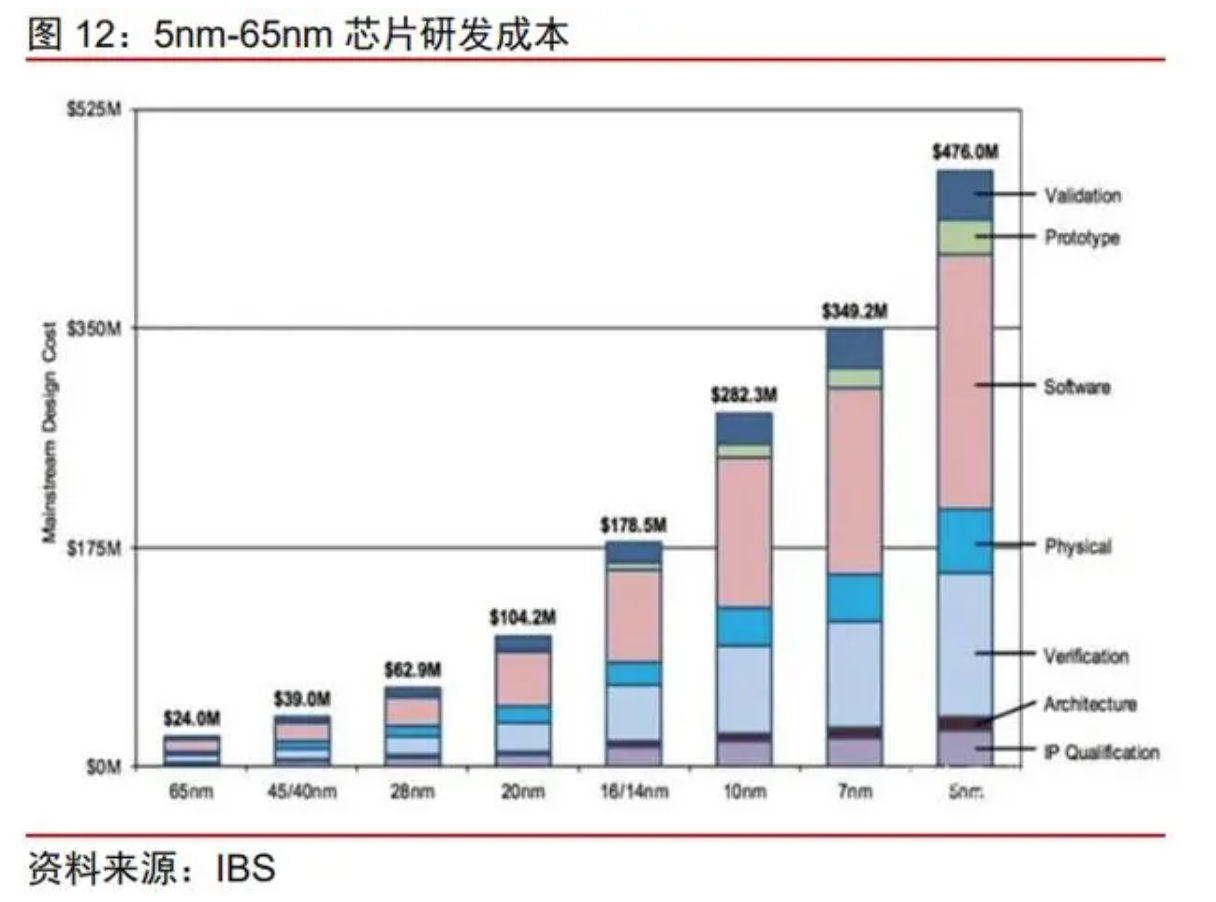

a. 研发成本因素:伴随芯片制程的提升,研发投入加速增长,由于硬件成本较高,因 此 EDA 软件的改进重要性凸显,帮助芯片架构升级。根据市场研究机构 IBS 数据,5nm 制程芯片研发费用为 4.76 亿美元。3nm 制程芯片研发费用为 5-15 亿美元;工艺开发成本 为 40-50 亿美元;晶圆厂运营成本为 150-200 亿美元。目前具备世界先进制程研发能力的 厂商仅有台积电、三星、英特尔等。2018 年,因高昂的研发成本,当时排名世界第二的 代工厂格罗方德放弃 7nm 制程的研发。中芯国际能够量产 14nm 制程芯片,12nm、7nm 制程芯片处于研发过程中。低制程芯片研发成本加速提升,因此,EDA 软件的改进对芯片 性能的提升显得尤为重要,EDA 软件革新可进一步帮助改进芯片架构。

b. 量子效应因素:量子效应阻碍工艺革新,EDA 模拟仿真可将量子效应带来的影响 考虑在内,在设计环节提供仿真验证方式。根据 Semiconductor Engineering 资料,量子 效应在 5nm 制造工艺中的相关影响可以通过代工厂的限制性设计规则在芯片设计阶段规 避。但是当制程进入 3nm 及以下,芯片设计者在芯片设计阶段就需要考虑到量子效应所带 来的影响。对纳米级半导体设计进行模拟仿真是 EDA 软件的新赛道,也是半导体制程能 否进一步降低的关键。

面对工艺制程更新趋缓,三个不同维度的演进路径有望进一步推动摩尔定律预言发展。延续摩尔定律指引:延续摩尔定律旨在单芯片上集成更多的晶体管,进一步提升芯片性能;扩展摩尔定律指引:扩展摩尔定律旨在将逻辑、模拟、存储等功能的模块叠加在同意芯片 上,对 EDA 软件的复杂设计功能提出更高的要求;超越摩尔定律指引:超越摩尔定律则 是基于新工艺、材料、器件等进行创新,对 EDA 工具在新器件的模拟仿真提出更高要求。

2)设计方法学创新:EDA 工具助力芯片设计研发成本降低。2013 年,美国加州大学圣地亚哥分校 Andrew Kahng 教授测算,2011 年设计一款面向消费端市场的芯片成本为 四千万美元,如果 EDA 技术自 1993 年开始止步不前,那么这款芯片的设计成本将为 77 亿美元。可重复利用 IP 模块,异构芯片等驱动 EDA 技术进步。EDA 软件与芯片设计技术 共同进步,提升芯片设计效率,降低研发成本。

3)AI 赋能:通过学习芯片设计师的设计经验,进一步提升芯片设计效率。从 RTL 级 别编程至 GDSII 级别文件生成需要芯片设计师数月的时间完成设计、仿真、综合、模拟等 环节,本世纪早期,EDA 公司就在尝试使用机器学习算法进行辅助。随着芯片设计相关数 据的积累,计算机计算能力的提升,芯片设计复杂性增加以及人工智能技术的进展等因素 的驱动,人工智能在芯片设计领域的重要性初步显现,EDA 软件中的规律性、调试性的性 能有望在 AI 的支持下自动化实现,从而提高 EDA 软件易用性,降低芯片设计成本,提高 芯片设计效率。国家级、企业级的项目着眼 AI 赋能 EDA 软件。

案例一:美国国防部高级研究计划局(DARPA)在 2017 年提出“电子复兴计划(ERI)”, 其中电子设备智能设计(IDEA)项目对于 AI 赋能 EDA 工具进行设想,其目标为“设计工 具在版图设计中无人干预”,即将芯片设计师的设计经验固化为机器学习模型的输出目标, 构建统一的版图生成器,从而实现版图设计的自动化、智能化,并进一步提升设计效率。

案例二:Synopsys 公司对于 AI 的布局主要涉及 AI 驱动的设计应用程序 DSO.ai 解决 方案;机器学习增强型设计工具;AI 芯片设计解决方案。其 AI 解决方案的客户主要有三 星电子、英国人工智能芯片制造商 Graphcore、萨瑞电子等。

案例三:谷歌公司刊发在《自然》杂志 2021 年 6 月刊上的文章表明,AI 在数字电路 布局布线领域取得一定进展,使用 AI 设计的电路布局有望应用在谷歌公司下一代 TPU 产 品上。

4)EDA 上云:云化 EDA 具备计算能力强、资本支出友好等多项优势。云化 EDA 主 要是通过云技术将 EDA 软件部署在云端,构建 EDA 云平台,主要优势有如下四点:

云端服务器具有较强的计算能力,芯片设计企业如需设计复杂芯片,具有强大计 算能力的云服务器是芯片设计的底层保障;

云端服务器无需前期大额费用,芯片设计企业无需在芯片设计前购置本地软硬件 设施,可根据企业需求灵活使用计算资源;

云端服务器的访问不受地理环境约束,芯片设计企业的设计师们可以随时随地对 于云端软件进行访问;

云端服务器提供 EDA 软件配套环境,便于 EDA 厂商向高校等机构推广自身 EDA 产品,进行人才梯队建设。

三、全球格局:巨头三足鼎立,产品与生态体现核心能力

市场规模:百亿美金“卡脖子”赛道,撬动四十倍半导体产业链

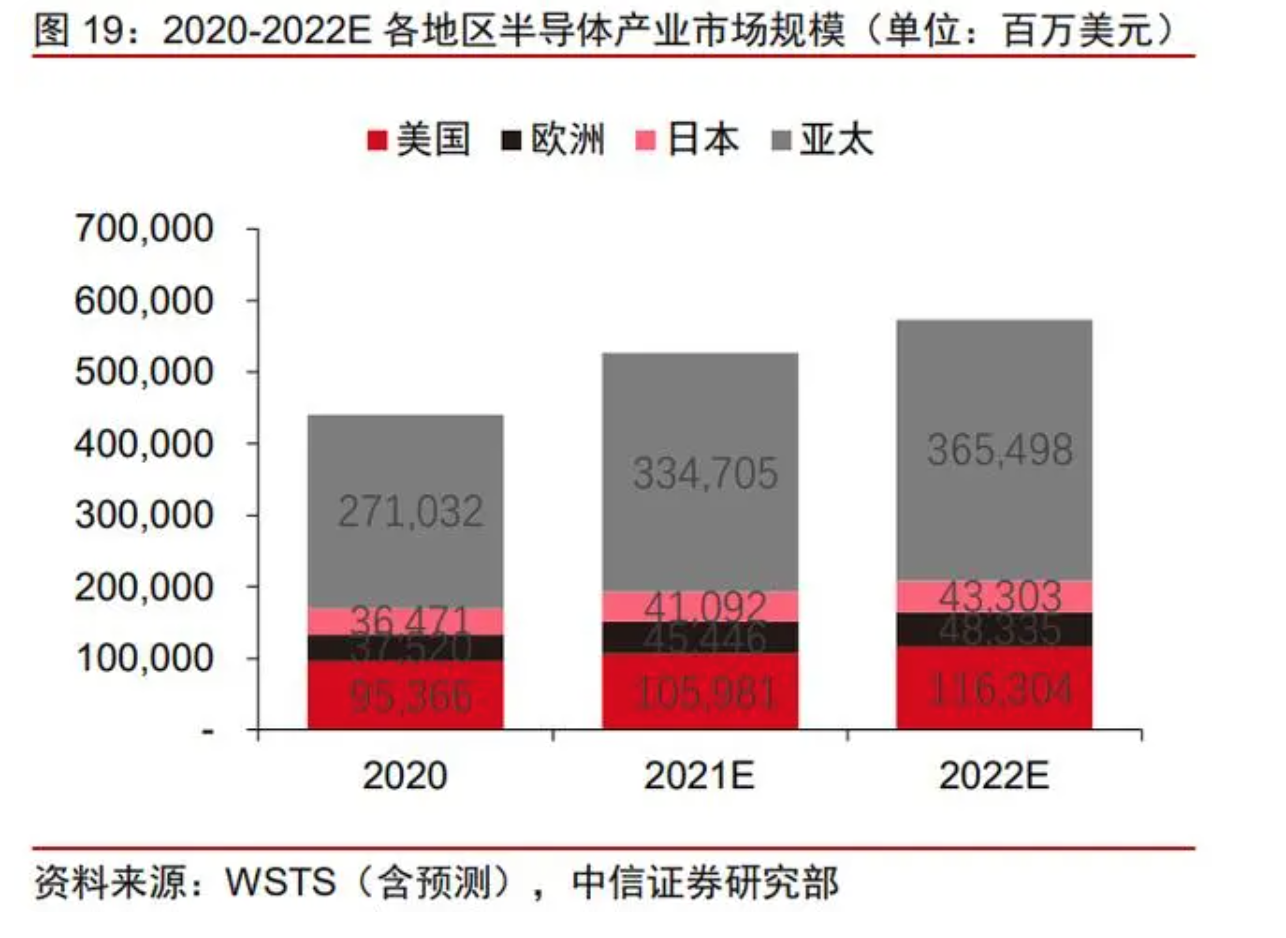

半导体产业:四千亿美元规模增长稳健,亚太地区市占率稳居第一,半导体产业方兴未艾。根据WSTS世界半导体贸易统计协会数据,2020年世界半导体领域市场规模达 4404 亿美元,2014-2020 年 CAGR 为 4.62%。其中集成电路 2020 年市场规模达 3612 亿美元, 占半导体产业规模 82%,2014-2020 年 CAGR 为 4.50%。根据 WSTS 预测,全球半导体 产业在 2021、2022 年增速将分别达到 19.7%、8.8%,对应市场规模 5270、5730 亿美元, 半导体产业发展方兴未艾。

根据地区划分:亚太地区增速引领。根据 WSTS 预测,2021 年,半导体产业市场规 模各地区增速中,亚太地区 23.5%、欧洲 21.1%、日本 12.7%、美国 11.1%,半导体产业 链第三次转移促成亚太增速引领。

根据产品划分:存储器等新兴领域有望快速发展。2021 年,半导体产业市场规模增 速中,存储器将达到 31.7%、传感器 22.4%、模拟电路 21.7%、光电器件 9.8%、Mos Micro (MPU、MCU 等)8.1%。

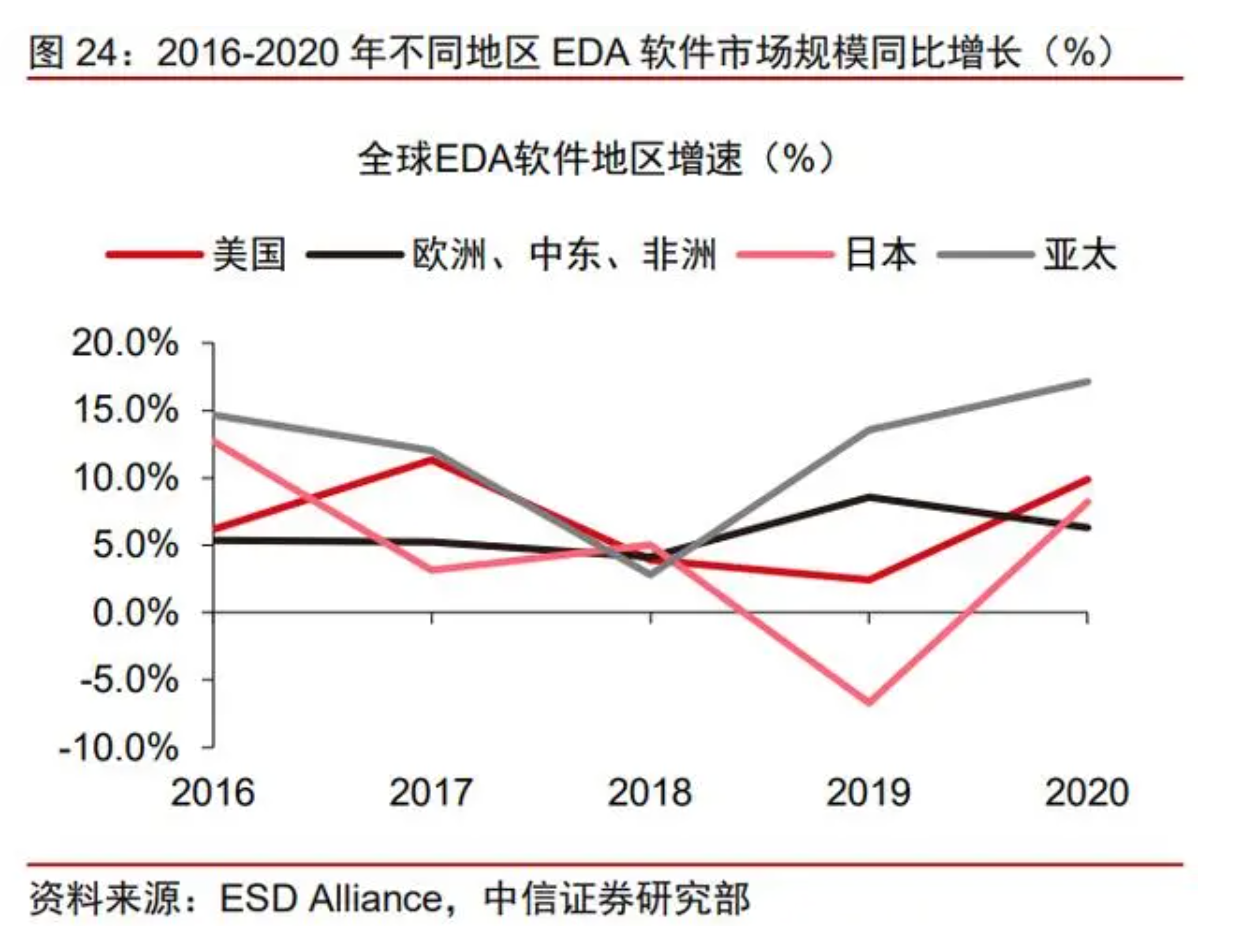

EDA 软件:EDA 软件处半导体产业链最上游,2020 年全球市场规模达 115 亿美元。 根据 ESD Alliance(Electronic System Design Alliance)电子系统设计联盟数据,2020 年全球 EDA 市场规模 115 亿美元,同比增长 11.6%,2015 年至 2020 年 CAGR 为 8%。

根据地区划分:美国、亚太地区占比近八成,亚太地区增速引领,规模有望超美国成 全球第一。2020 年美国、欧洲中东非洲、日本、亚太地区营收分别为 48.8、16.0、9.7、 40.2 亿美元,占比分别为 43%、14%、8%、35%,分别同比增长 9.9%、6.3%、8.2%、 17.1%,2015-2020 年 CAGR 分别为 6.7%、5.9%、4.3%、11.9%。亚太地区 EDA 软件 市场规模持续高增长。

根据产品划分:CAE/SIP/IC 三者占比超八成,SIP 保持高增速成主驱动力。半导体产 业链上游 EDA 软件根据类型可分为计算机辅助工程 CAE、半导体知识产权 SIP、IC 物理 设计、印刷线路板 PCB 和多芯片模块 MCM 以及其他相关服务。2020 年 SIP 规模 40.4 亿美元,占比 35%,增速 17.1%,引领 EDA 软件行业增长。

EDA 软件之于半导体产业链:百亿美金卡脖子赛道,撬动四十倍半导体产业链。根 据 ESD Alliance 电子系统设计联盟数据,2020 年 EDA 软件产业规模达 115 亿美元,结合 WSTS 测算的半导体产业 2020 年市场规模 4404 亿美元,EDA 软件占半导体产业规模 2.6%。EDA 软件位处半导体产业链最上游,EDA 软件是下游半导体产业链的“卡脖子” 环节,地位不言而喻。

主要参与者:三巨头市占率超六成,需求释放促进龙头高增

全球市场中,Synopsys、Cadence 和 Mentor Graphics 呈三足鼎立之势,对 EDA 软件具备深度理解,也与下游电子设计与制造厂商绑定较深。

Synopsys:成立于 1986 年,创始团队曾就职于通用电气的微电子中心,创始人 Aart de Geus 博士的导师是加州大学伯克利分校 SPICE 模拟程序之父 Rohrer 教授,公司初期公司具备逻辑综合技术,融资来自于下游企业通用电气和哈里斯半导体公司。Synopsys 公司目前是 EDA 软件工具厂商,并提供技术先进的集成电路设计与验证平台,半导体知 识产权和设计服务。

Cadence:由 SDA 公司和 ECAD 公司在 1988 年合并而成,其中 SDA 公司成立于 1983 年,创始团队为加州大学伯克利分校的学生和贝尔实验室的研究员,融资来自于下游企业 (爱立信、通用电气、哈里斯半导体公司、美国国家半导体公司各 100 万美元)以及风险 投资公司(共计 100 万美元)。SDA 公司尽管初期遇到困难,但是凭借其合伙模式最终实 现持续盈利。Cadence 公司目前提供 EDA 软件、仿真硬件和知识产权等。

Mentor Graphics:成立于 1981 年,创始团队来自于美国俄勒冈州电子制造公司 Tektronix,创始团队同样具有半导体制造产业背景。2017 年 Mentor 被德国西门子公司收 购成为其 EDA 部门。

全球 EDA 行业按照营业收入规模大体可分为三个梯队。参与者根据营收分类,第一 梯队为 Synopsys、Cadence 和 Mentor 公司,年营收大于 10 亿美元,在 EDA 行业具有 显著领先优势;第二梯队为 Ansys 等公司,年营收在五千万至四亿美元之间,具有部分领 域的全流程工具从而具备局部领先优势;第三梯队包含国微集团、概伦电子等公司,年营 收小于三千万美元,主营业务为聚焦于某些特定领域的点工具,在产品矩阵的集成度、完 整度等方面与前两梯队具有一定差距。

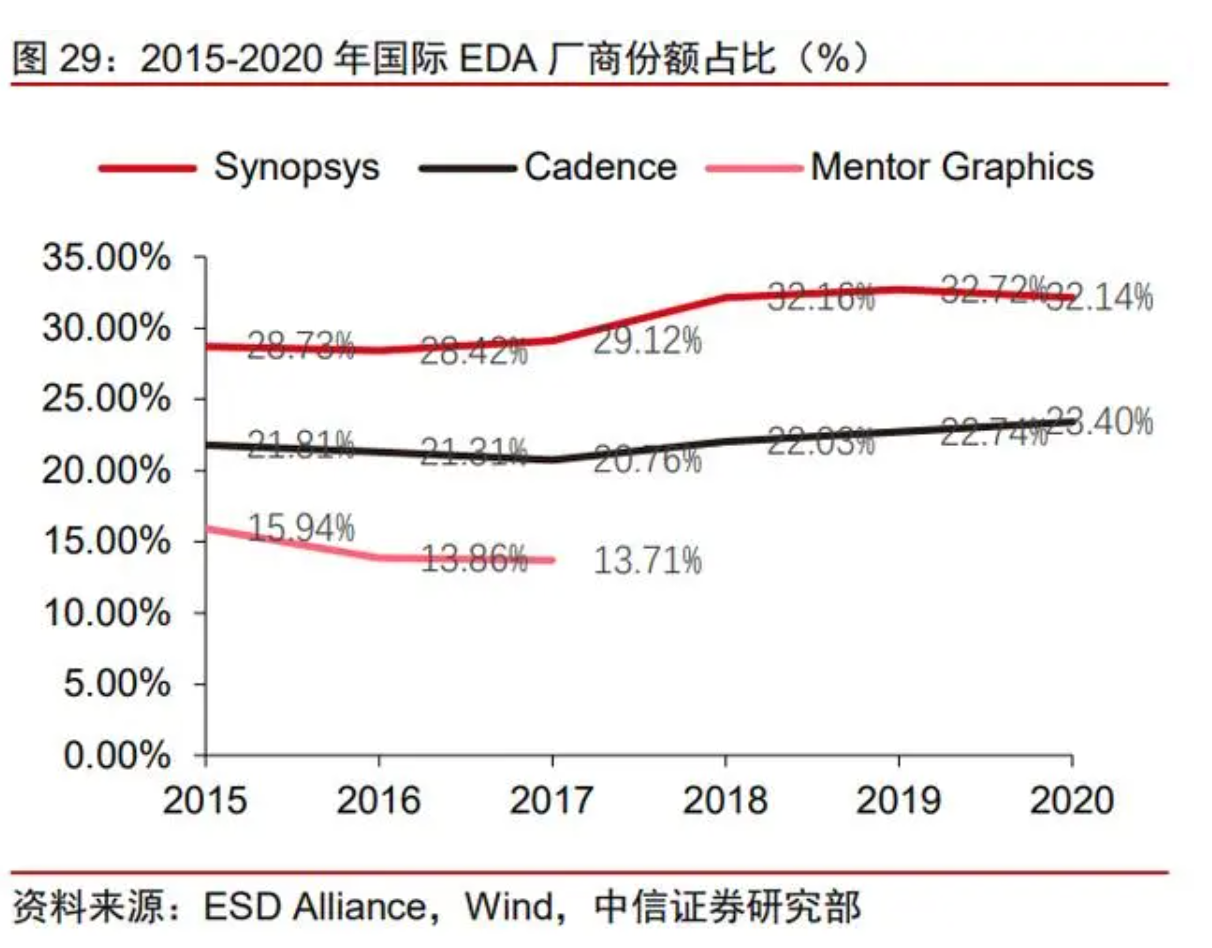

Synopsys、Cadence和 Mentor Graphics 总营收占全球 EDA软件市场份额超 60%。根据 ESD Alliance 数据,2020 年 EDA 全球市场规模 114.67 亿美元。根据营业收入,我 们测算 Synopsys、Cadence 公司市场份额分别为 32.14%、23.40%。Mentor Graphics 2017 年被西门子公司收购后,营收不单独披露。2017 年,根据 ESD Alliance 数据,全球 EDA 软件规模为 93.58 亿美元,经我们测算得 Synopsys、Cadence 和 Mentor Graphics 的市 场份额分别为 29.12%、20.76%、13.71%,三者共计 63.59%。2018-2020 年 Synopsys、Cadence 公司毛利率为 76%以上及 87%以上。

营收增速:巨头增速高于行业,集中度提升,龙头优势地位加深。Synopsys、Cadence 公司 2020 年营收分别为 36.9、26.8 亿美元,分别同比增长 9.66%、14.83%。Synopsys、 Cadence 2015-2020 年营收 CAGR 分别为 10.4%、9.5%,营收增速均高于 EDA 软件平 均 8%的 CAGR。根据 Synopsys 公司 2020 年报披露,公司营收同比增长 9.66%主要由 SIP 的 license 授权和服务营收增加所致。根据 Cadence 公司 2020 年报,公司营收同比 增长 14.83%主要由软件和 SIP 收入增长所致。

EDA 巨头全球布局,美国营收占比近半,市场机会广阔。2020 年 Synopsys 公司营 收根据区域划分,美国营收贡献 48.1%,占比近半,欧洲、中国、韩国分别占比 10.5%、 11.4%和 10.6%;2020 年 Cadence 公司营收根据区域划分,美国营收贡献占比 40.9%, 中国、除中国外其他亚洲地区、欧洲中东非洲分别占 15.2%、18.2%和 17.5%。芯片设计 领域相关产业需求强劲,促进 EDA 软件需求高速增长。

龙头崛起规律 1:重视拳头产品打磨,加码布局半导体知识产权

EDA 厂商各有拳头产品,依托拳头产品构建全流程解决方案。Synopsys 公司主攻数 字芯片设计、静态时序验证确认以及 SIP 提供;Cadence 公司主攻模拟、数模混合平台, 数字后端、DDR4 IP 等;Mentor 主攻后端验证、可测试性设计、光学临近修正等,各家 分别有主打的拳头产品,同时也有配套的全流程工具。芯片设计公司可根据其设计的芯片 类型采购对应 EDA 厂商的全流程工具。

资金投入、研发人才是促成 EDA 厂商拳头产品的关键因素。EDA 企业的资金需求主 要来源于研发需求和并购需求,人才需求主要来源于对综合型专业人才的需求。

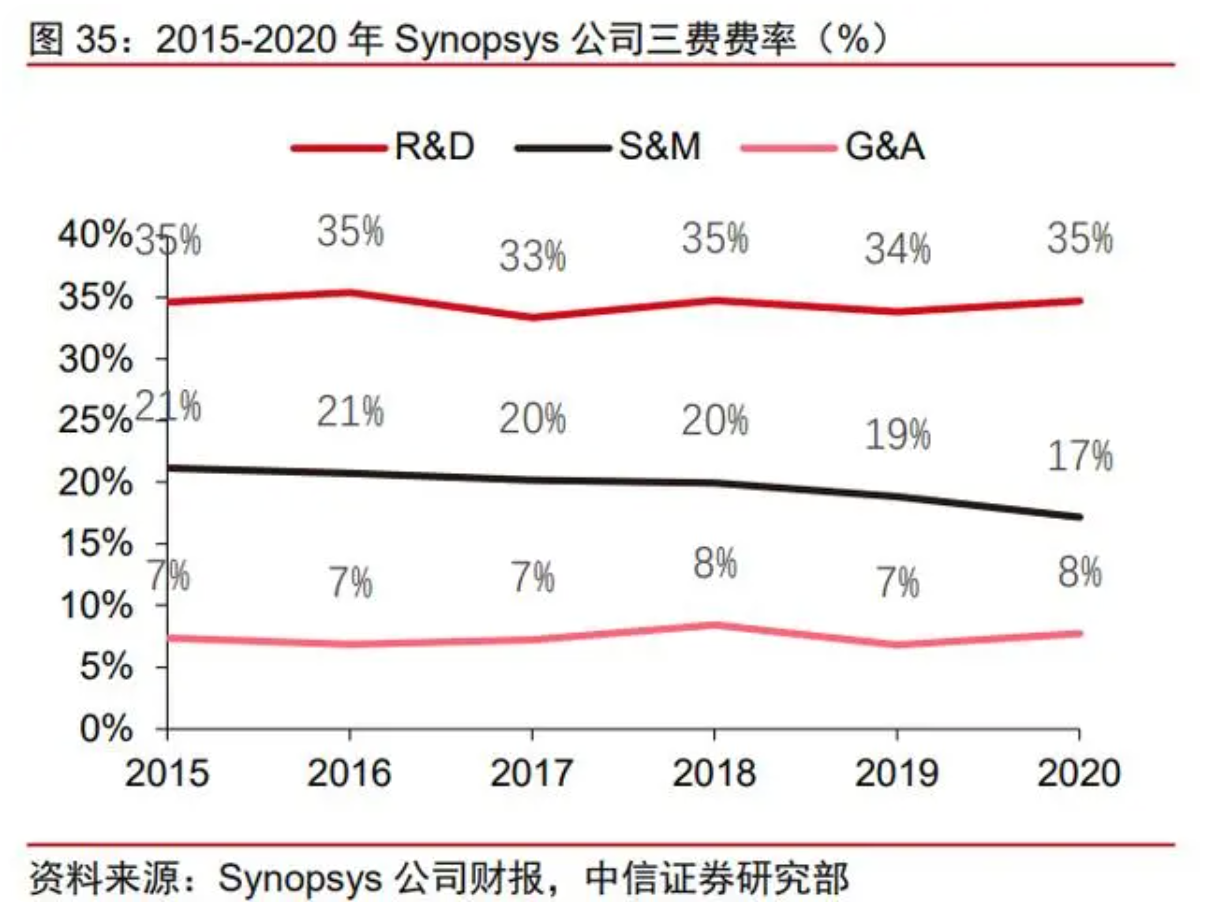

1) 研发需求:行业巨头持续高研发提升产品质量,从而形成高营收、高研发、优化 产品、降本增效的良性循环。根据Synopsys和Cadence公司财报数据,2015-2020 年两公司管理费率维持 7%波动;销售费率随着市场格局逐步稳定从而稳步下降;研发费率保持较高水平,Synopsys 公司研发费率约 34%,Cadence 公司研发费 率约 40%。高昂的研发费率维持行业巨头领先优势,持续固化技术壁垒。

2) 并购需求:EDA 三巨头历史并购上百次,补全产品矩阵。根据南山工业书院工业 软件组统计,EDA 国际三巨头历史并购共 200 余次,并购范围覆盖工具、SIP 公 司等。一家 EDA 软件公司难以独立研发出色的 EDA 软件前端后端全流程,收购 点技术出色的 EDA 软件公司并进行整合成就 EDA 巨头。

3) 复合人才需求:EDA 软件依赖相关复合型人才提升产品质量。根据前文对 EDA 软件人才需求的介绍,EDA 软件青睐具有数理背景、计算机知识以及芯片设计经 验的复合型人才。复合型人才能够在求解方程、仿真可靠性等方面提升产品的性 能和可靠性,为芯片设计厂商顺利流片保驾护航。根据 Synopsys 年报,截至 2020 年 10 月 31 日,公司拥有雇员 15036 名,约 80%以上是工程师,其中近半数拥 有硕士及以上学位。

半导体知识产权 SIP 成新增长点,EDA 厂商布局于此构建完成解决方案,竞逐增量 市场。根据 Synopsys和 Cadence公司发展历史,其前期收购主要是通过收购点工具公司, 不断完善自身产品矩阵,最终形成全流程解决方案。近些年收购主要布局 SIP 模块及面向 新场景的仿真测试工具。以 Synopsys 为例,公司近两年分别收购德国汽车软件开发、仿 真、测试工具企业 QTronic GmbH;FPGA 电路板解决方案公司 DINI Group;存储器、接 口 SIP 公司 eSilicon;存储器、接口 SIP 公司 INVECAS 等。

海外巨头 SIP 营收高速增长,占比持续提升,有望成为业务高速增长的主驱动力。根 据 Synopsys 和 Cadence 财报数据,Synopsys 公司 IP 和系统集成部份营收占比从 2017 年的 28%提升至 2020 年的 33%,2017-2020 年 CAGR 为 17%;Cadence 公司 IP 部分占比从 2016 年的 11%提升至 2020 年的 14%,2016-2020 年 CAGR 为 17%。SIP 业务对 目标功能的设计进行封装,提高芯片设计人员开发效率。受半导体下游新应用场景催化, SIP 业务占比持续提升。

龙头崛起规律 2:上下游生态绑定紧密,下游厂商是 EDA 的试金石

EDA 软件脱胎于半导体生产垂直整合模式,蕴含芯片生产基因。根据《芯路》(作者:冯锦锋、郭启航)描述,上世纪中叶,半导体发展早期,惠普公司 HP、德州仪器 TI 等公 司下设 CAD 部门,并以加州伯克利 Pederson 教授所开发的仿真程序 SPICE 为基础进行 半导体研发。随着集成电路复杂性增大,芯片设计厂商难以单独承受高昂研发费用,促使 EDA 软件从垂直整合模式向独立软件方向发展,但是上下游联动依然紧密。

以 Cadence 为例,1982 年,来自加州伯克利和贝尔实验室的科学家们创建 Cadence, Cadence 邀请下游厂商 GE、爱立信、IBM 等半导体厂商入股,各 100 万美元,几家 VC 入股不超过 100 万美元,下游厂商有意愿将最新的制造工艺反馈给 Cadence 公司。Synopsys 公司创始团队出自通用电气微电子中心,同样具有相关技术背景。

构建上下游生态体系,下游带动上游 EDA 软件革新。如前文所述,EDA 软件厂商、 芯片设计厂商和下游代工厂三方面合力构筑生态体系。以台积电为例,其大联盟生态是半 导体行业规模最大的生态平台之一,其生态体系包括 EDA厂商、独立 IP厂商等,Synopsys、 Cadence 和 Siemens EDA 部门均在生态体系中占据一席之地。

根据格罗方德官网资料,公司在 2016 年成立合作伙伴计划 FDXcelerator,旨在促进 22FDX片上系统(SoC)设计的生态系统,以缩短客户的产品上市时间。FDXcelerator 合作伙伴计划的初始合作伙伴包括:Synopsys(EDA),Cadence(EDA),INVECAS(IP 和设计解决方案),VeriSilicon(ASIC),CEA Leti(服务),Dreamchip(参考解决方案) 和 Encore Semi(服务)。

四、国内推演:群雄逐鹿,剑指三百亿元市场机遇

市场规模:近七十亿元市场空间,半导体高景气驱动 EDA 快速增长

半导体产业:中国半导体产业链稳步增长,2020 年市场规模达 1517 亿元。根据 WSTS 数据,中国 2020 年半导体产业市场规模达 1517 亿美元,同比增长 5.0%,占全球半导体 产业 34.4%。根据中国半导体行业协会测算,2020 年中国集成电路市场规模为 8848 亿元, 2014-2020 年 CAGR 为 19.7%,保持快速增长。半导体产业链第三次转移向中国进一步 稳固中国在全球半导体产业链中市场地位。

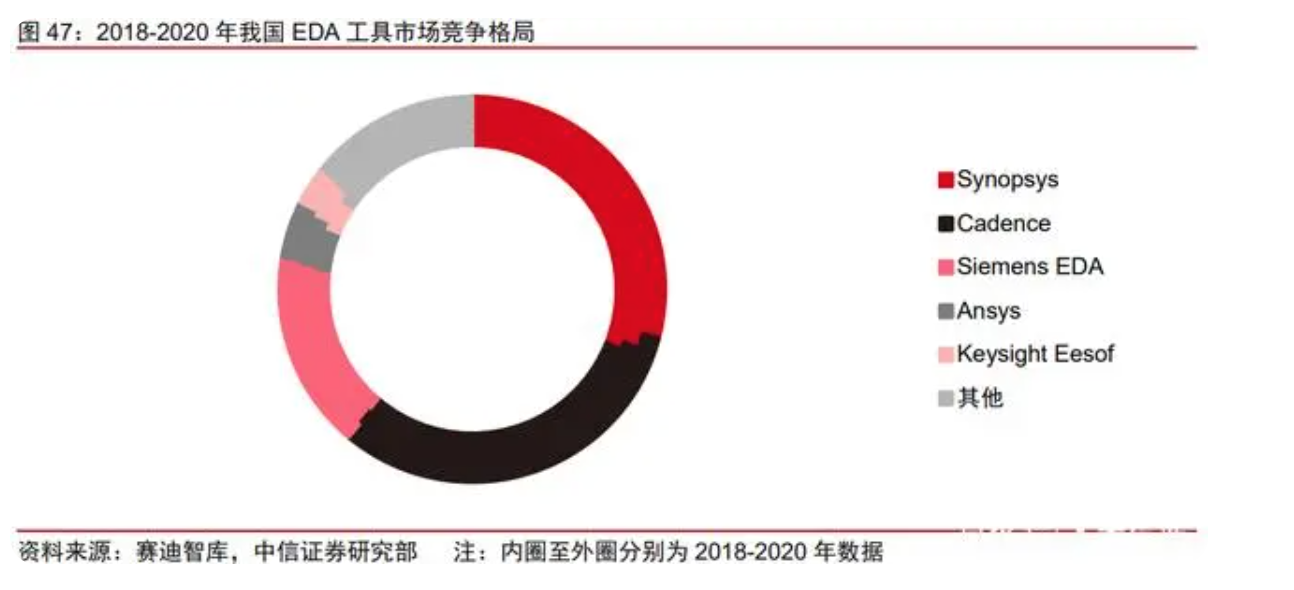

EDA 软件:2020 年中国 EDA 市场规模为 66 亿元,市场规模快速扩张。根据赛迪智 库数据,2018-2020 年中国 EDA 软件市场规模从 44.9 亿元增长至 66.2 亿元,CAGR 为 21.4%。结合 ESD Alliance 数据,2018-2020 年中国 EDA 软件市场规模占全球比例从 7% 增长至 9%,远低于中国半导体产业链占全球半导体产业链的比例。

下游芯片设计厂商数目显著增加,芯片设计行业景气高增长。根据中国半导体行业协会集成电路设计分会年会数据,中国芯片设计企业规模持续增长,2020 年达 2218 家,同 比增长 24.6%,北京、上海、深圳等地设计企业聚集。半导体产业及芯片设计高景气带动 EDA 软件需求迅速增长。

主要参与者:国产 EDA 点工具较多,以点带面提升产品能力

中国 EDA 起步较早,受国内国际两方面影响未大规模推广。自建国初期,巴统(巴 黎统筹委员会)对中国实施禁运,EDA 软件受政策影响无法进入中国。1986 年,国家动 员全国 17 个单位和 200 余位专家在北京集成电路设计中心联合研发 EDA 软件,于 1993 年发布熊猫 EDA 软件。熊猫 EDA 随后获两项国际大奖。

受 1994 年“巴统”解散,美国解除对中国的 EDA 软件封锁和国内“造不如买、买不如租”的思想两方面原因影响,熊猫 EDA 未能被广泛使用。

2008 年 4 月,“核高基”科技重大专项方案经国务院审议通过。EDA 行业作为《国家 中长期科学和技术发展规划纲要(2006-2020 年)》所确定的十六个重大专项之一,重新 获得了鼓励和扶持。国内 EDA 领域涌现出一批优质的企业,如概伦电子、广立微电子、 国微集团和芯和半导体等,中国本土 EDA 企业逐步进入全球视野。

提供点工具企业众多,看好头部企业以点带面式发展。中国 EDA 软件大多以点工具 为突破口,少有 EDA 厂商拥有针对某种半导体产品的全流程解决方案,与下游代工厂、 芯片设计厂商构筑生态体系者寥寥。

拥有点工具尖端技术公司料将通过并购等方式扩大产品矩阵,强化产品的技术壁垒, 实现以点带面的发展。概伦电子于 2019 年并购北京博达微科技有限公司,持有 80%股份, 意在利用博达微的 AI 驱动的测试和建模技术,增强概伦电子在半导体建模和测试的领先地 位。我们认为,拥有尖端点技术公司、资金充沛的公司有能力通过并购的方式以点带面发 展,并以全流程解决方案为盾坚守市场份额。

成长逻辑:EDA 国产化势在必行,三百亿空间前景广阔

“卡脖子”赛道国产化替代势在必行。随着 EDA 国际巨头对中国芯片设计企业断供, 其对中国芯片设计企业的影响主要有三点:

1)无法使用最新版本的 EDA 软件进行芯片设 计;

2)无法使用先进的 IP 进行芯片设计;

3)无法获得下游代工厂的生产工艺 PDK。EDA 软件作为“卡脖子”赛道,自主可控势在必行。结合中国目前市场环境和上世纪日韩半导 体崛起经验,我们从政策、人才、资金、上下游产业链的角度对国产 EDA 软件崛起驱动 因素进行分析。

资金、人才打造优质产品,上下游生态初具雏形。

1)政策层面:工业软件、集成电路政策鼓励。EDA 软件属于产品创新数字化软件, 同时位处半导体产业链上游,相关政策对 EDA 软件影响显著。近年来,随着国际 EDA 巨 头和相关下游制造厂商对中国半导体行业的断供,中央、地方政府政策频出,促进 EDA 软件发展。

日韩启示:国家支持,整合业界资源是半导体产业发展的先决条件。日韩半导体的崛 起与国家支持紧密相关,国家在政策、行业整合、资金等多方面的大力支持才能够扶持起 半导体这一规模庞大但至关重要的产业。

日本于 1974 年批准“VLSI 计划”,联合日立、NEC、富士通、三菱、东芝公司 研发 DRAM 存储器。1982 年,日本 DRAM 市场份额排名第一。举国体制、行业 资源整合实现技术攻坚。1980-1989 年,世界半导体份额占比,美国从 57%下降 至 35%,年均下降 2pcts,日本从 27%上涨至 52%。

半导体产品研发成本较高,为加速半导体制造技术追赶进程,韩国以三星等公司 为主要力量进行半导体工业先进技术研发。

2)资金层面:大基金及产业资金支持,龙头企业 IPO 进展加速。国家大基金于 2018 年 9 月投资 EDA 产业龙头公司中国电子、建元投资等跟投。华为旗下投资公司哈勃科技 布局 EDA 软件,分别投资湖北九同方微电子有限公司、无锡飞谱电子信息技术有限公司 和上海立芯软件科技有限公司。九同方微电子专注 IC 设计软件,提供 IC 流程设计工具、 IC 电路原图设计、电路原理仿真等工具。飞谱电子专注为芯片设计、制造、封测厂商提供 解决信号及电源完整性、电磁兼容及干扰等挑战的产品。上海立芯软件科技有限公司专注 物理设计和逻辑综合等 IC 工具研发。

日韩启示:资金购买专利技术加速追赶。对于技术和相关工具的收购有助于我国 EDA 软件的快速追赶。根据 Synopsys 2020 年报,软件完整性功能海外竞争公司有以色列 Checkmarx 公司、英国 Micro Focus International plc 公司。根据 Cadence 2020 年报, 海外竞争公司有澳大利亚的 Altium Limited;日本的 Zuken Ltd.。通过并购的方式可以加 速企业全流程解决方案的实现,有望加速国产化替代。

根据《芯路》描述,19 世纪 50 年代,日本的索尼、NEC 等公司从美国购买专利 并在此基础上进行研发,集成电路产业快速发展。日美厂商随后成立合资公司, 实现半导体技术快速追赶。

在韩国半导体技术追赶的过程中,以三星公司为例,三星希望购买技术的诉求被 美国的摩托罗拉、德州仪器,日本的东芝、日立等拒绝。但是三星依然从美国的 CITRIX 公司购买了 CMOS 工艺技术;从美光公司购买了 256KB DRAM 技术;从日本的夏普公司购买半导体生产设备等。十年时间从组装切入半导体制造, 1979 年 16KB DRAM 研制成功,掌握 VLSI 技术。

3)人才层面:产学研结合,内资 EDA 企业人才数目大幅增长。为贯彻《鼓励软件产 业和集成电路产业发展的若干政策》,国家教育部、科技部于 2003 年成立国家集成电路人 才培养基地,目标是为国家培养 4 万名电路设计人才。支撑单位包括北大、清华、北航等 20 所高校。高校培养模式中覆盖 EDA 软件,如北京大学软件与微电子学院集成电路方向 包括集成电路设计与 EDA;清华大学计算机系设置 EDA 实验室;北京航空航天大学设置 EDA 实验室并开设“计算机 EDA 设计”课程。国内龙头 EDA 厂商与清华、复旦、浙大、 福州大学等共建实验室,鼓励培养 EDA 领域人才。在学生培养阶段构建软件使用习惯有 助于为企业培养人才梯队,熟悉相关软件。

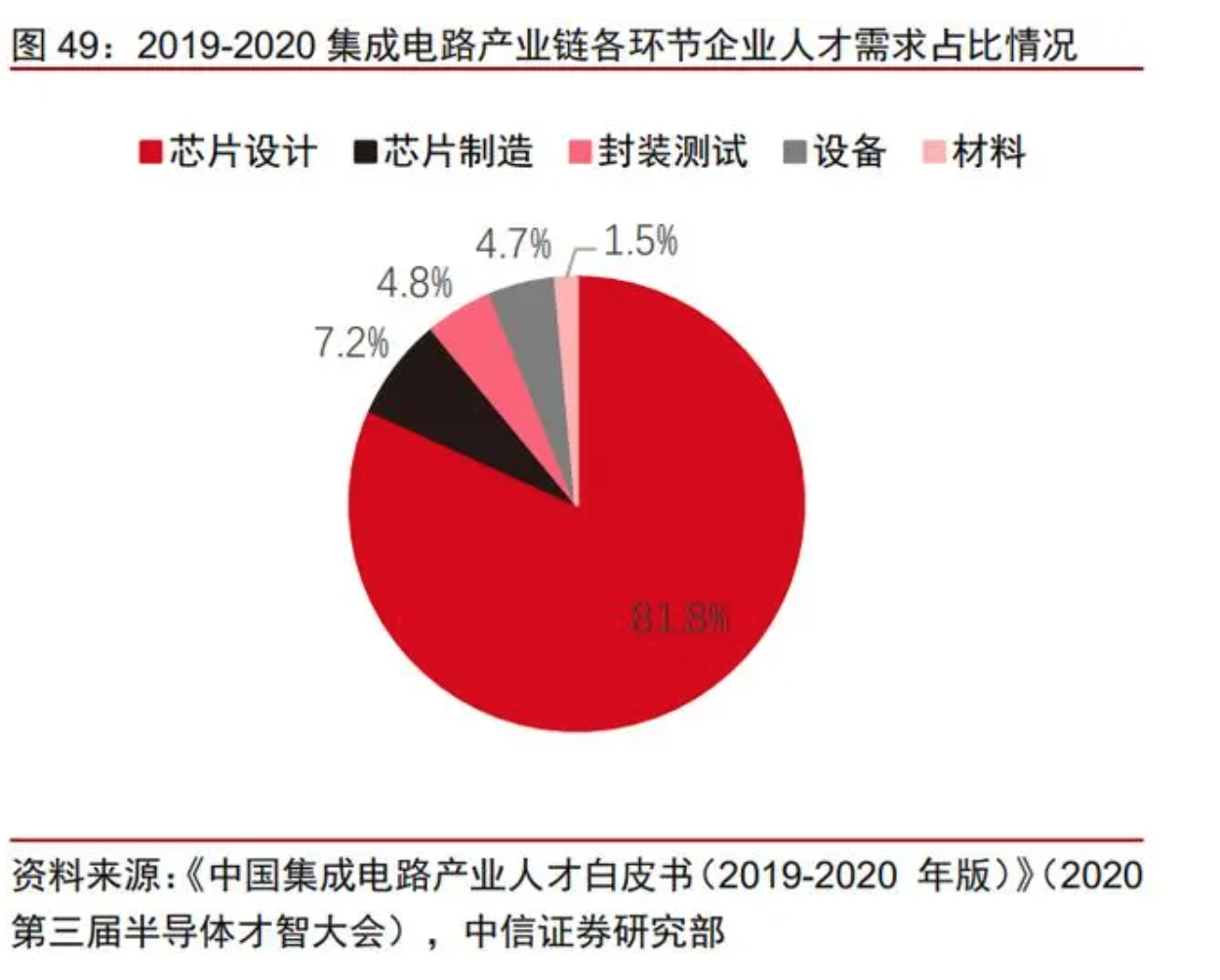

根据 2020 第三届半导体才智大会发布的《中国集成电路产业人才白皮书(2019-2020 年版)》数据,芯片设计领域人才需求占集成电路产业 81.8%,人才缺口较大。根据赛迪 智库集成电路研究所数据,内资 EDA 企业人数从 2018 年约 700 人增长至 2020 年约 2000 人,外资 EDA 企业同期从 2100 人增长至 2400 人。

4)生态层面:上下游产业联动,强化软件、设计、代工生态,本土龙头正在崛起。EDA 软件、芯片设计、代工厂三方面结合实现良性循环有助于 EDA 厂商实时更新 PDK 套 件,SIP 库等,与下游代工厂紧密结合的 EDA 厂商将更加具有竞争优势。以概伦电子为例, 概伦电子提供面向集成电路设计的 EDA 软件,其 2018-2020 年国内客户包含中芯国际、 华力微、上海先进半导体制造有限公司、长江存储等,国外客户包含台积电、美光科技、 联电、三星电子等。2020 年概伦电子营业收入达 1.4 亿元,2018-2020 年 CAGR 为 62.7%。整体来看,我国 EDA 产业链生态初具雏形,上下游协同发展初见端倪。

空间测算:从半导体产业市场规模和 EDA 软件渗透率角度对未来空间进行测算,对 应 EDA 软件市场规模。

1)半导体产业市场规模:根据 WSTS 数据,2020 年全球半导体市场规模为 4404 亿 美元,2014-2020 年 CAGR 为 4.62%,WSTS 预测 2021 年全球半导体市场增速将达到 19.7%。2020 年中国半导体产业市场规模达 1517 亿美元,同比增长 5%。受益于下游新 场景如 5G、自动驾驶汽车等,半导体产业高景气;受益于半导体产业链向中国转移,以 及半导体产业链国产化趋势明显,预计中国半导体产业增速将超全球平均水平。我们预计 中期中国半导体产业市场规模有望达到 2000 亿美元。

2)国产 EDA 软件渗透率:根据 ESD Alliance 数据,2020 年全球 EDA 软件市场规模达 115 亿美元,相较于 4404 亿美元的半导体产业链,渗透率为 2.6%。根据赛迪咨询数据, 2020 年中国 EDA 软件市场规模为 66.2 亿元,相较于 2020 年中国半导体产业 1517 亿美 元市场规模,渗透率仅为 0.6%,近 3 年年复合增速为 21.4%,增长动力强劲。随着半导 体产业链向中国转移过程中芯片设计行业高景气,EDA 软件市场规模有望向国际平均渗透 率看齐。我们预计中期中国 EDA 软件渗透率达到 2.6%。

基于以上假设,我们粗略估计中国 EDA 软件中期市场规模超 50 亿美元,对应超 300 亿元人民币。

原文:FPGA 的逻辑

来源:九岳股权

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。