1 .AXI3与AXI4之间的区别是什么?

- AXI3只支持多达16拍的burst 。而AXI4支持高达256拍的burst 。

- AXI3支持write interleave。AXI4不支持write interleave

- AXI3支持locked 传输,AXI4不支持locked 传输

- AXI4支持QoS,AXI3不支持QoS。

2. 为什么没有单独的read 响应通道?

VALID/READY握手机制只允许一个方向的数据流,所以对于读事务,数据(data和resp)从slave流向master,而对于写事务,数据从master流向slave,所以就需要单独的响应通道

3.为什么在burst 写中,不是每拍都有写响应。但是在burst 读中,每拍都有一个单独的读响应?

所有的AXI信道只在1个方向传递信息 ,所以才需要一个单独的写响应通道。在大多数应用中不管slave能不能接受完整的数据这个burst传输都会执行完成,slave无需在每一拍都返回ERROR响应

4.如何终止burst 传输?

不能。AXI不能够提前终止burst传输。对于写事务,master可以完成burst 传输,通过WSTRB信号丢弃掉无效数据即可,对于读事务同样也可以将读回的数据丢弃。

5.master 可以在burst 传输中间给WLAST吗?

不行。只有在burst 传输的最后一拍才能拉高WLAST,在burst传输的中间拉高WLAST是违反协议的行为。此外,许多slave设计不会使用WLAST信号,而是自己计数,所以master拉高WLAST也不会提前终止burst传输。

6.Slave能在burst传输完成之前置起rlast么?

和上题一样,slave在burst传输的未完成就拉起RLAST是违反协议的行为。master同样也有可能不依赖RLAST

7.既然WLAST和RLAST可能不被使用,那为什么需要支持这两个信号?

为了支持所有的master和slave,无论其是否依赖这两个信号传输数据。

8.Exclusive 读写事务是什么?在哪里使用?

如果一个内存区域被多个master共享,某个master需要希望确保在没有其他master更改共享内存的情况下完成读然后写的序列,就可以使用Exclusive 传输

9.读取事务是否有可能在一个周期内完成?

需要至少1个时钟周期传递地址(从master到slave),然后至少1个时钟周期传递数据(从slave到master)。

10.axi slave是如何支持Exclusive 访问的?

假设 AXI Master1(M1)已经启动了对地址位置12h100到12h10F的exclusive 读写。那么相应的salve将开始监视由M1给出的这些地址。如果此时该地址被其他master执行写操作,此时会返回Exclusive error。

11.发送给slave的读写地址和读写数据是如何关联的?

AR总线和AW总线是独立的,不管读写请求的地址是否顺序发出的,响应的数据都可能是无序的,他们之间是通过awid和arid对应配对的。

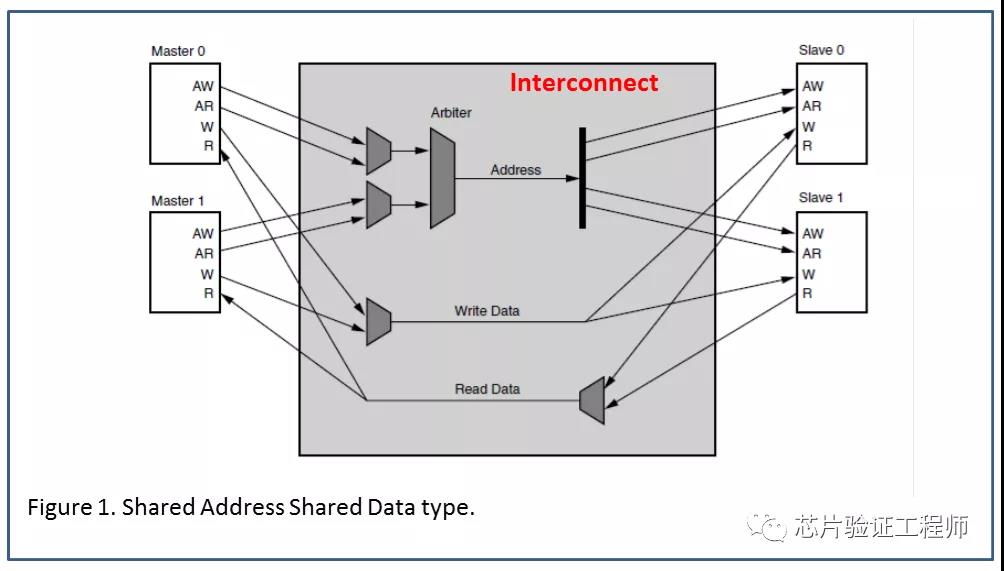

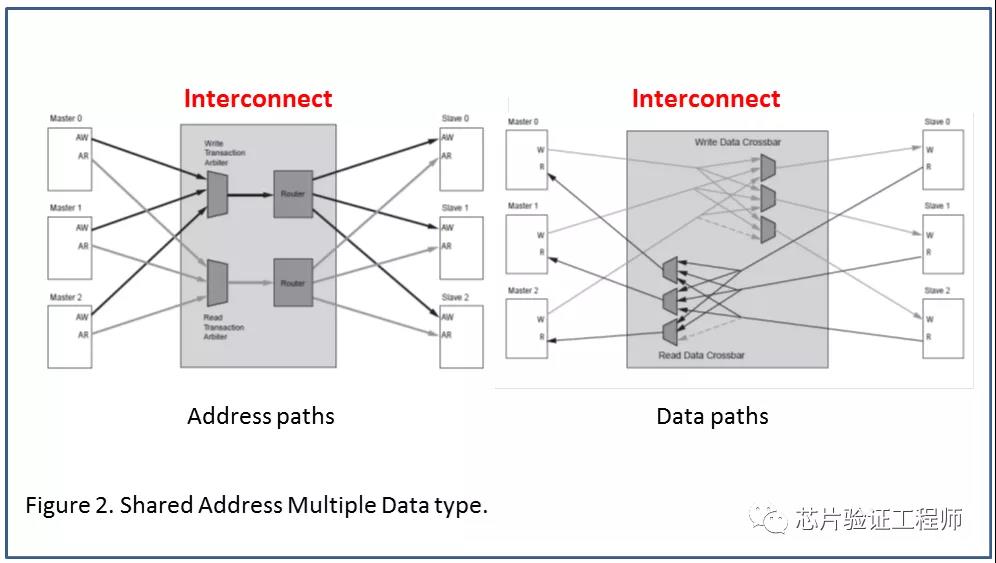

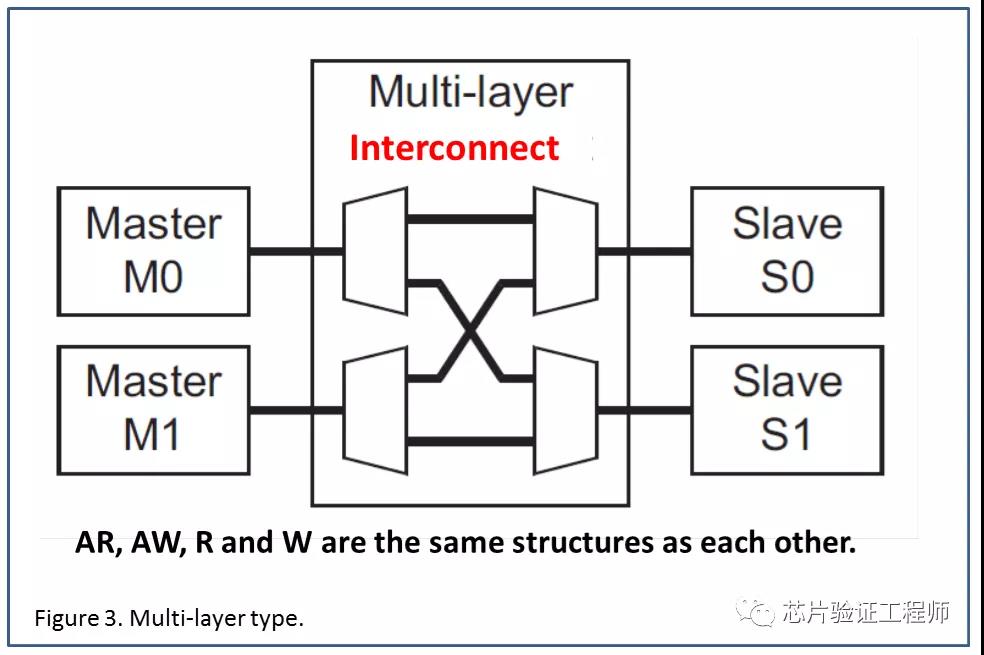

12.在AMBA规范中,其中提到了3种不同的拓扑(共享地址和数据总线、共享地址和多个数据总线和多个地址和数据总线),这些互联是什么意思?

END

作者:验证哥布林

原文链接:https://mp.weixin.qq.com/s/bnCXWIL-b1vtFeZFaTIdfA

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。