后端工作大家最关注的首先是绕线,其次是timing。优先级排列,绕线优先于时序。

其实非常好理解,绕线都不同,时序当然也不准。

如果问绕线问题你会怎么解决。基本都能回答出来,调整floorplan,加padding,挪cell,甚至,试一试工具的相关选项。

本文想让提醒大家,下面这个方法别忘了。

下面来说一个遇到的案子。

首先在place阶段,congestion map没有问题。但是最后绕线的时候,会发现某几种类型的cell的有short问题。深入分析下来,其实是因为cell的pin不在track上,因此如果打孔的时候,就会打歪。于此同时,cell内部还占用了M2。这样的些打歪的孔就会和cell内部的M2发生短路。

看下图就会更加直观。

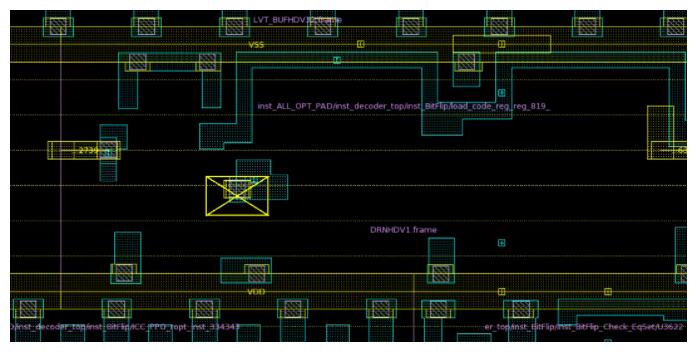

这个是改M2 track之前的layout:

可以看到,track基本都被挡住了。M2的绕线根本无法进入到cell。这时候M1的pin自然会被挡住。

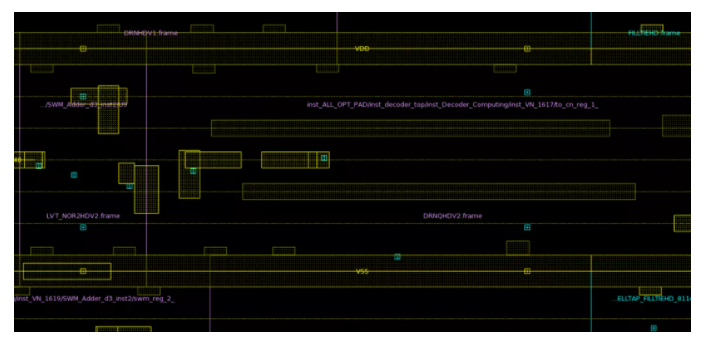

而修改之后,你会看到有三根绕线资源都空出来了。这仅仅是对M2的track做了半个track距离的平移。

通过这种方法,本案中M1,M2的short的问题解决了。如有不清楚的地方,可以微信中讨论。

作者:白山头

原文链接:https://mp.weixin.qq.com/s/vraa1UFBckpddaLTMnwe6A

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。