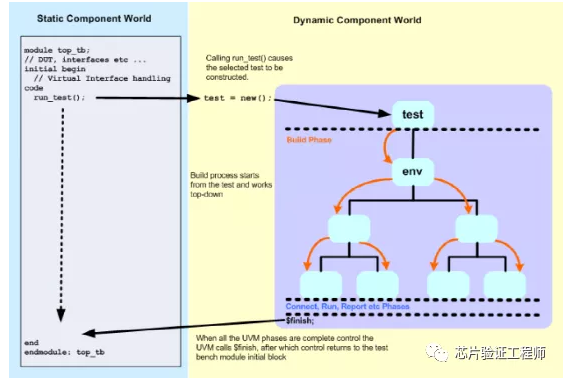

在UVM testbench开始发送激励之前,必须构建其组件层次结构以及验证组件之间的连接关系。

UVM testbench 的第一阶段(phase)是build phase,在此阶段自上而下地实例化组成验证环境层次结构中的各个uvm_component类。

当在顶层的initial 语句块中调用run_test()方法时,就开始激活验证平台的构建,即从testcase开始依次调用各组件的build_phase。在执行test case的build phase期间,需要准备好testbench配置对象,并将virtual interface赋值给testbench中各个组件中的virtual interface句柄。

在下一级的层次结构(uvm_env)中,将根据从testcase获取的配置对象进一步地配置(uvm_agent)并可以根据实际情况进行更改。在build phase完成后,将开始connect phase确保完成所有组件之间的连接(自下而上)。等到所有的uvm_phase运行完成,会将控制权再给到test case。

简而言之,在发送测试激励之前需要完成验证组件的构建、配置和组件之间的连接。

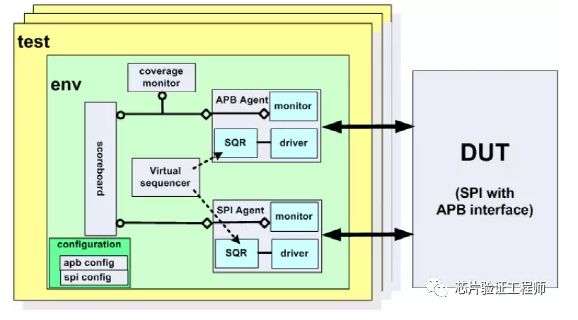

UVM testbench 的构建过程从test case开始,决定了构建怎样的验证平台:

• 进行factory override,以便将配置对象或组件对象替换为为派生类型

UVM factory 允许一个UVM类在构建时被另一个派生类替换,必须在构建对象之前就指定factory override,因此需要在该组件上层的build phase进行指定。

• 设置一个层次化的env配置对象,其中包含各种子组件所需的配置对象

每个验证组件如env或agent ,都应该有一个定义其结构和行为的配置对象。这些配置对象应该在build phase方法中创建,并根据测试用例的要求进行配置。如果验证子组件的配置比较复杂或者可能需要发生更改,那么值得添加一个 virtual function调用并在扩展的测试用例中重载

class spi_test_base extends uvm_test;

`uvm_component_utils(spi_test_base)

spi_env m_env;

spi_env_config m_env_cfg;

apb_agent_config m_apb_cfg;

spi_agent_config m_spi_cfg;

// Standard UVM Methods:

extern function new(string name = "spi_test_base", uvm_component parent = null);

extern function void build_phase( uvm_phase phase );

extern virtual function void configure_env(spi_env_config cfg);

extern virtual function void configure_apb_agent(apb_agent_config cfg);

endclass: spi_test_base

function spi_test_base::new(string name = "spi_test_base", uvm_component parent = null);

super.new(name, parent);

endfunction

// Build the env, create the env configuration

// including any sub configurations and assigning virtual interfaces

function void spi_test_base::build_phase( uvm_phase phase );

// Create env configuration object

m_env_cfg = spi_env_config::type_id::create("m_env_cfg");

// Call function to configure the env

configure_env(m_env_cfg);

// Create apb agent configuration object

m_apb_cfg = apb_agent_config::type_id::create("m_apb_cfg");

// Call function to configure the apb_agent

configure_apb_agent(m_apb_cfg);

// More to follow

endfunction: build_phase

// Convenience function to configure the env

// This can be overloaded by extensions to this base class

function void spi_test_base::configure_env(spi_env_config cfg);

cfg.has_functional_coverage = 1;

cfg.has_reg_scoreboard = 0;

cfg.has_spi_scoreboard = 1;

endfunction: configure_env

// Convenience function to configure the apb agent

// This can be overloaded by extensions to this base class

function void spi_test_base::configure_apb_agent(apb_agent_config cfg);

cfg.active = UVM_ACTIVE;

cfg.has_functional_coverage = 0;

cfg.has_scoreboard = 0;

endfunction: configure_apb_agent• 配置验证环境中各组件的virtual interface句柄

在调用UVM run_test()方法之前,DUT顶层I/O上的信号应该通过连接到 SystemVerilog interfaces并赋值给virtual interface,然后通过uvm_config_db::set将每个接口的virtual interface赋值给所需的验证组件,然后各个组件访问其配置对象内部的virtual interface手柄,以驱动或监视DUT信号。

if( !uvm_config_db #( virtual apb3_if )::get(this, "" , "APB_vif",m_apb_cfg.APB) )

`uvm_error(...)作者:验证哥布林

原文链接:https://mp.weixin.qq.com/s/T3Oqxu6tb-IWfuq3KbmF3g

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏