说起FPGA之前,先提个问题。

芯片的本质是什么?

老哥认为芯片的本质是电路!

简单来说,数字芯片,不论多复杂,其底层就是 与,或,非的组合。

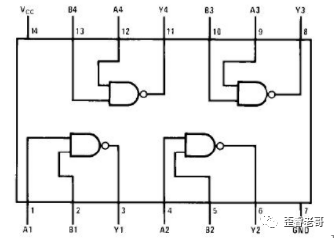

这个是某宝上可以买到的世界上简单的芯片之一, 74LS系列,很便宜,两毛钱;

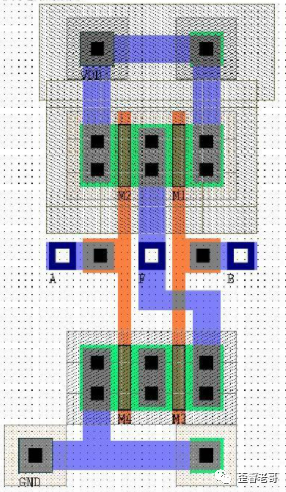

其功能就是二输入与非门。这是一个最简单的芯片,其电路和版图如下

上图中一共4个二输入与非门。

而CPU或者GPU等大芯片,有几千万门甚至上亿门的电路。

但是如果我们深入到大芯片的底层,就会发现这些大芯片也是一个与非门,或非门,等逻辑门组成的。

这就是电路,CPU和GPU也是一种电路的组织形式。

无论多复杂的芯片,都是芯片设计工程师通过硬件描述语言(HDL)来描述电路。看起来像是和软件工程师一样,都在敲代码,在编程,实际上是在搭电路。

EDA工具把语言转换成电路,最终得出这个版图(GDS)。然后这个版本提交给厂家生产。流片厂家把GDS变成硅。封装厂家完成硅 (DIE)到 CHIP的封装。这个过程和设计PCB电路基本上是非常相似的。都是电路转换成PCB 到厂家制版。

我们所说的卡脖子,目前看,主要是制造环节,也就是从版图到硅的阶段。其他也有,但是这个问题这个有时间找专题另说。

今天主要说一下 ,设计一款芯片研发最大的问题是啥?

有两点是大家公认的。

第一,研发迭代周期长:

大芯片花费了一年或者2年研制,这个很常见。或者因为功能缺陷,或者市场变化,最终没有卖出去,又要重新迭代。这个就是非常恐怖,小的芯片公司,因为芯片失败,钱花光,直接一波流带走也是很常见的。

第二,芯片投入高:

芯片研发包括流片成本,IP成本,人力成本等。28nm的MASK在1000万,12nm接近2500万,除此之外还有人力,IP等成本。研发一颗28nm的芯片总投入成本投入大几千万还是有的,7nm和5nm更是几亿的投入。这么高的成本(NRE),将来要分摊到每一颗芯片上去的。

如果一个项目或者需求,只有几千颗或者几万颗的量,是否值得来去研发芯片就是一个很大的问题。

流片不合适,那么没有一种替代的方案?迭代周期短,代价小的实现这个电路的需求。

FPGA,他来了!

1:FPGA:实现电路的电路

FPGA Field Programmable Gate Array。 场可编程门阵列。FPGA和专用芯片不同。可以编程。

文章开头说过了, 芯片的本质就是电路。

那么FPGA的本质是什么?FPGA本质也是一种芯片。

但是可以也可以实现数字电路功能,如CPU,GPU,NPU等这些电路,都可以放在FPGA内部实现,效率另说。。

那FPGA的本质就是可以通过编程实现电路的电路。

这个是怎么做到的?

或者说,什么样的电路可以实现与或非这些基本操作

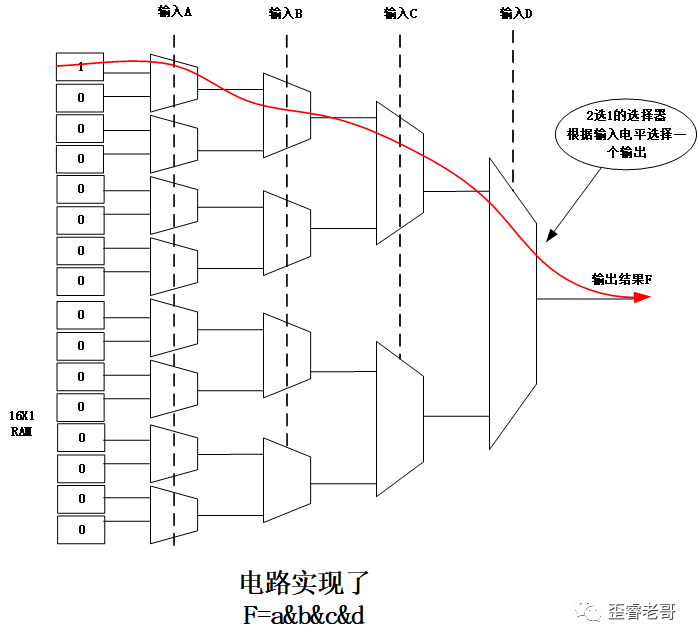

我们以 F=A&B&C&D 这个电路举例:一个16x1的RAM,这个RAM的每一bit都可以编程为0或1。这个RAM有4位地址, DCBA。通过这4bit选择RAM的输出。通过配置RAM中不同的值,实现输出F 和输入A,B,C,D的关系

上图中,我们把16bitRAM 配置为 0000000000000001 ,这个电路 则等效 F=A&B&C&D;

只有A=B=C=D=1时, F=1,其他情况 F=0;完美实现了 F=A&B&C&D;

重要的事情再说一遍;

16bitRAM 配置为 0000000000000001 , 则等效F=A&B&C&D;那么现在“0000000000000001” 这串数就是FPGA的编程。

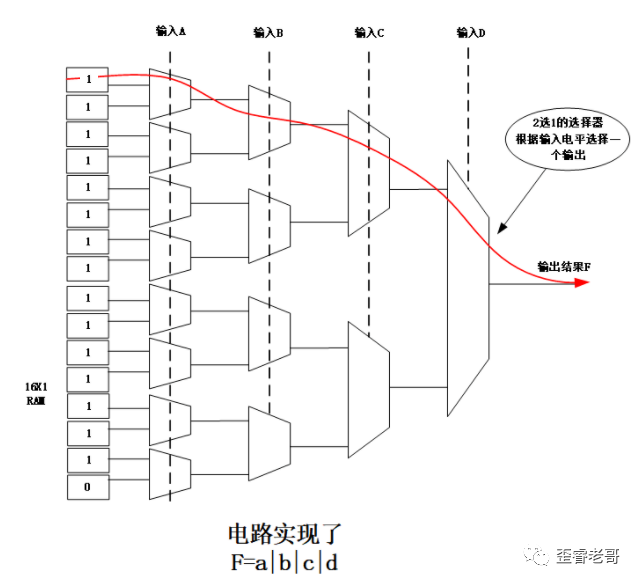

这就是FPGA最基本的原理;举一反三,如果实现电路 F=A|B|C|D 。

这个电路如何编程:

16bit RAM 配置为 01111111111111111, 则等效F=A|B|C|D。

大家可以试一下:通过配置16bitRAM 的值,可以实现A,B,C,D四个输入的任何逻辑操作。

FPGA就是利用了这个转化,具备了描述任何电路的能力。

上图这个结构在FPGA中有一个专有名词,叫做LUT ,lookup table( 查找表)。

LUT就构成了所有FPGA的最基本的单元。

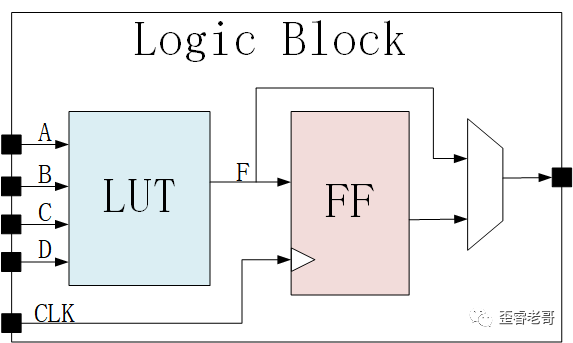

LUT只能实现数字组合逻辑,所以又添加了一个寄存器flipflop (ff),可以实现数据的锁存;

如下图所示:LUT+寄存器构成了现代FPGA基本结构。

FPGA的基本结构,就是依靠如此简单的电路实现了无比复杂的逻辑。

这个包括LUT和FF的基本结构,这两个合并成为一个基本的逻辑单元(LOGIC BLOCK)。

这种能够实现ABCD四个输入计算的LUT的叫做4输入LUT,此外还有5输入,6输入等等变种。

万变不离其宗。这种结构,从FPGA诞生以来,就没有怎么变过。这个电路,也可以看作是一个最小的FPGA。

现在能实现一个功能的芯片,少则几万门,多则几千万门,上亿门。

单纯靠这个电路实现,这就是开玩笑了。

那么就需要无数的LUT和FF来实现,。

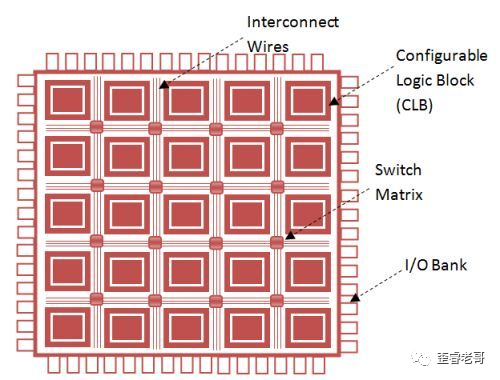

FPGA就实现了一个无数 Logic Block(Logic Block内部就是LUT+FF)的阵列,中间用布线资源连接起来。

把互联和逻辑单元结合起来就是一个FPGA芯片,图如下所示。

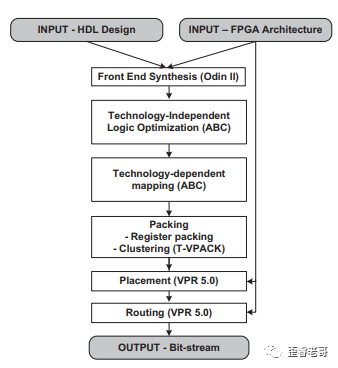

一个典型的FPGA开发流程如下。从HDL(verilog的电路描述语言)到配置文件 bit流,相比一下,专用芯片的开发流程从HDL(verilog的电路描述语言)到硅。这个时间就长多了。

这些bit流包括啥?

开头说过了,16bitRAM (LUT)配置为 0000000000000001 ,

则等效F=A&B&C&D;

FPGA最终生成的Bit-stream流,包括 LUT 的配置文件,以及布线资源的配置文件。

到这里,FPGA的设计及编程就完成了。 简单明了!

2:EDA工具:从知到行的距离

看起来设计一个FPGA芯片也不复杂。电路不复杂,市场上高性能的FPGA,可选择的余地不多。从知到行,这里面有一个巨大的鸿沟,

按照本文开头的原理,假如一个厂商设计完毕了一款FPGA芯片。等到给客户使用的时候,就碰上了一个大麻烦。

EDA工具。

如果给客户提供FPGA芯片,则需要配套提供给客户一个EDA工具。没有EDA工具,难不成让客户手动生成FPGA的bitstream的文件。芯片都做出来了,EDA工具,还难吗?

难,真的难!这是一个巨大的坑。

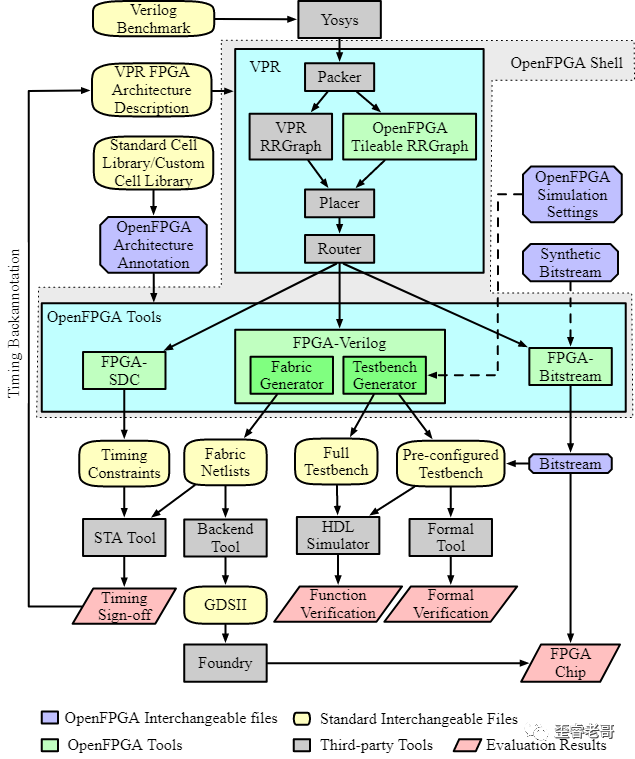

下图是一个 开源的FPGA的设计流程(OpenFPGA),我们可以看看,即使一个开源项目,其涉及到的EDA工具最少都要有哪些?

这些需要给客户的EDA工具包括:

1:综合工具

2:布局布线工具

3:bit生成工具

4:时序分析工具

5:仿真工具

6:嵌入式逻辑分析仪器等调试工具

7:功耗分析工具

这些还算是最少的集合,但已经比一个CPU芯片提供给用户GCC编译工具要难多了。

老哥装过某司的EDA工具,这些大小都是十几个G,比windows安装盘还要大。

如果CPU的GCC工具难度是1,FPGA的EDA工具的难度就是10到100。

借用《让子弹飞》里的一段话:项目成功了,芯片功劳怎么才占7成。七成是EDA的,芯片也就三成。就这三成,还要看EDA的脸色。

辛辛苦苦半天,做出来芯片,还要看EDA工具的脸色。

看看EDA都有哪些“脸色”?

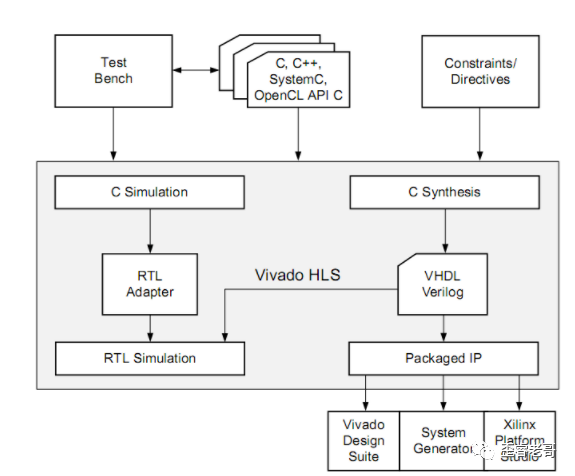

以上图的布局布线工具为例,看起来就比较复杂。如果做不好,整个FPGA的利用率极低,还布不通,你说重要不重要。除了传统的EDA工具,实现HDL,例如verilog这种编程之外,还包括HLS这种高层次综合的描述语言。

HLS的引入使软件工程师也能参与到FPGA设计中来,把电路开发屏蔽掉,直接开发软件,这个就更是EDA工具的能力了。

但是,这个本质上,讲高级语言(C,C++)转换成硬件描述语言(HDL),在通过综合工具转换成电路。

好处是,更贴近软件工程师的习惯,缺点就是加了一层转换,带来了效率的损失。

3:FPGA的架构:融合超越

文章开始说了,FPGA就是Logic Block,内部主要是(LUT+FF),以及布线资源。除了这些。FPGA还有很多硬核IP,也叫做宏单元。例如PLL,SERDES,RAM等常规IP的。

随着现在芯片的演进。FPGA内部也集成了很多新的东西。这些新东西中,比较有特色的就是CPU,在FPGA内部集成了硬核CPU系统,甚至可以运行OS(操作系统)。这样CPU+FPGA。CPU软件编程,FPGA 硬件电路编程,这个就是双剑合璧,更胜一筹。

同样serdes也是高端FPGA的必须模块,没有serdes,FPGA就是孤家寡人,没有办法实现和其他芯片电路的高速互联。

现在与外部器件连接,支持比如PCIe,SATA,10G/100G ethernet这些高速协议。数字信号处理,FPGA应用于数字信号处理等计算密集型任务,如雷达等等。所以,FPGA内部也集成了了很多DSP单元,实现乘法等操作。

为了在人工智能时代分一杯羹,有的FPGA内部集成了用于AI处理的神经网络加速的硬核。

总结一下,除了LUT,FPGA内部集成硬核IP包括:

1:RAM:用于实现存储资源;

2:PLL:提供高速的时钟信号和资源;

3:DSP:乘法操作,滤波器,数字信号处理模块;

4:SERDES:实现PCIE,SATA,FC,100G ethernet等高速接口

5:CPU系统:提供软件编程开发能力;

6:NPU硬核:提供AI处理加速;

而根据市场需要,还可能添加更多的硬核IP 与传统的FPGA进行融合。

融合更多功能IP。这就是FPGA架构未来的趋势。

4:FPGA优势:解决问题才是王道

FPGA和CPU有什么区别和优势?

我们讨论一种架构的优劣,重点是解决了什么问题?而不是CPU与FPGA,孰优?只有放在固定的应用场景下,才能说哪种架构更适合解决这些问题。

FPGA编程是电路,本质上还是可以看作,逻辑门(与或非)等等效电路。

CPU是指令操作,运行的是软件。

FPGA是时间并行运行的,而CPU是时间串行的,单CPU核总是需要一条一条来执行指令来实现功能(也有指令级并行,但原理不变)。

FPGA的并行度较高,相比CPU的计算方式,数据吞吐量大,时延控制比较好。但是CPU的频率很高,可以运行操作系统,作为通用计算单元非常灵活,并不是FPGA更能做的。

FPGA更适合做ASSP,配合CPU做专门的运算单元使用,适合专一的大数据量的计算。

FPGA既然是”万能的芯片“,似乎那就可以替代实现所有芯片功能。

是不是可以不研发专用芯片,只用FPGA。

相比专用集成电路:FPGA有三个劣势

1:面积大,成本高:

和专用集成电路(芯片)相比,FPGA由于采用LUT来表征基本逻辑门单元,所以其面积粗略来比是专用电路的10倍,所以其成本简单类比也会高很多。

2:面积大,功耗高:

同样功耗也没有优势,做低功耗设备,例如手持的供电式设备,基本不太可行。

3:运行频率低,计算效率低。

FPGA内部LUT之间,由于其互联较长,导致FPGA的频率相比同工艺下的ASIC也是慢很多。专用电路门与门之间的延迟要小很多。

但是,FPGA优势也很明显。

FPGA最大的优势,就是灵活性高。

用FPGA不用重新流片,节约了NRE成本。

在一些雷达,5G,网络,存储,高性能计算等数据密集型计算领域都有广泛的应用。

特别是需求不明确,量不大,不值得做芯片,或者,需求老在变化,FPGA都是不错的选择。

intel收购后altera后, FPGA的重心变成了数据中心市场,特别是利用FPGA在数据中心加速方面,投入颇大,最新的intel的IPU其中是FPGA技术,用于数据中心基础设施的卸载,也是类似DPU的一种实现。(见上一篇:大话DPU—从网络到数据)。

目前很多家DPU都是用Intel和Xilinx的FPGA实现的。

这个就是DPU需求不固定,数据中心对于DPU的需求一直在变化的一种体现。

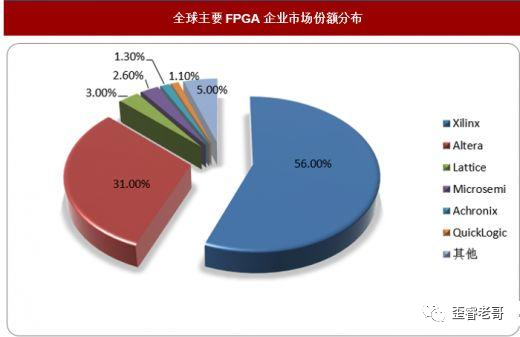

FPGA全球市场2018年大约60亿美金,Xilinx 和Altera 是这个FPGA市场上最重要的提供者,其他都是比较小的公司。(2015年英特尔宣布以167亿美元收购FPGA厂商Altera),给其他家留的份额就不多了。

老哥早些年,这两家FPGA都使用过,各有千秋。

国内也有很多FPGA的公司,有的出货也比较客观。与国外巨头相比,处于解决了有无的问题阶段,能够满足部分国产化需求。其容量,性能,特别是EDA工具方面,有明显的差距,还需要继续市场的磨练。

这里举两个国产FPGA的非典型案例,非常有意思。

2014年,俄罗斯并入克里米亚,美国出售制裁,美国对俄罗斯的封锁禁运也是很厉害,俄罗斯芯片告急,特别是高端的FPGA芯片,某司FPGA芯片抓住这个机会,解决了国际友人的燃眉之急,成就了某司的FPGA出口,也获得不错的利润。

另外,某手机大厂手机屏幕是有特殊转码格式的,所以如果返修,只能使用原厂屏,其他屏幕格式对不上,原厂屏价格很高。某司就定做了一批超小型FPGA,实现了手机屏的解码,中国的屏幕提供厂很多(LCD+LED等等),直接就可以替代原厂屏,在手机返修屏市场也是卖的风声水起。

在这些细分领域,找到了定位,实现了很大的突破,不论是利润还是数量。如果有数量几十万片,几百万片,甚至更多,做专用芯片更合适。

如果没有那么多数量,需求又不固定,用FPGA更合适。芯片设计中,其中有个环节叫做FPGA原型验证,FPGA原型验证就是把芯片代码放在FPGA做原型实现,加快芯片设计迭代的速率。

本文开始说:FPGA特性,就是能够描述芯片电路。所以数字芯片流片之前,用FPGA装入芯片逻辑来等效测试,也是非常重要的

从这个角度看,FPGA和芯片(专用集成电路)从来就不是对立的,FPGA,万能芯片,从功能上看是万能的,理论上可以实现所有功能。但是从,PPA上看,性能,功耗,面积(成本),这三个维度来衡量,又是非常受限的。

FPGA也在进化,拓展更多的领域,满足那些变化的市场需求。也有部分市场需求更为固化,被专用芯片所取代。万能的芯片,变化的应用。找到市场定位,解决用户的问题,才能获得一席之地。

FPGA是如此,芯片也是如此。

作者:申墨-歪睿老哥

原文链接:https://mp.weixin.qq.com/s/M7skXrxNw6xORHW2gKDcpg

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。