针对SpinalHDL中的两大类型Reg、Wire,来梳理下在SpinalHDL中的对应关系及声明形式。

Wire

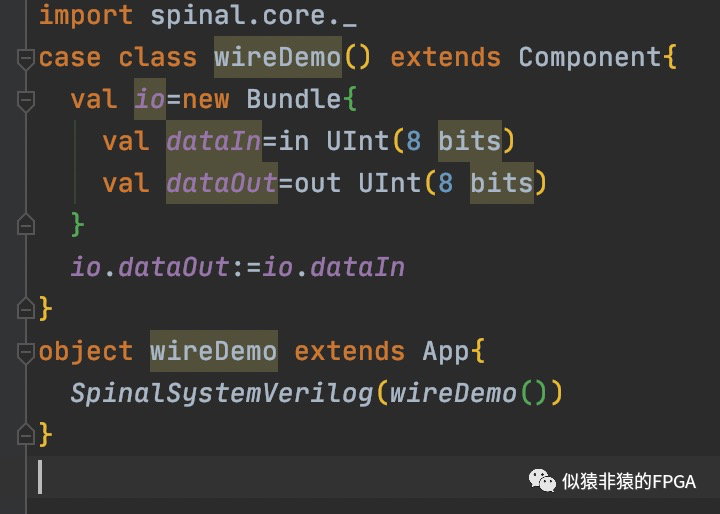

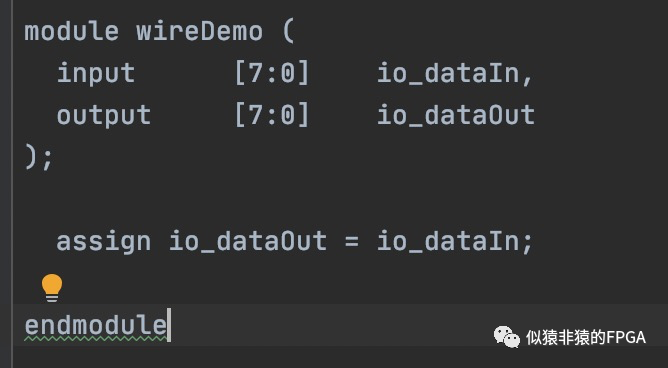

在编写Verilog时,reg、wire是我们经常用到的变量声明类型。wire类型变量常用于描述组合逻辑。而Reg则用于描述时序逻辑。在SpinalHDL中,其定义了Bool、Bits、UInt、SInt、Vec等数据类型。当我们声明一个数据类型变量时其默认均为线网类型:

在上面的代码中,我们声明了端口dataIn、dataOut、其默认均对应着RTL中的Wire类型:

Reg

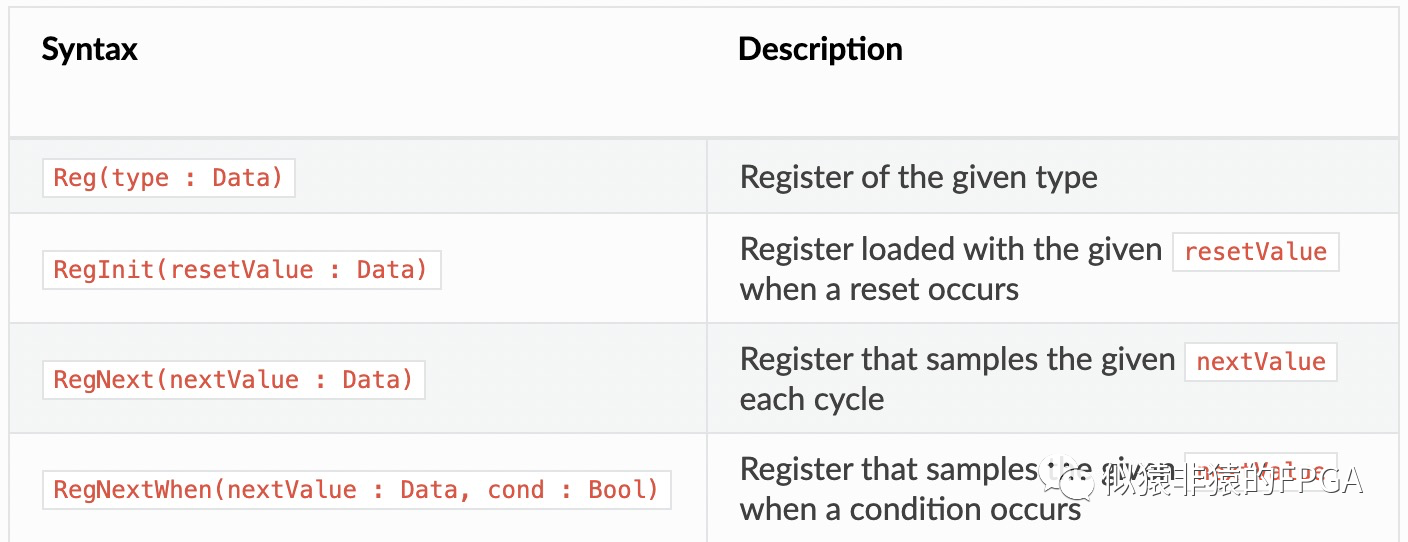

Reg类型变量常用于时序逻辑,在SpinalHDL中,将数据类型声明为Reg类型的方式有:

SpinalHDL提供了四种类型声明寄存器的方式,根据不同的场景需求,我们可以四选一选择最合适的(都是基于Reg一步步封装的)。

除此之外,由于SpinalHDL中默认为Wire类型,而SpinalHDL为其都提供了setAsReg()方法来标注为寄存器类型,同时提供Init(resetValue)方法来做初始化。因此想上面的那个例子我们想寄存器打一拍我们可以这么来写:

case class regDemo() extends Component{

val io=new Bundle{

val dataIn=in UInt(8 bits)

val dataOut=out UInt(8 bits)

}

val regTemp=Reg(UInt(8 bits)) init(0)

regTemp:=io.dataIn

io.dataOut:=regTemp

}

也可以这么来写:

case class regDemo() extends Component{

val io=new Bundle{

val dataIn=in UInt(8 bits)

val dataOut=out UInt(8 bits)

}

val regTemp=RegInit(U(0,8 bits))

regTemp:=io.dataIn

io.dataOut:=regTemp

}

还可以这么写:

case class regDemo() extends Component{

val io=new Bundle{

val dataIn=in UInt(8 bits)

val dataOut=out UInt(8 bits)

}

io.dataOut:=RegNext(io.dataIn).init(0)

}

甚至可以这么写:

case class regDemo() extends Component{

val io=new Bundle{

val dataIn=in UInt(8 bits)

val dataOut=out UInt(8 bits) setAsReg() init(0)

}

io.dataOut:=io.dataIn

}

时序调整很容易

在我们编写RTL代码时,当时序存在问题时需要我们调整时序时是很痛苦的,因为无论是Verilog还是SystemVerilog代码,在较长组合逻辑之间添加一级寄存器往往需要改动较多的点,还需要仔细的评估。稍不注意就是时序没调整好,功能先出问题了(主要在于代码太长,更改需慎之又慎)。

而在SpinalHDL里,时序调整可以做到简洁而优雅。

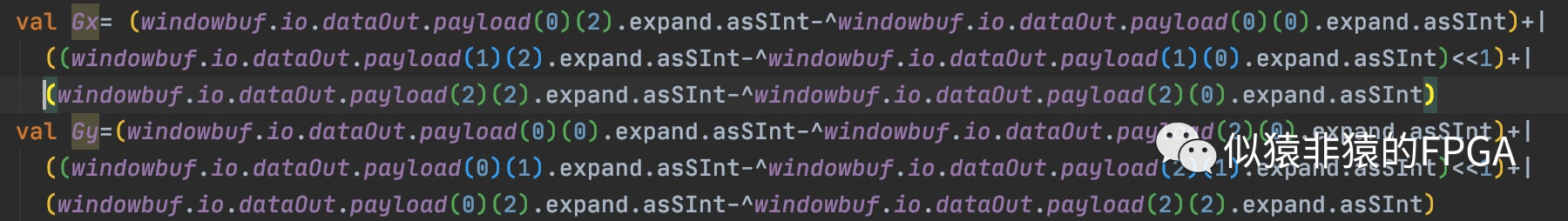

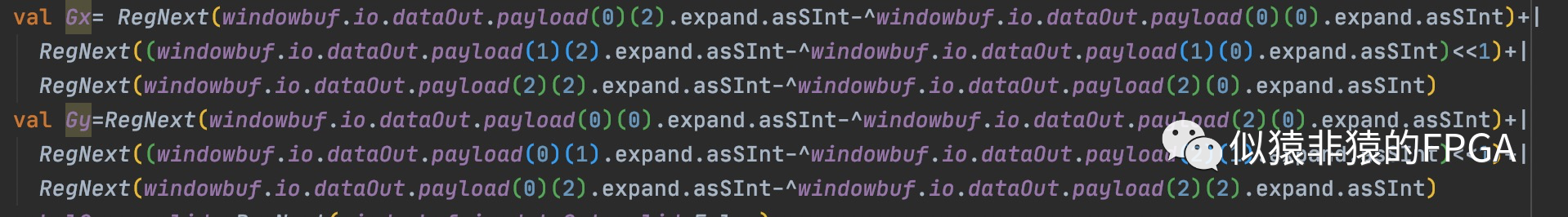

在我们之前用SpinalHDL做Sobel图像处理算法时有这么一段代码:

在卷积核计算处理时这里存在较多的组合逻辑延迟,会成为系统时序瓶颈点。当我们想向更高的频率去跑时这里便需要插入寄存器。想想看这里如果是用Verilog来写时我们插入寄存器不仅要计算清楚中间寄存器的位宽,同时也需要改多行代码,还要小心翼翼的改写。

而在SpinalHDL里,我们这里插入寄存器调整时序很容易!我们可以通过调用regNext很容易地插入一级寄存器:

如此我们便可以轻松地优化时序,谁还说时序调整是个体力活儿呢???

而针对带握手信号的时序打拍优化,SpinalHDL也有相关的Lib供调用可以快捷地优化处理。

END

作者:玉骐

原文链接:https://mp.weixin.qq.com/s/eIQ0Z-JVdbCWlULcbpkpJQQ

微信公众号:

推荐阅读

更多SpinalHDL技术干货请关注Spinal FPGA专栏。