倘若用SpinalHDL写完代码后需要用Verilog/SystemVerilog来进行验证,那将是一件痛苦的事情。

仿真设计不分家

对于数字电路逻辑设计而言,设计与仿真往往是紧密结合的。在SpinalHDL里,当我们的设计完成后如果说把生成的Verilog/SystemVerilog代码用SystemVerilog来进行仿真验证那真是一件痛苦的事情,而且对于SystemVerilog本身来讲,在一些比较贴合具体业务场景的测试条件下往往需要前后很多脚本或调用C模型来进行生成测试数据和最后的数据验证,构建case的便捷性上稍显不足(在《FPGA图像处理—老细新说》一文中,这里的仿真测试如果用SystemVerilog来搭建的化前后数据的处理还是蛮麻烦的)。

由于SpinalHDL是基于Scala的,而这种更高层的语言在case的构建上占据很大优势,也因此SpinalHDL对仿真的支持也更加丝滑。

SpinalHDL是如何让仿真跑起来的

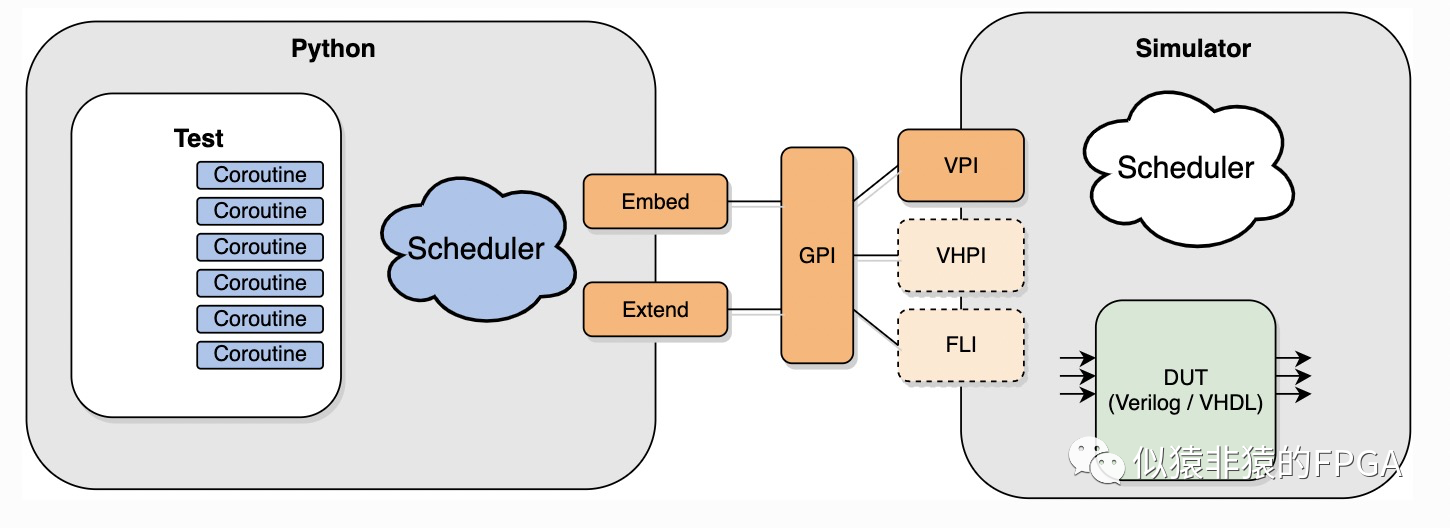

SpinalHDL的开发环境下,我们的逻辑设计和仿真代码均是基于SpinalHDL(Scala)来进行的,但仿真的运行依旧离不开仿真器的支持。在进行仿真时,SpinalHDL会将的逻辑设计转换成Verilog代码,然后将Verilog代码交给仿真器去编译生成可执行二进制文件。而我们由Scala编写的测试代码则会调用仿真器的VPI接口与设计逻辑进行数据交互,其模型与基于Python的cocotb类似(只不过左侧是Scala代码):

有一点先进行说明,类似我们在Verilog/SystemVerilog的测试代码中多个initiial或者fork其多个进程,我们在SpinalHDL的测试代码里也可以起多个,不过其为协程。SpinalHDL的仿真库已经帮我们封装好了底层协程的处理,两个协程之间的通信(类似systemVerilog中的mailbox)我们可以直接用队列即可而无需使用scala中的用于进程间通信的队列数据类型。

目前SpinalHDL仅支持了Verilator、IVerilog等开源仿真器,对于VCS、Modelsim等EDA工具尚未进行集成。在进行FPGA开发时当我们的代码里封装了厂商的IP时因而目前尚无法进行仿真(主要是FPGA厂商目前对这些开源仿真器尚不提供支持),因而如果是这种场景,使用cocotb是一个不错的选择。

仿真环境搭建

SpinalHDL仿真环境的搭建(SpinalHDL设计环境的搭建参考《SpinalHDL-环境搭建》) 需要:

- 仿真器:Verilator。

- 波形查看器:gtkWave 。

在SpinalHDL—Doc里,已经给出了Linux和Windows下的仿真环境安装,可直接参考(主要是我没有这两个环境……),而在Mac OS下,建议通过homebrew进行安装(可参照“原文阅读里的连接安装homebrew”)。

brew install verilator

#安装完成后运行verilator --version

verilator --version

Verilator 4.036 2020-06-06 rev v4.034-208-g04c0fc8aa

gtkwave的安装则可通过homebrew或者从网上直接下载二进制可执行文件即可。

安装好verilator后我们即可在IDEA下直接运行仿真(IDEA这种软件环境单步调试简直不要太爽),SpinalHDL会自动调用verilator,我们无需做额外工作。

写在最后

本篇简单总结下SpinalHDL中的测试环境,后续陆续对SpinalHDL仿真库的使用进行梳理归纳。

END

作者:玉骐

原文链接:https://mp.weixin.qq.com/s/jUJPPCbcTYMWWjW4qSgSlw

微信公众号:

推荐阅读

更多SpinalHDL技术干货请关注Spinal FPGA专栏。