我们在实现FPGA逻辑电路时,时常会在Verilog代码里添加一些约束原语,本文就SpinalHDL里如何给电路添加约束标签进行说明。

前言

我们在描述FPGA电路时,我们经常会在电路里添加一些像这样的约束原语:

(* ram_style = "ultra" *) reg [520:0] ram [0:1023];

(*mark_debug=true*) reg sig;

通过这种方式,我们可以指导FPGA在综合及布局布线时的动作,当切换到SpinalHDL来描述电路时,身为一门优秀的HDL,怎能不支持这种约束标签的添加呢。

约束语法

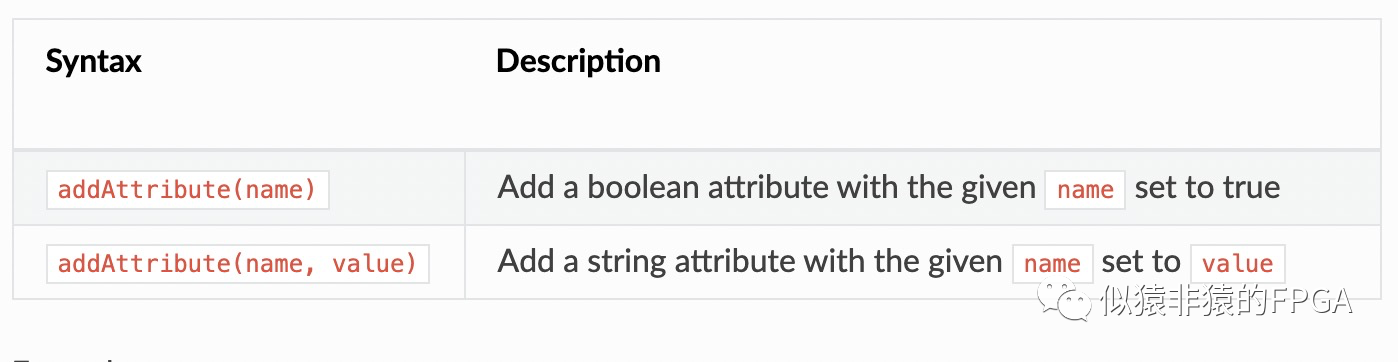

在SpinalHDL里,为方便给RTL添加约束属性,SpinalHDL里提供了下面两个方法:

通过addAttribute方法,我们可以对信号,Mem进行属性添加,最终在生成Verilog时相应的会添加到对应的信号上。

Example

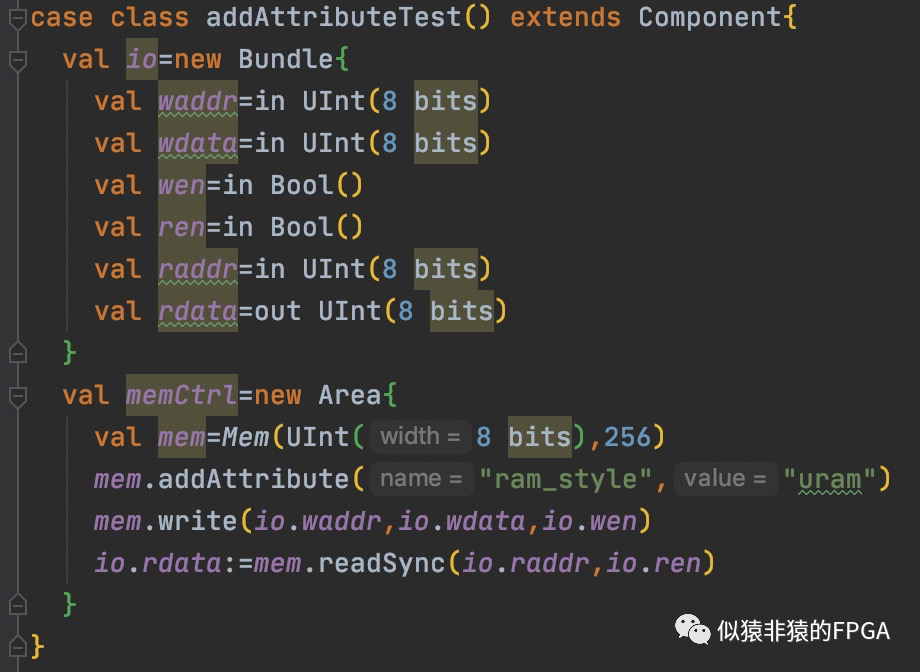

这里我们以Mem为例,建立一个简单的Ram读写Demo:

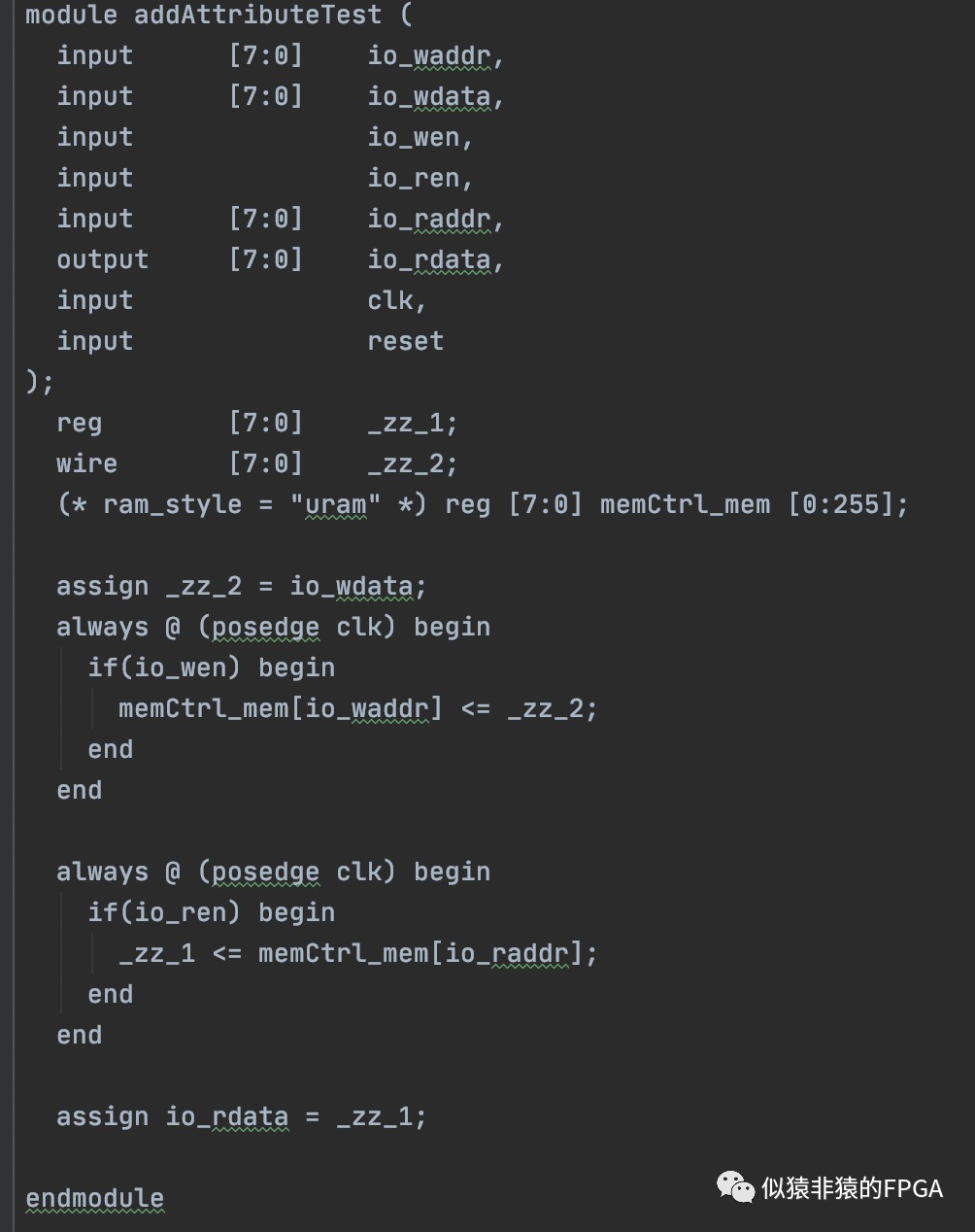

如代码中所述,我们在这里给mem添加约束属性ram_style,要求在实现时用uram来实现。对应生成的Verilog文件如下所示:

在生成的Verilog代码里我们可以看到,memCtrl_mem添加了我们想要的约束,这个我们在手写Verilog代码时的效果是一样的。

END

作者:玉骐

原文链接:https://mp.weixin.qq.com/s/AfMiXoIoVDRRm09a3xGd1A

微信公众号:

推荐阅读

更多SpinalHDL技术干货请关注Spinal FPGA专栏。