书接上文,与诸君共看如何在SpinalHDL里启动一个仿真。

前言

在安装完成Verilator、GtkWave后,我们即可在IDEA里通过SpinalHDL提供的仿真接口来对我们的设计进行仿真。在《SpinalHDL—仿真环境》一文中已提到SpinalHDL下仿真的原理,尽管我们仿真对象是我们的SpinalHDL代码生成Verilog文件交给仿真器去执行但我们的仿真环境搭建和case构建可以借助scala语言本身丰富的软件库来进行构建,这是我们用SystemVerilog进行仿真所无法替代的(一堆脚本亦或是调用C),而且我们在仿真过程中是无须关心生成的Verilog,追踪的波形都是我们在SpinalHDL中定义的电路对象,更遑论像IDEA这类软件调试工具单步调试的便捷性了。所以这种“高层次”仿真,还是值得一用。

启动仿真的方式

SpinalHDL中的仿真入口一般情况下都是这么来写的:

import spinal.core.sim._

object DutTests {

def main(args: Array[String]): Unit = {

SimConfig.withWave.compile(new TopLevel).doSim{ dut =>

// Simulation code here

}

}

}

- 通过引入spinal.core.sim._ ,我们可以使用SpinalHDL已经集成好的接口来搭建仿真环境。

- SimConfig用于配置仿真环境参数。

- doSim里构建仿真环境及测试case。

SimConfig里的参数配置可分为三类:

- 仿真环境配置。

- DUT配置及编译。

- 仿真启动。

仿真环境配置

仿真环境的配置主要包含仿真器的选择,波形文件生成、覆盖率生成等参数配置,每个参数配置项在SpinalHDL中均封装成一个函数。这里以常用的选项进行说明(详细的参数配置可参见源码)。

- 仿真器选择:目前支持verilator、ghdl、Iverilog。对应的函数为withVerilator、 withGhdl、withIVerilog。默认为withVerilator。

- 波形类型:withWave、withWave(Int)。默认生成VCD波形文件,可指定抓取波形信号的层级深度。

- 覆盖率收集:该功能在1.4.2版本支持,通过withCoverage使能。

DUT配置及编译

DUT的配置通过withConfig(config: SpinalConfig)函数进行配置。这里的配置常用的是对时钟域的配置,包含时钟有效边沿、复位信号类型、时钟频率等。如下例所示:

SimConfig

.withWave

.withConfig(SpinalConfig(

defaultClockDomainFrequency = FixedFrequency(100 MHz),

defaultConfigForClockDomains = ClockDomainConfig(resetKind = SYNC)))

而DUT的编译则通过compile函数执行:

SimConfig

.withWave

.withConfig(SpinalConfig(

defaultClockDomainFrequency = FixedFrequency(100 MHz),

defaultConfigForClockDomains = ClockDomainConfig(resetKind = SYNC)))

.compile(new addInstSim(8))

仿真启动

仿真启动

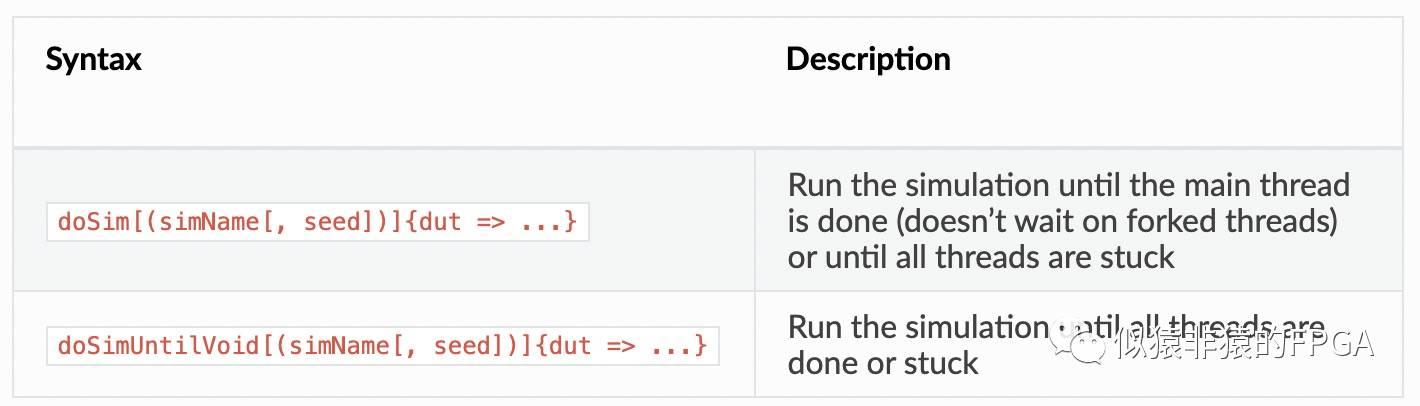

仿真的启动可调用两个函数:

个人常用doSim。仿真启动默认会采用随机种子,也可以指定仿真种子。而这里dut(你也可以用名字)表示待测试逻辑,通过dut我们可以访问和驱动待测试逻辑的信号:

SimConfig

仿真启动,你会在控制台看到仿真的启动:

[Runtime] SpinalHDL v1.4.2 git head : 804c7bd7b7feaddcc1d25ecef6c208fd5f776f79

可以看到,仿真的启动首先会将DUT编译生成Verilog文件,随后交由Verilator进行编译,随后选择一个随机种子启动仿真。

写在最后

本篇就SpinalHDL中的仿真启动进行简短说明,后续将继续对时钟和信号的驱动和访问进行说明。

END

作者:玉骐

原文链接:https://mp.weixin.qq.com/s/golzadgIUVvHBAM2hxFkeQ

微信公众号:

推荐阅读

更多SpinalHDL技术干货请关注Spinal FPGA专栏。