无论是做SOC设计还是FPGA设计,AXI4总线是经常提及的。本系列以AXI4总线为例,来看下在SpinalHDL中AXI4总线互联IP的设计。

关于AXI4总线

关于什么是AXI4总线的定义,网络上相关的文章不胜枚举,也是无论是做FPGA还是ASIC都是必须要了解和掌握的知识,这里不做过多的讲解(小伙伴可以自行下载AMBA总线协议规范或者翻看网络上AXI4总线协议相关文章)。在SpinalHDL中,关于Axi4总线,包含了配置和实现两块内容,其内容均在spinal.lib.bus.amba.axi4 package中。

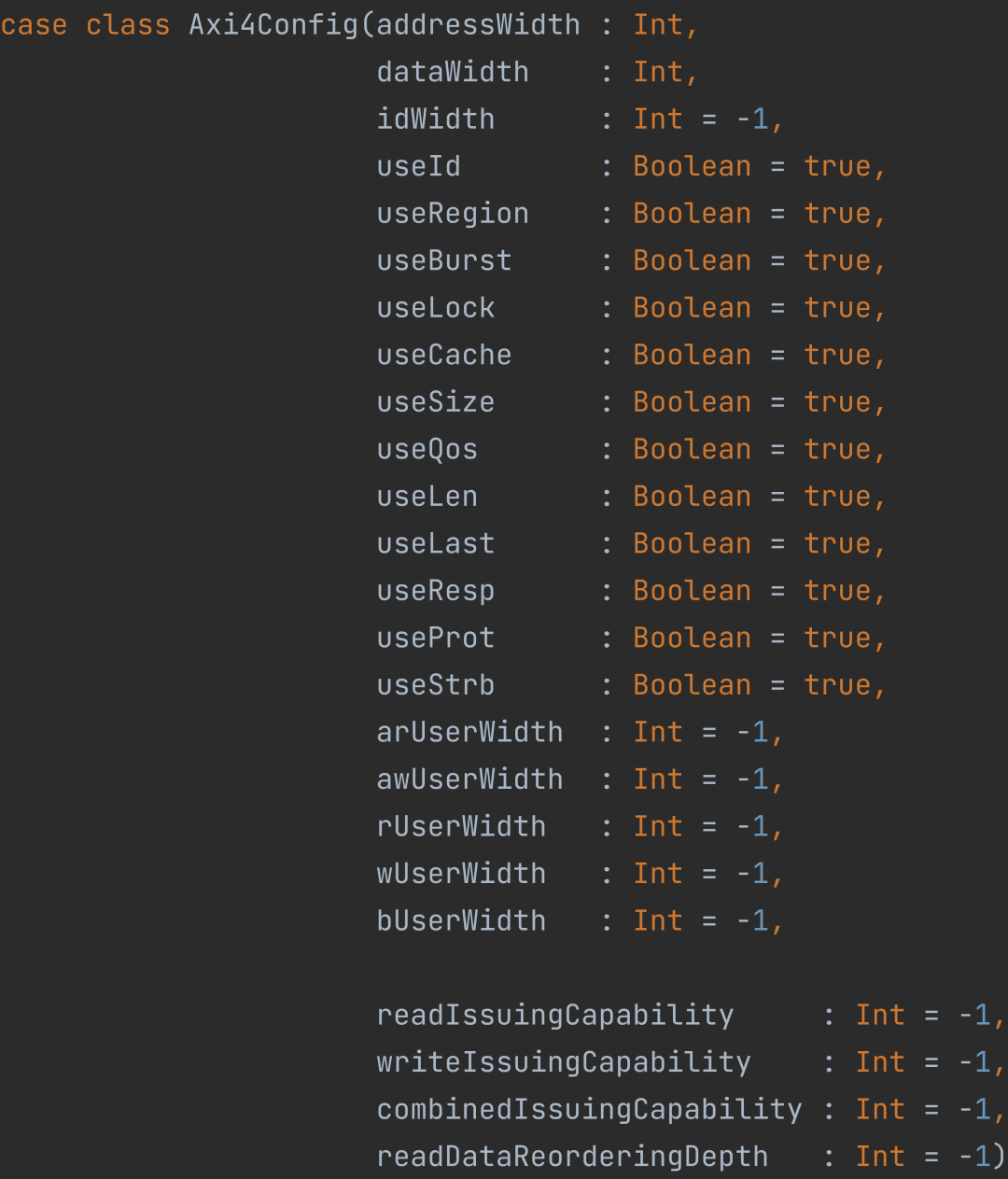

Axi4总线配置:

这里结尾的四个参数值的注意:

- readIssuingCapability:指明AXI4总线读最大支持的指令个数。

- writeIssuingCapability:指明AXI4总线写最大同时支持的指令个数。

- combinedIssuingCapability:其值应不小于前两者,用于在AXI4总线读写地址通道共用的场景。

- readDataReorderingDepth:读乱序传输的深度。

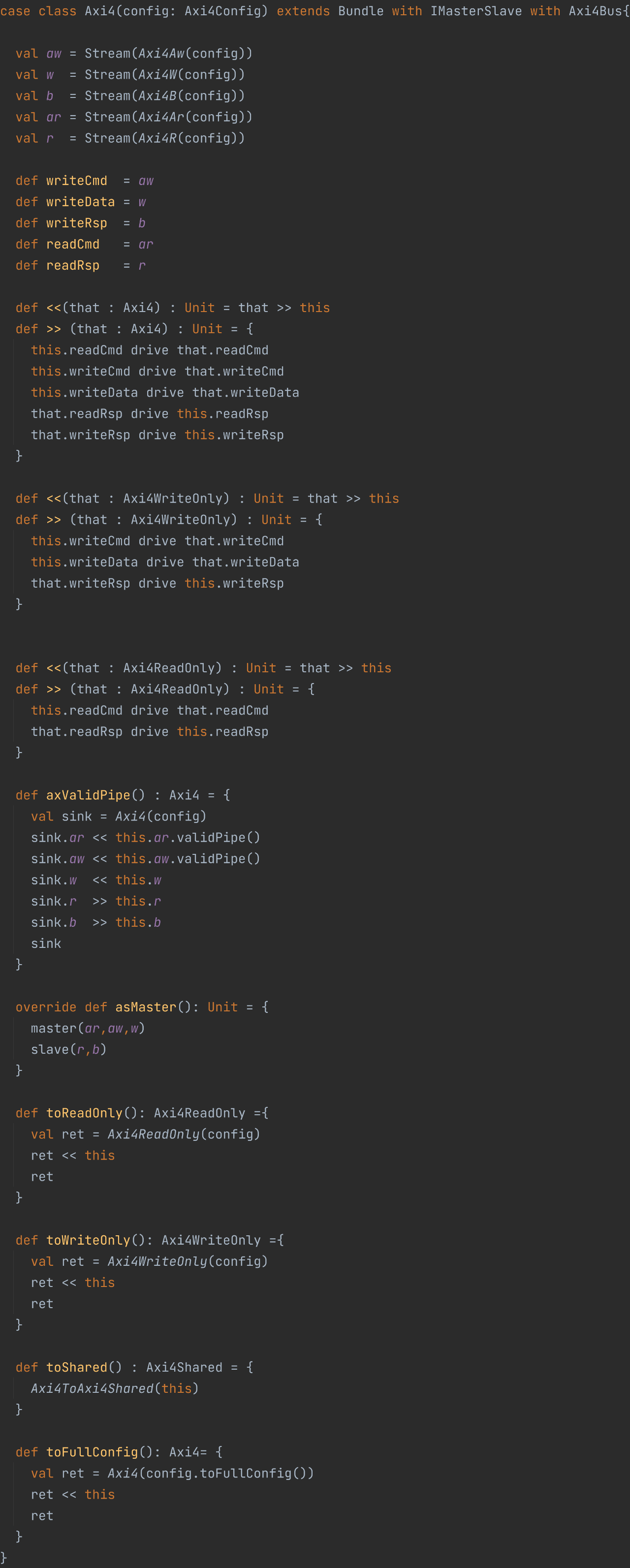

AXI4总线定义为:

AXI4总线定义划分为五个Strema通道:aw,w,b,ar,r。

除了Axi4总线的定义,在SpinalHDL还另外定义了一些Axi4总线的接口变种:

- Axi4WriteOnly:只有Axi4总线写通道(aw,w,b)的接口。

- Axi4ReadOnly:只有Axi4总线读通道(ar,r)的接口.

- Axi4Shared:Axi4读写地址通道(aw,ar)共用一组信号的接口(arw,w,b,r)。

关于总线互联的设计

凡是设计中用到Axi4总线的设计总离不开总线互联。在Xilinx FPGA使用中,VIvado针对Axi4总线提供了丰富的IP,对于设计带来了不少设计的便利性。然而在Intel系列FPGA中,其推崇自家Avalon总线,相关IP也不尽完善。当我们的设计从一家平台迁移到另一家平台时,便存在严重的设计兼容性问题,况且Xilinx IP对我们来讲属于黑盒,对于了解其设计背后的思想也难以入手。

而在SpinalHDL中针对Axi4总线互联也有相应的实现。不妨以此为蓝本,来学习下其背后设计的思路。

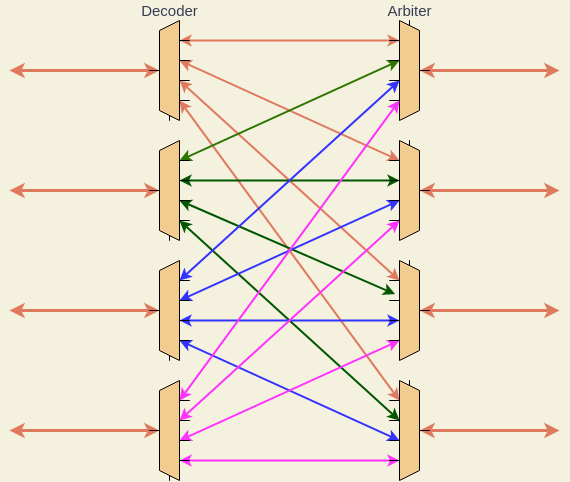

总线互联的逻辑从整体层面上来看并不复杂,其整体上可分为Decoder,Arbiter两大部分:

对于每个slave端口,其在整个互联系统上都会分配一段地址,在互联系统中通过对地址的译码来进行数据流的路由:

- Decoder:负责地址的译码。

- Arbiter:负责进行多路端口的仲裁。

再聚焦到Axi4协议本身,那我们面临的问题就相对来讲比较多了。在Axi4总线中,无论是读还是写,都需要多个通道的协作才能完成,而这其中便牵涉到了诸多问题:

- Decoder,Arbiter做通道切换的契机选择?

- 若master端读写访问地址均没有命中任何一个slave端口的处理?

- readIssuingCapability,writeIssuingCapability如何支持?

- Arbiter 如何将b,r通道数据路由至正确的端口?

除此之外,针对总线互联这种IP,如何做成参数化的形式在Verilog中也是一个不小的挑战。后续就上述问题来解析SpinalHDL中的设计实现。

☆ END ☆

作者:玉骐

原文链接:https://mp.weixin.qq.com/s/r2k_Y0wwKlkJxlrjtnBGhg

微信公众号:

推荐阅读

更多SpinalHDL技术干货请关注Spinal FPGA专栏。