本文主要介绍各种类型的跨时钟域问题。同步时钟是指具有已知相位和频率关系的时钟。这些时钟本质上是来自同一时钟源。根据相位和频率关系,可分为以下几类:

具有相同频率和零相位差的时钟

具有相同频率和固定相位差的时钟

具有不同频率和可变相位差的时钟

整数倍时钟

非整数倍时钟

具有相同频率和零相位差的时钟

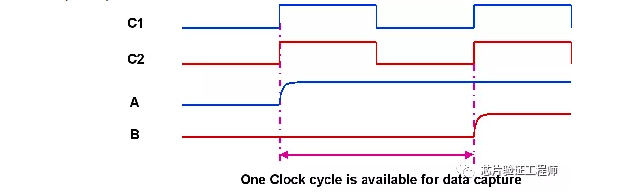

时钟C1和C2具有相同的频率和0相位差。由于此时时钟C1和C2是相同的,并且由相同的时钟源产生,因此从C1到C2的数据传输本质上不是跨时钟域。每当数据从时钟C1传输到C2时,一个C1(或C2)时钟周期就可以完成数据采样,如下图所示。

只要源时钟触发器和目的时钟触发器之间的组合逻辑延迟能够满足电路的setup和hold时间,数据就会正确传输。这里唯一的要求是设计应进行过时序clean,即STA(静态时序分析)。在这种情况下,将不会存在亚稳态、数据丢失或数据不一致性的问题。

具有相同频率和固定相位差的时钟

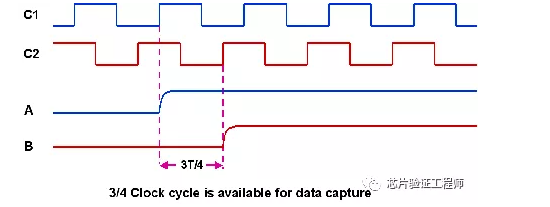

如下图所示时钟C1和C2具有相同的频率,但发生相位偏移,C1领先C2 3T/4时间单位。

每当数据从时钟C1传输到C2时,由于setup/hold margin较小,对组合逻辑延迟有更严格的要求(setup或者hold )。如果数据传输处的setup/hold时间满足要求,数据将被正确地传输,并且不存在亚稳态。在这种情况下也不需要同步器,唯一的要求是设计STA clean。

具有不同频率和可变相位差的时钟

这里可以有两个子类别:

1、一个时钟的时钟周期是另一个时钟的整数倍(奇数倍和整数倍)

2、一个时钟的时钟周期是另一个时钟的非整数倍。

在这两种情况下,时钟边沿之间的相位差可以是可变的。

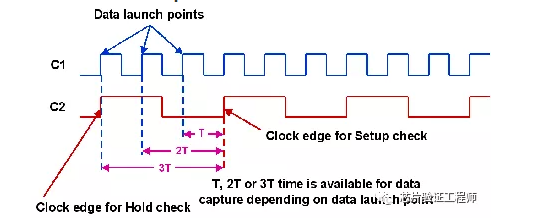

整数倍时钟

在这种情况下,一个时钟的频率是另一个时钟的奇数倍,它们边沿之间的相位差是可变的。下图中2个时钟边沿之间的最大相位差等于快速时钟的时间周期。时钟C1比时钟C2快3倍。假设T是时钟C1的时钟周期,时钟C2采样到的数据可能来自时钟C1的T、2T或3T时刻数据。在进行静态时序分析时需要针对setup和hold的最差情况。

在上面这种情况下,由慢时钟到快时钟的数据传输只要满足时序,不存在亚稳态或数据不一致,也不需要同步器。然而,在快时钟到慢时钟的情况下存在数据丢失的问题。为了防止这种情况发生,源数据应该至少在一个目标时钟(慢时钟)的周期内保持不变。这可以通过一些控制电路(例如状态机)来保证。在上图的示例中,如果源时钟每3个周期生成一次源数据,则不会出现数据丢失。

非整数倍时钟

在这种情况下,一个时钟的频率是另一个时钟的非整数倍,时钟边沿之间的相位差是可变的。这里考虑两种情况:

第1种情况下,两个时钟的时钟边沿非常近,近到足以导致亚稳态问题。然而,一旦时钟边沿接近,在下一个周期中有足够的时间来适当地捕获数据。在这种情况下,这两个时钟的边沿可以断断续续地结合在一起。

换句话说,时钟边沿一次接合在一起,然后在接下来的几个周期中,时钟边沿之间会有足够的时间以正确地捕获数据。在这里,“近”一词意味着足够近,足以引起亚稳态。

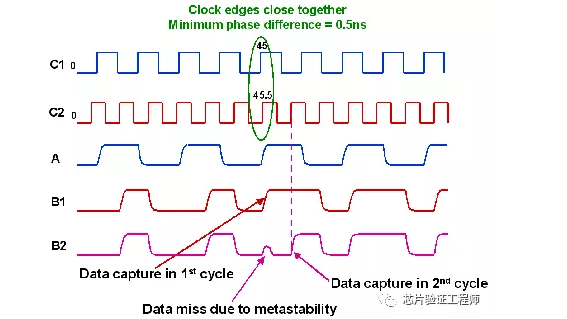

在下图中,时钟C1和C2的时间周期分别为10ns和7ns。由于亚稳态,当时钟边沿非常接近时,可能无法在目标时钟域中捕获数据。然而,在下一个周期中,就可能有足够的时间以便目标时钟可以正确地捕获数据。如下图所示,虽然预期输出是B1,实际波形看起来像B2,但在这种情况下仍然没有数据丢失(当然也不是每一拍都能采到)。

对于快时钟到慢时钟的跨时钟域传输,可能会发生数据丢失,为了防止这种情况发生,源数据应该在至少一个目标时钟周期内保持不变。同样,这可以通过使用一个简单的FSM来实现。

第2种情况下,两个时钟的时钟边沿可以足够接近并且连续多个周期。在这种情况下,时钟之间的相位差有时非常小,并且可以保持几个周期。这与异步时钟非常相似,除了可变相位差是已知的并周期性地重复。

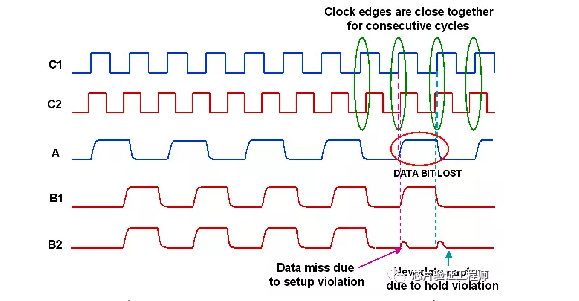

下图中这两个时钟的时钟边沿连续4个周期非常接近。在前2个周期中,有可能出现setup违例,而在接下来的2个周期中,也有可能出现hold违例。

在这种情况下,将存在亚稳态的问题,因此需要进行同步。除了亚稳态之外,还可能存在数据丢失的问题,尽管它是一个慢时钟到快时钟域的传输。上图中,如果没有亚稳态,B1是预期的输出。但是,实际的输出可以是B2。这里的数据值“1”丢失,因为在第一个周期中,值“1”由于setup违例而没有被捕获,而在第二个周期中,新值“0”被错误捕获。

为了防止数据丢失,数据需要在至少两个目标时钟周期内保持不变。这可以通过使用一个简单的FSM来控制源数据的生成来实现。然而,数据不连贯性的问题可能仍然存在。在这种情况下,需要使用握手和FIFO等技术处理数据的不连贯性问题。

异步跨时钟域

没有已知相位或频率关系的时钟被称为异步时钟。异步时钟之间的相位差是可变的,而且不像同步时钟,它是不可预测的。

如果已知源时钟频率和目标时钟频率,则可以通过保持源数据在目标时钟的两个周期内不变来防止数据丢失。如果电路要被设计为独立于时钟频率,则应使用握手或FIFO技术来防止亚稳态、数据丢失和数据一致性问题。

作者:验证哥布林

原文链接:https://mp.weixin.qq.com/s/_9AazglZFVJ-L_PQjyeENg

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏