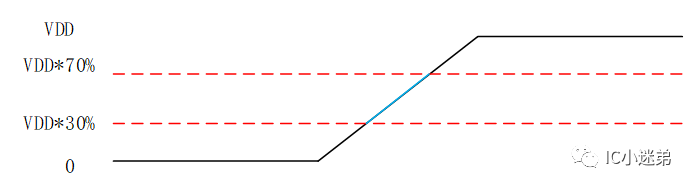

在数字电路的世界里,只有“0”和“1”。但是在实际电路中,信号的变化并不是一瞬间的事情,而是会经过一个上升或者下降时间,如下图。所以人们通常会将小于VDD*30%的电平定义为“0”;同时将大于VDD*70%的电平定义为“1”;而在这两者之间的电平属于不确定区。换句话说,在这个区域内的电平有可能是“0“,也有可能是“1”。

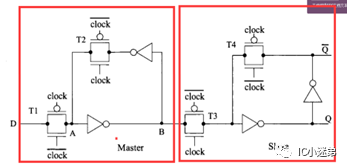

寄存器是由两级锁存器串联而成,如下图。当clock为低电平时,T1和T4打开,T2和T3关闭,此时D只能传到B处,Q端输出的是前一个周期锁存到的值。而当clock由低变高(上升沿)时,T1和T4关闭,T2和T3打开,此时前面一级锁存器将锁存到的D值传到后一级锁存器,并通过Q端输出。所以,在上升沿处,如果D还处于变化状态,那就有可能采到它的不确定区,从而导致寄存器Q端输出不确定态,也就是我们所说的亚稳态。

所以为了保证时序逻辑采样的正确性,就需要数据在时钟沿前后有一个稳定的窗口。那么这个窗口需要多大呢?这时就需要引入setup/hold time的概念:

setup time:时钟沿到来之前,数据必须保持稳定的最小时间。

hold time:时钟沿到来之后,数据必须保持稳定的最小时间。

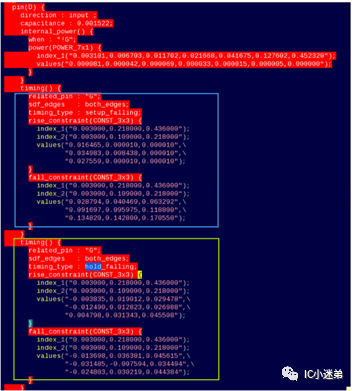

setup/hold time的大小跟器件有关,是器件的特定属性。我们可以在foundry提供的lib中找到相关的值,下图是某工艺库内锁存器D端的setup/hold查找表,其中蓝色方框内为setup time,而绿色方框内为hold time。

原文链接:IC小迷弟

作者:ChaucerG

推荐阅读

更多嵌入式AI技术相关内容请关注嵌入式AI专栏。