写在前面

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.

本文系转载,略做格式调整与增加解释,转自https://blog.csdn.net/weixin_48180416/article/details/116563101

相应内容可参考:

- MindShare,PCI Express System Technology 3.0 第十三章。

- 《PCI Express 体系结构导读》 第八章

转载正文

Recovery.Equalization为Recovery子状态,用于链路均衡。

为了改善High Speed(8GT/s及以上)时的信号质量,加入了Transmitter Equalization。

2.5GT/s和5GT/s仅采用de-emphasis技术。

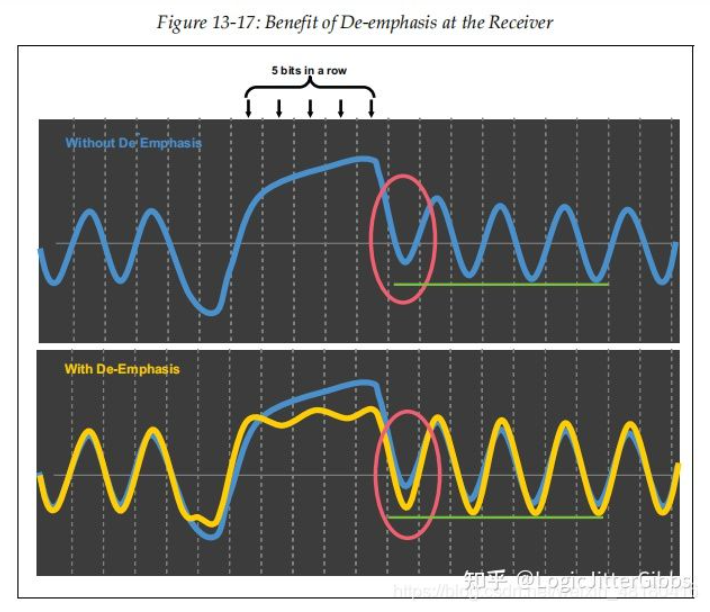

为什么采用de-emphasis?

由于Repeat Bits导致Transimtter Driver连续的Charge up,达到了很高的电压值,当变为0时不能达到预期的电压值,造成码间串扰(ISI)

为了解决这个问题,Repeat Bits时减小电压值,over-charge的问题就会得到改善,这种方法叫做de-emphasis.

在2.5GT/s时选择固定的去加重de-emphasis -3.5dB, 5GT/s时选择选择de-emphasis -6dB(当支持5GT/s的设备工作于2.5GT/s采用-3.5dB)

8GT/s及以上---de-emphasis, preshoot, boost

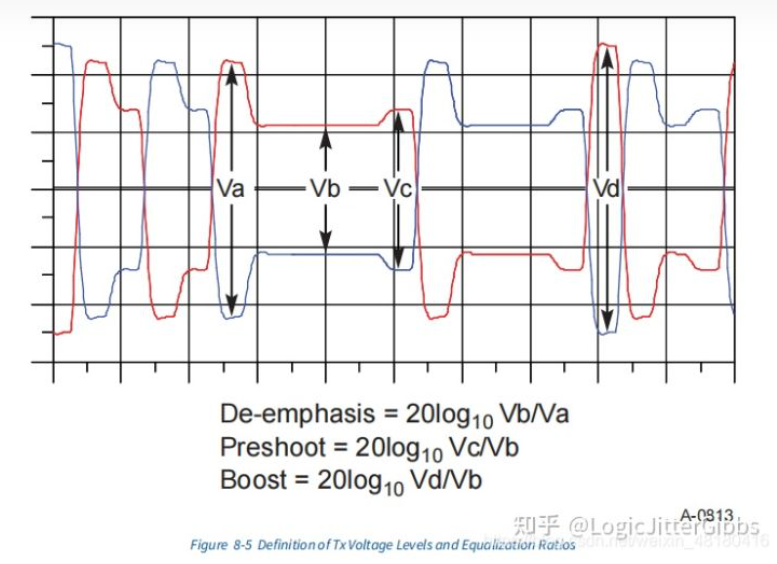

如上图所示,当8GT/s及以上速率时,除了De-emphasis外还有两个Preshoot和Boost参数

- De-emphasis发生于repeat bits的第一个bit,是指非跳变bit比跳变bit幅度减小,减小的幅度叫做De-emphasis

- Preshoot发生于repeat bits的最后一个bit, 是指跳变bit的前1个bit也要增大幅度,这个增大的幅度通常叫做Preshoot

- Boost发生在0->1->0或1->0->1这样的码型。

从上面的原理可以看出,EQ的本质是在调节Transmitter的电压,具体如何调节电压呢?

FFE 滤波器调节电压

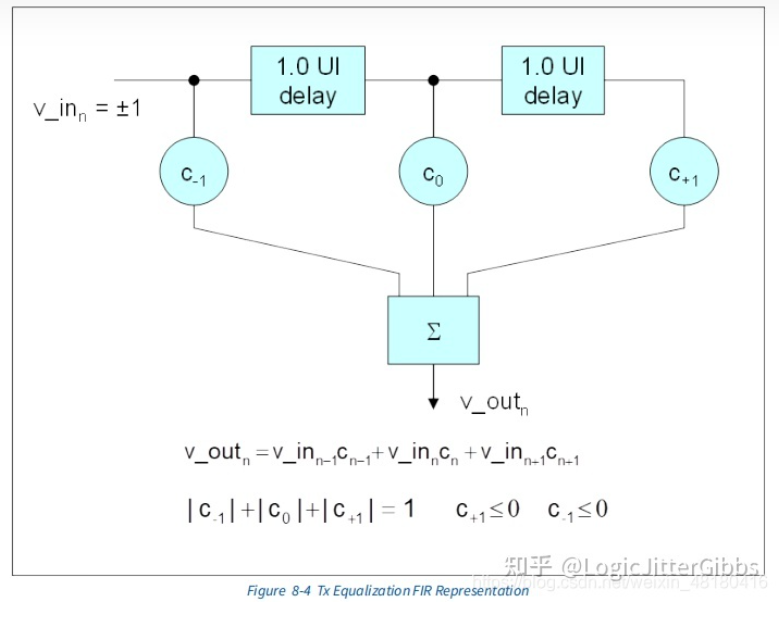

Transmitter内部有一个三阶的前向反馈滤波器(FFE),如下图:

滤波器有三个系数,Pre-Cursor(C-1), Current Cursor(C0), Post-Cursor(C+1)

这三个系数决定了Transmitter的各个码型的电压,EQ的过程实际上是在调节FFE的这三个系数。

从上面的原理可以看出,EQ的本质是在调节FFE的系数,具体如何调节系数呢?

有两种方法:

一种是调整Preset, 是最常用的方法,是粗调,耗时短。

使用预置系数 Preset 调整 EQ 系数

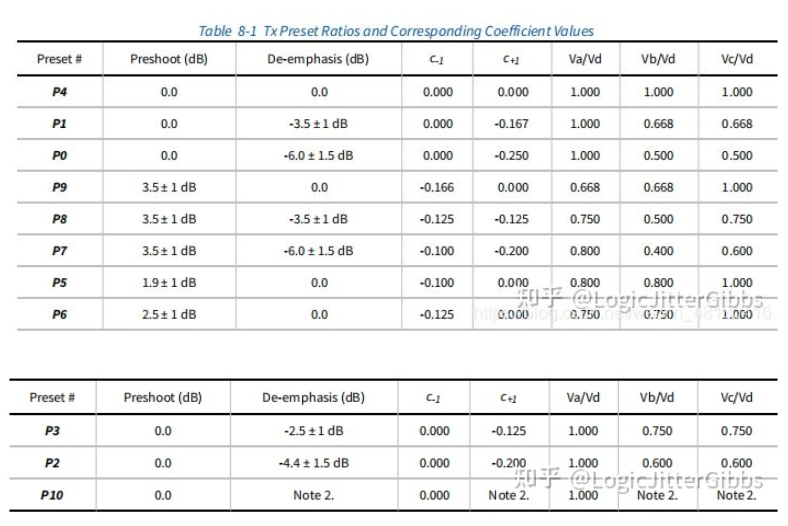

PCIe Spec规定了11套预置的系数,称为Preset 0-10,每一个Preset对应一套系数。

实际应用中Tx和Rx端可以在Link EQ阶段根据接收端收到的信号眼图质量协商出一个最优的Preset值。

下图是11种Preset的组合,比如P4代表没有任何去加重,P7代表最厉害的去加重。

Spec中没有规定Preset Request评估的具体方法, 仅以Synopsy IP为例,采用FOM Mode,调节的具体过程是:

- Transmitter选择一个初始的Preset,Receiver记录Initial Preset对应的眼图质量;

- Transmitter遍历所有支持的Preset, Receiver记录每个Preset对应的眼图质量;

- Transmitter应用眼图质量最好的Preset

注:通过PHY层评估眼图的质量。

另外一种是直接调整系数,是精调,耗时长,可能最终不会收敛。

直接调整 EQ 系数

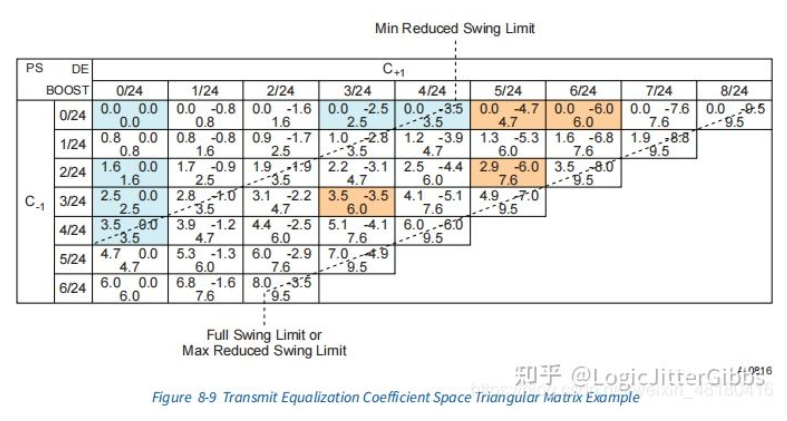

- 直接调节系数是有电压范围的,根据电压是Full Swing(全摆幅)还是Reduced Swing(降低摆幅) ,Boost不能超过3.5dB/9.5dB,

- 每次调节的分辨率(最小步长)为1/24

Spec中没有规定Coefficient Request评估的具体方法, 仅以Synopsy IP为例,采用DIR Mode,调节的具体过程是:

- 选定最优的Preset后,Receiver PHY对系数评估,反馈C+1/C-1需要加1还是减1还是保持不变

- 当系数收敛的时候就会停止调节,收敛有两种:

- 所有的Lane的C+1 C-1都反馈需要保持不变,这个需要很久的时间,通常很难做到;

- 另外一种是配置一个delta值, 当C+1/C-1的波动小于这个delta值就会停止调节,认为是收敛的。

上述系数调节的时候是不需要调节C0的,因为C-1、C0、C+1是有固定关系的。

FFE 系数规则

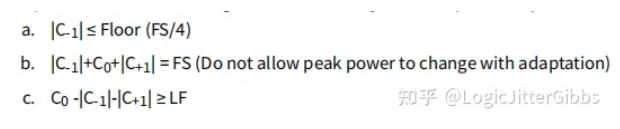

无论是Preset调节还是系数调节必须满足以下规则

Floor是向下取整。FS(Full Swing)最大的电压值,LF(Low Frequency)代表最小的电压值。

FS定义了系数的和,FS的范围如下:

FS ∈ {24, …, 63} (i.e., FS must have a value from 24 through 63) for full swing mode.

FS ∈ {12, …, 63} for reduced swing mode.

版权声明

版权声明:本文为CSDN博主「小雨滴落落」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:PCI Express学习篇---物理层LTSSM(二) Recovery.Equalization基础知识

转载自:知乎

作者:小雨滴落落

推荐阅读

- PCI Express 学习篇_物理层 LTSSM(1):Recovery 子状态介绍

- 国密标准IPsec VPN协议处理及其密码IP设计与FPGA实现(2)

- 国密标准IPsec VPN协议处理及其密码IP设计与FPGA实现

更多招聘及面经请关注FPGA的逻辑。