0 I2C介绍

权威官网

https://www.i2c-bus.org/

I2C 总线规范是由飞利浦半导体编写的。这家公司后来成为 NXP Semiconductors,现在它是 I2C 总线规范的维护相关者。

不幸的是,最近的 I²C 总线规范,NXP 文档版本 6.0,2014 年 4 月 4 日不再在 NXP 站点上公开。它位于

https://www.nxp.com/docs/en/user-guide/UM10204.pdf

或者登录后下载:

https://www.nxp.com/webapp/Download?colCode=UM10204&location=null.

History of the I2C Bus

https://www.esacademy.com/en/library/technical-articles-and-documents/miscellaneous/i2c-bus/general-introduction/history-of-the-i2c-bus.html

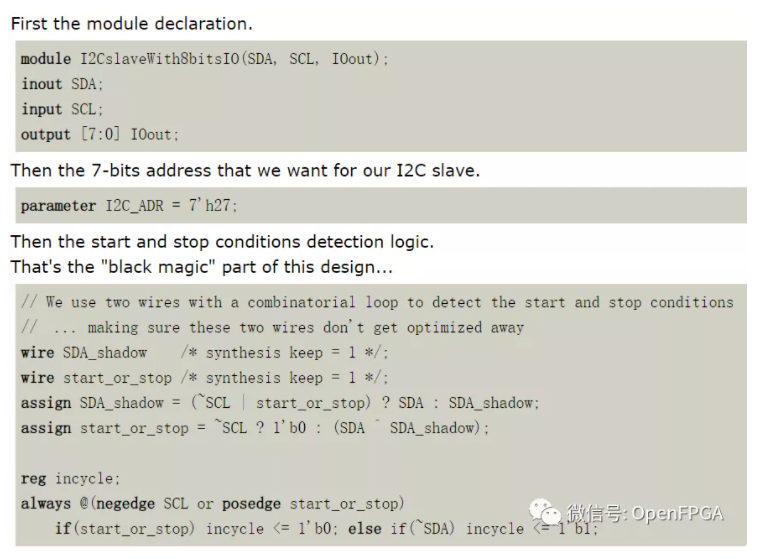

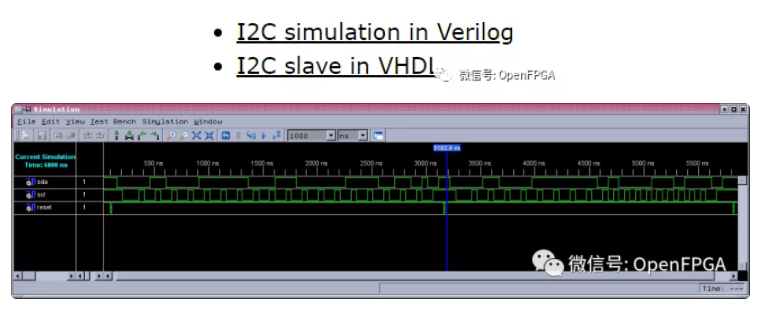

1 fpga4fun上的I2C

https://www.fpga4fun.com/I2C_2.html

详细的设计过程:

完善的仿真程序:

2 alexforencich的verilog-i2c

https://github.com/alexforencich/verilog-i2c

alex的项目无需多说,他的网络和PCIe都是完成度等方面首屈一指。

我们先看下这个项目包含哪些文件:

axis_fifo.v : AXI stream FIFO

i2c_init.v : Template I2C bus init state machine module

i2c_master.v : I2C master module

i2c_master_axil.v : I2C master module (32-bit AXI lite slave)

i2c_master_wbs_8.v : I2C master module (8-bit Wishbone slave)

i2c_master_wbs_16.v : I2C master module (16-bit Wishbone slave)

i2c_slave.v : I2C slave module

i2c_slave_axil_master.v : I2C slave module (parametrizable AXI lite master)

i2c_slave_wbm.v : I2C slave module (parametrizable Wishbone master)i2c_init module

通过 I2C 进行外设初始化的模板模块。当一个或多个外围设备(即 PLL chips, jitter attenuators, clock muxes,PLL 芯片、抖动衰减器、时钟多路复用器等)需要在上电时初始化而不使用通用处理器时使用。

i2c_master module

带有 AXI 接口的 I2C 主模块。

i2c_master_axil module

具有 32 位 AXI lite 从接口的 I2C 主模块。

i2c_master_wbs_8 module

带有 8 位 Wishbone 从接口的 I2C 主模块。

i2c_master_wbs_16 module

带有 16 位 Wishbone 从接口的 I2C 主模块。

i2c_slave module

带有 AXI 接口的 I2C 从模块。

i2c_slave_axil_master module

带有参数化 AXI lite 接口的 I2C 从模块。

i2c_slave_wbm module

带有可参数化 Wishbone 主接口的 I2C 从模块。

3 opencores i2c

https://opencores.org/projects/i2c

https://opencores.org/projects/i2c_master_slave_core

https://opencores.org/projects/i2cslave

https://github.com/trondd/oc-i2c

特征

- Both Master and slave operation

- Both Interrupt and non interrupt data-transfers

- Start/Stop/Repeated Start generation

- Fully supports arbitration process

- Software programmable acknowledge bit

- Software programmable time out feature

- programmable address register

- Programmable SCL frequency

- Soft reset of I2C Master/Salve

- Programmable maximum SCL low period

- synthesis core

综合结果

各种目标的按钮合成结果。

A54SX16ATQ100-std:352Modules@58MHz

FLEX : EPF10K50ETC144-3: 294LCELLs@82MHz

ACEX : EPF20K30ETC144-3: 257ATOMs@74MHz

Spartan-II:2S15CS144-5:229LUTs@82MHz

Virtex-E:XCV50ECS144-8:230LUTs@118MHz

4 freecores i2c

https://github.com/freecores/i2c

https://github.com/freecores/i2cslave

虽然没有详细的 文档,但是整个项目还是很完整的,I2C整个逻辑也不复杂即使没有文档,使用这个项目也不是难事。

5 hhping i2c_code

https://github.com/hhping/i2c_code

这套I2C代码已经经过板上验证。在九州探测器版验证过通过。

6 BNUGYX Verilog_i2c_eeprom

https://github.com/BNUGYX/Verilog_i2c_eeprom

https://github.com/mcgodfrey/i2c-eeprom

I2C通信实现eeprom读写

先写入固定字符,再读出此字符,显示在数码管上

7 splinedrive i2c_sdd1306_framebuffer

https://github.com/mcgodfrey/i2c-eeprom

这是一个基于 fpga 的 i2c ssd1306 oled 设计!它包含一个 i2c 主控、帧缓冲区、字体渲染单元、rx 单元......

只需将 115200 波特的数据通过串口发送到 fpga,这些字符就会显示在 oled 上!

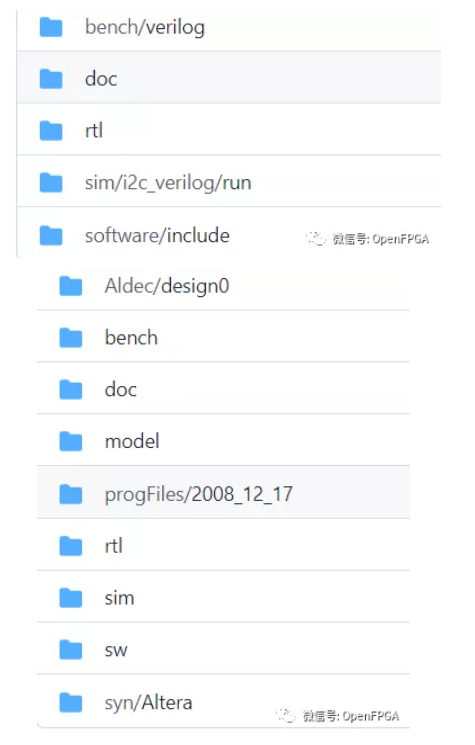

8 tmatsuya i2c_edid

https://github.com/tmatsuya/i2c_edid

用于 EDID(扩展显示识别数据)IP CORE 的 I2C ROM

说明

- 该项目是使用 I2C DDC 协议将显示模式传输到视频源的目标设备。

- 适用于 HDMI 相机捕获设备或视频切换器开发人员

特点

- 支持 I2C 从机协议和 EDID(扩展显示识别数据)ROM

- 8 位寻址(最大 256 字节)

目录结构

/boards/ 顶层设计文件、约束文件和 Makefiles /cores/ 核心库 /software/ 软件和数据文件

总结

I2C相关的开源项目很多很多,很多大佬独立写个I2C总线应该是很容易,头两个项目是使用最常见的项目,无需过多介绍。后面几个项目针对EDID、EEPROM特殊场景的项目,经过上面一些项目的介绍,相信大家对于FPGA实现I2C应该更有信心吧。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。