来源:ZYNQ

最近准备数字IC岗时复习整理的知识点,参考了比较火的fpga面试题,和一些相关知识。主要是写着自己看着方便的,有很多不严谨的地方,有些地方有参考链接,那些博客写的都很好。

FPGA原理

1:FPGA和CPLD的区别?

2:FPGA的构成?查找表LUT的原理与结构?

3:FPGA设计流程:★

4:FPGA芯片内存储器资源?

5:FPGA上电配置方式

1:FPGA和CPLD的区别?

FPGA是可编程ASIC。ASIC:专用集成电路,为专门用途定制

CPLD这种基于乘积项(实际就是与或阵列)的PLD基本都是由EEPROM和Flash工艺制造的,一上电就可以工作,无需其他芯片配合。布线方式是全局的,所以延时可预测。CPLD适合做逻辑设计。而SRAM工艺的FPGA是易失的,因为它们是基于 SRAM 工艺的,掉电丢失配置。

2:FPGA的构成?查找表LUT的原理与结构?

Spartan-6中每个slice包括4个LUT,8个FF,和其他逻辑。具体了解slice结构有助于coding充分利用资源。

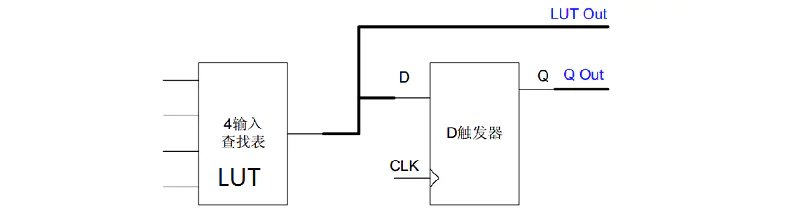

查找表(look-up-table)简称为LUT,LUT本质上就是一个RAM。如果FPGA中使用4输入的LUT,那每一个LUT可以看成一个有4位地址线的16x1的RAM。这也是为什么FPGA需要外接一个ROM来上电配置。

当用户通过原理图或HDL语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

3:FPGA设计流程:★

- 功能定义,器件选型

- 设计输入

- 功能仿真(前仿真) ModelSim

- 综合优化

- 布线

- 时序仿真(后仿真)

4:FPGA芯片内存储器资源?

FPGA芯片内有两种存储器资源:一种叫block ram,另一种是由LUT配置成的内部存储器(也就是分布式ram)。

Block ram由一定数量固定大小的存储块构成的,使用BLOCK RAM资源不占用额外的逻辑资源,并且速度快。但是使用的时候消耗的BLOCK RAM资源是其块大小的整数倍。

FPGA中可以综合实现为RAM/ROM/CAM的三种资源:block ram ;触发器(FF),查找表(LUT);

注意事项:

1:在生成RAM等存储单元时,应该首选block ram 资源;其原因有二:第一:使用block ram等资源,可以节约更多的FF和4-LUT等底层可编程单元。使用block ram可以说是“不用白不用”,是最大程度发挥器件效能,节约成本的一种体现;第二:block ram是一种可以配置的硬件结构,其可靠性和速度与用LUT和register构建的存储器更有优势。

2:弄清FPGA的硬件结构,合理使用block ram资源;

3:分析block ram容量,高效使用block ram资源;

4:分布式ram资源(distribute ram)

5:FPGA上电配置方式

上电——>清空寄存器——>根据M[1:0]电平设置载入模式——> 配置同步 ——> 启动序列 ——>CRC校验 ——> 载入配置文件 ——> 检测器件ID

- JTAG 边界扫描模式 4线

JTAG 引脚:测试数据输入(TDI)模式选择(TMS)和测试时钟(TCK),TDO输出。在这种模式下,每个 TCK 载入一个比特的数据。JTAG时钟频率—TCK 最高是 33 MHz。

TMS、TCK 和 TDI 引脚在缺省的情形下都提供了内部的可编程的弱上拉。TDO 是浮空的。

- 从并模式

- 主串模式 Master Serial SPI FLASH

- 从串模式 好像区别在于是不是自己的时钟CCLK驱动

- PROM配置:bit文件 iMPACT转mcs,写入PROM。

上电里面核心电压VCCINT先启动,然后是IO电压,,载入模式确定之后进行识别和载入配置文件,需要考虑上电时IO电压为弱上拉,要加入上下拉电阻,改变器件加电顺序等来尽量避免或减少FPGA配置时对电路其他器件的影响。载入成功后还会校验。

配置E²prom eletric eraser program IIC总线,要上拉,上电后写一个数据到 EEPROM 的地址 0, 再读出地址 0 的内容。这里我们写的数据是 0x12, 用户可以自行修改。

END

作者:比特波特

原文链接:https://mp.weixin.qq.com/s/yG18otVnNOqYLAtNjH5MBQ

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。