逻辑设计的演变

1958年,德克萨斯仪器公司(Texas Instrument)的年轻电气工程师杰克·基尔比(Jack Kilby)发明了如何将电路元件、晶体管、电阻器和电容器放置在一小块锗上。但在1958年之前,很多革命性的想法已经被发表和概念化。

戈特弗里德·莱布尼茨(Gottfried Leibniz)是德国著名数学家和哲学家,他在1676-1679年间重新定义了二进制数系统。在成功地重新定义了数字系统之后,著名数学家乔治·布尔(George Boole)在1854年发明了布尔代数,并开始了数字逻辑设计的革命。

1946年至1947年,肖克利、巴丁、布拉顿在贝尔实验室实际发明了晶体管原型模型,彻底改变了半导体在开关理论和芯片设计中的应用。1954年,第一个工作晶体管的设计,是莫里斯·坦恩鲍姆在德克萨斯仪器公司的最大贡献。

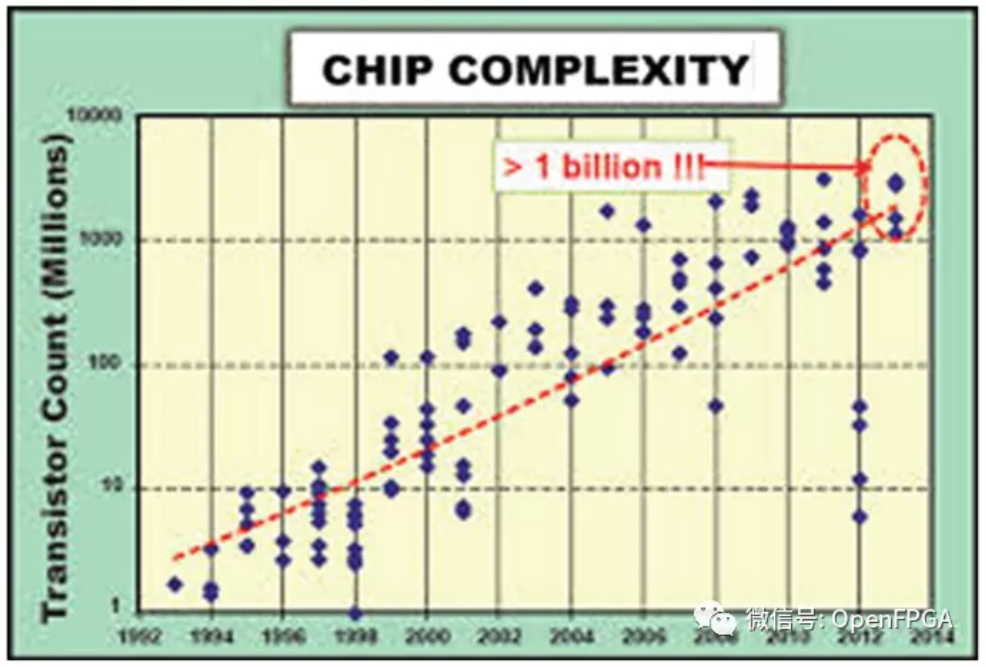

1963年CMOS逻辑的发明使得逻辑单元的集成变得非常容易,Intel的联合创始人戈登·摩尔(Gordon Moore)预测,相同硅面积的逻辑单元密度每18到24个月就会翻一番,这就是我们所说的摩尔定律。

摩尔的预测是正确的,工程师可以从复杂的基于VLSI的ASIC芯片设计中获得经验。在目前的十年中,芯片面积已经缩小到足够的程度,设计公司铸造厂工作的工艺技术节点是14纳米,芯片有数十亿个小硅芯片尺寸单元。随着设计和制造技术的发展,大多数设计都是使用高速集成电路硬件描述语言(VHSICHDL)或Verilog实现的。我们的重点是将Verilog作为硬件描述语言。EDA行业的发展为逻辑设计工程师在更短的时间内完成里程碑开辟了新的有效途径。

系统和逻辑设计摘要

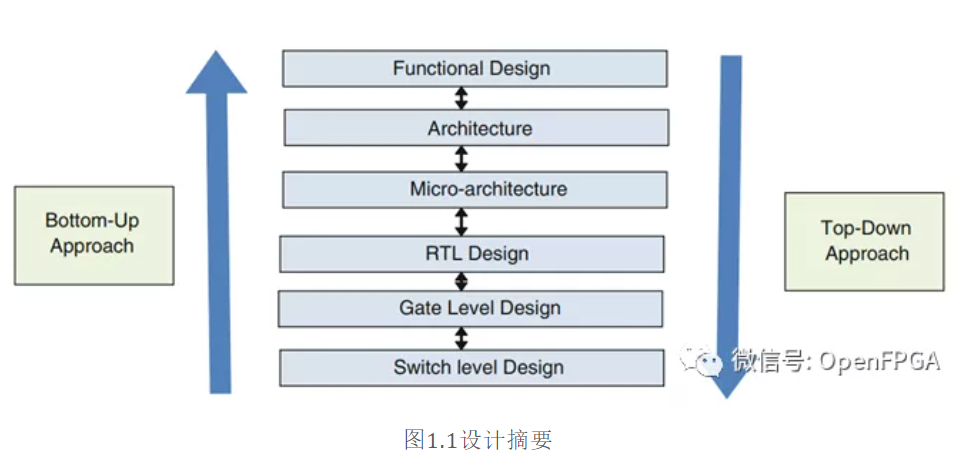

如图1.1所示,大多数设计具有不同的抽象级别。设计方法可以是自顶向下或自下而上。实施团队根据设计复杂性和设计资源的可用性决定正确的方法。大多数复杂的设计都使用自上而下的方法,而不是自下而上的方法。

最初将设计描述为功能模型,通过理解功能设计规范来描述设计的体系结构和微观体系结构。体系结构设计涉及对内存处理器逻辑和吞吐量的估计,以及关联粘合逻辑和功能设计需求。架构(Architecture)设计采用功能块的形式,并以方框图的形式表示设计的功能。

微体系结构是每个体系结构块的详细表示,它描述了块和子块级别的细节、接口和引脚连接以及分层设计细节。有关同步或异步设计以及时钟和复位树的信息也可以在微体系结构文档中描述。

RTL代表寄存器传输级别。RTL设计使用微体系结构作为参考设计文件,可以使用Verilog RTL对设计进行编码,以实现所需的设计功能。在此阶段,高效的设计和编码指南起着重要作用,高效的RTL减少了实施阶段的总体时间需求。RTL设计的结果是门级网表。门级网表是在执行RTL综合后,RTL设计阶段的输出,它以组合逻辑单元和时序逻辑单元的形式表示功能设计。

最后,开关级设计是布局中使用的抽象,以开关(或PMOS、NMOS和CMOS)的形式表示设计。

集成电路设计和方法

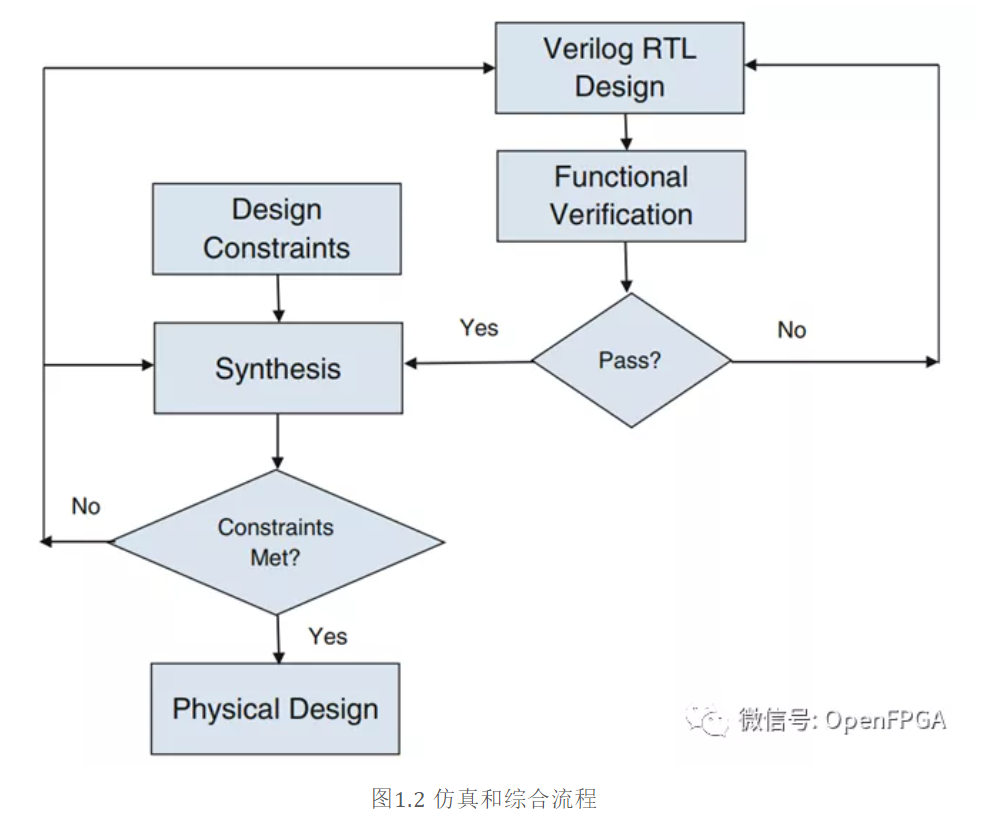

随着VLSI(超大规模集成电路(Very Large Scale Integration)的简称)设计技术的发展,设计变得越来越复杂,基于SOC的设计在更短的设计周期内变得可行。通过使用有效的设计流程,可以满足客户在较短的设计周期内获得产品的需求。设计需要从规范阶段发展到最终布局。使用具有适当功能的EDA工具,使具有经过验证功能的无缺陷设计成为可能。设计流程如图1.2所示,包括生成网络表的三个主要步骤。

RTL设计

使用体系结构和微体系结构以文档形式描述功能设计。使用Verilog的RTL设计使用微体系结构文档对设计进行编码。RTL设计器(RTL designer)在实现RTL设计时使用合适的设计和编码准则。一个高效的RTL设计在实现周期中始终扮演着重要的角色。在此期间,设计器使用有效的Verilog RTL描述块级和顶级功能。

功能验证

在完成给定设计规范的有效Verilog RTL后,使用行业标准仿真器验证设计功能。预合成仿真没有任何延迟,在此期间,重点是验证设计的设计功能。但业界的常见做法是通过编写测试平台来验证设计功能。测试平台将信号的刺激施加到设计中,并监控设计的输出。在当前场景中,验证流程中的自动化和新的验证方法已经发展并用于使用适当的资源在较短的时间内验证复杂的设计功能。验证工程师的职责是测试预期输出和实际输出之间的功能不匹配。如果在仿真过程中发现功能不匹配,则需要在进入综合步骤之前对其进行校正。功能验证是一个迭代过程,除非设计满足所需的功能和目标覆盖率,才会进图到下一阶段。

综合

当设计的功能需求满足时,下一步就是综合。综合工具使用RTL Verilog代码、设计约束和库作为输入,并生成门级网表作为输出。综合也是一个迭代过程,直到满足设计约束。主要的设计约束是面积、速度和功率。如果不满足设计约束,则综合工具将对RTL设计执行更多优化。优化后,如果观察到不满足约束,则必须修改RTL代码或调整微架构。合成器工具生成面积、速度和功率报告以及门级网络列表作为输出。

物理设计

它涉及设计的布局规划、电源规划、布局和布线、时钟树合成、布局后验证、静态时序分析以及ASIC设计的GDSII生成。

小结

此篇文章作为数字硬件建模开篇文章,后续将陆续进行Verilog介绍及相关建模的概念,不知道能坚持多久。。。。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。