查了一圈发现网上对post netlist simulation 介绍的比较少,今天和大家聊聊post netlist simulation。

首先什么是post netlist simulation(后面简称 postsim )?

Netlist simulation 有些公司也叫gate level simulation,是指将RTL综合后的网表用与仿真的过程。Post netlist simulation 则是将生产的网表和静态时序分析(STA)产生的SDF一起用于仿真。SDF(standarddelay format)描述了网表单元的时序信息。

其次为什么要跑post netlist simulation?

- Postsim 可以检查系统reset的状态和reset的流程对不对;

- Postsim可以检查上下电的流程是否正常;

- Postsim 相较于RTL simulation可以引入X(unknown)状态,可以发现更多的功能和时序问题;

- Postsim可以检查multi-cycle/asynchronous电路,这些电路的问题很难在RTLsimulation中被发现;

- Postsim 可以检查网表的功能是否正确;

除此之外Postsim 还被用于timing skew的分析,以及功耗分析;

由于MOS管受PVT(工艺,电压,温度)影响,后端在进行时序分析时会生成不同状况下的SDF。

post netlist simulation 需要跑哪些工艺角(processcorners)下的SDF呢?

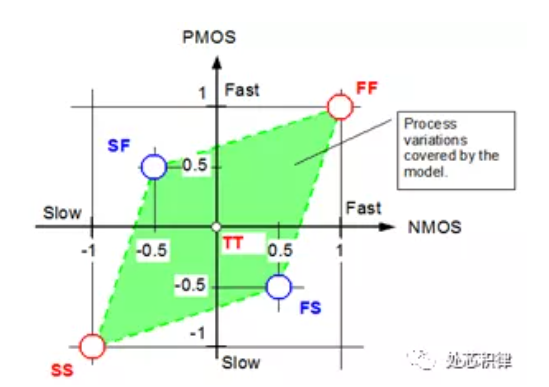

什么是工艺角,不同晶片在不同工艺,电压,温度下MOS管的参数变化很大,为了在一定程度上减轻电路设计任务的复杂性,工艺工程师需要保证器件的性能在某个范围内。工程师们以工艺角的形式给出数字电路的性能范围。其思想是把NMOS和PMOS晶体管的速度波动范围限制在四个角所确定的矩形。这四个角分别是:快NMOS和快PMOS(FF),慢NMOS和慢PMOS (SS),快NMOS和慢PMOS(FS),慢NMOS和快PMOS(SF)。如果我们设计的电路在这矩形内都能满足电路的功能和功耗需求,那么设计出来的芯片在实际应用里面就会具备很高的可靠性,比如芯片在125℃和-45℃下都能正常工作。

除了上述四个corner外,大家将中心点的位置称为Typical,Typical也就是TT。这个点就是常温下常压下芯片的工作状态,也可以称为一个corner,所以算上TT,工艺角一共有五个。

在上述5种corner中SS这个corner 的delay 最大,setup差,FF这个cornerdelay最小,hold差。

所以一般我们跑post simulation 盯住这两种corner就可以了检查网表中时序问题了。

这两种情况一般对应的是什么条件呢?

WC:worst case slow,低电压,高温度,慢工艺,这种情况就是SS,对应setup最差。

BC: bestcase fast,高电压,低温度,快工艺,这种情况就是FF,对应的hold最差。

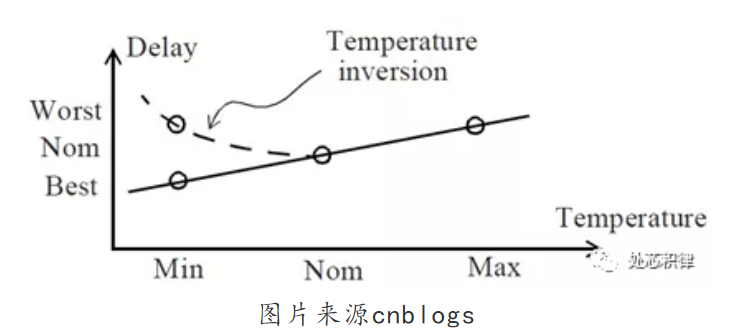

但是65nm以下的时候,人们发现随着温度的降低,delay增大,这就是温度反转效应,在这种情况下。低电压,低温度很可能造成delay最大,setup最差。这就多了以下两种case。

WCL:worstcase low-temperature,低电压,低温度,慢工艺,对应的setup 最差。

ML: maxleakage,高电压,高温度,快工艺,对应的delay最小,hold最差。

所以正常来讲,跑postsim 只需重点跑WC和BC的场景就行了,但是考虑到温度反转还需要测WCL和ML的场景。

对应一些需要在postsim检查skew修得怎么样的还得考虑SF和FS这两种corner,这是因为PMOS和NMOS两边速度相差很大,两个翻转的沿的skew相差也会比较大。

Post netlist simulation 需要准备什么?

Post netlist simulation 相较于 RTL simulation 会占据更多的内存,以及消耗更多的时间,你一个test在RTL simulation 可能只要5G内存就行了,但是到了post simulation可能就要40G,此外,RTL跑一只test可能只要1个小时,但是到了post simulation可能就要跑一个星期。

因此我们在准备test的时候,需要想办法加速post simulation。一个方法是缩短你的测试test,第二个是尽量不要dump波形,第三个同时跑几个test,第四个是通过backdoor的方式将一些初始化的状态force到simulation环境中去,尽量减少simulation在初始化中花的时间。

Post netlist simulation 需要测哪些东西?

在流片前,post netlist是最接近真实芯片的,所以他是保证芯片质量的最后一道护卫。如果时间和资源允许当然是所有的corner和tests都要测。

如果资源和时间有限的情况下该重点关注哪些呢?

- 跨时钟域的test

- Power switch 相关的test

- Reset 相关的test

- 不同clock频率下的test

- Chip外设相关的test

- Chip 内部模块的基本功能相关test

- Bootrom相关的test

Post netlist simulation 需要怎么去debug?

这是一个很头疼的问题,首先postsim 跑起来特别慢,如果test fail,要去dump波形的话会花很长的时间,其次postsim是拿网表跑simulation的,网表不像RTL那么直观,很难看懂。所以如何去debug?以下是我总结的经验。

- 跑postsim的test一定要在RTL阶段跑pass过。

- 如果有时间可以建立不带SDF的Prenetlist环境,Pre netlist simulation跑起来速度会很快,在这个阶段如果test跑fail也能快速dump波形debug。

- 跑postsim的时候跑两只test,一只dump波形,一只不dump波形,如果不dump波形的跑过了,dump波形的就没有必要继续跑了。

- Dump波形的时候不要全部dump,分时,分模块去dump。

- Debug的时候可以拿netlist跑出来的波形在load RTL设计的verdi里面看,综合虽然做了优化,但是一些模块的接口信息还是能对应上。

- 如果实在debug实在困难,就只能trace信号去debug了,一直认为trace信号是IC工程师的一项基本功。

总结

Postsim是芯片顺利流片的最后一道守卫。理论上前期的流程比较完善,在postsim中不会遇到太大问题。因为诸如跨时钟域的问题,时序的问题,功能问题都能在前期的CDC,STA,LEC等过程中被发现。但是问题是很多公司人力资源有限,在这种情况下只能靠postsim增加流片信心。

作者:IC bug 猎人

原文链接: 处芯积律

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。