写在前面

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.

本文系转载,略做格式调整与增加解释,转自https://blog.csdn.net/weixin_48180416/article/details/116564143

相应内容可参考:

- MindShare, PCI Express System Technology 3.0 第十三章。

- 《PCI Express 体系结构导读》 第八章

转载正文

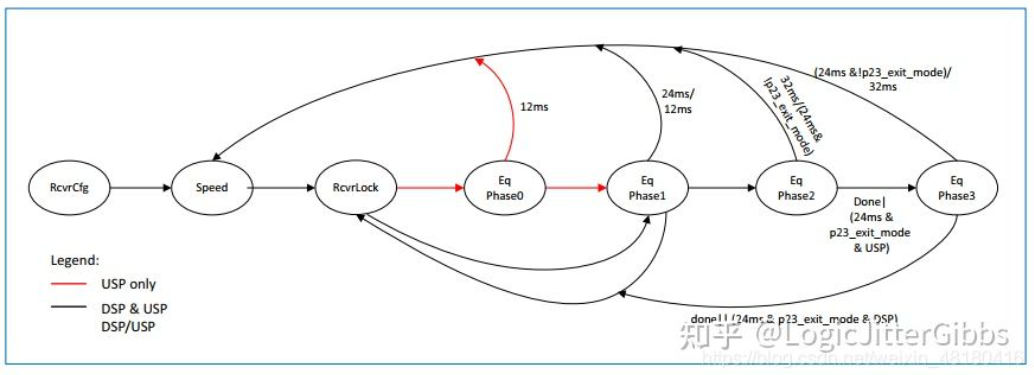

Link EQ的过程是首次进入8GT/s及以上的速率时进行的。EQ主要包含四个阶段:Phase0, Phase1, Phase2, Phase3.

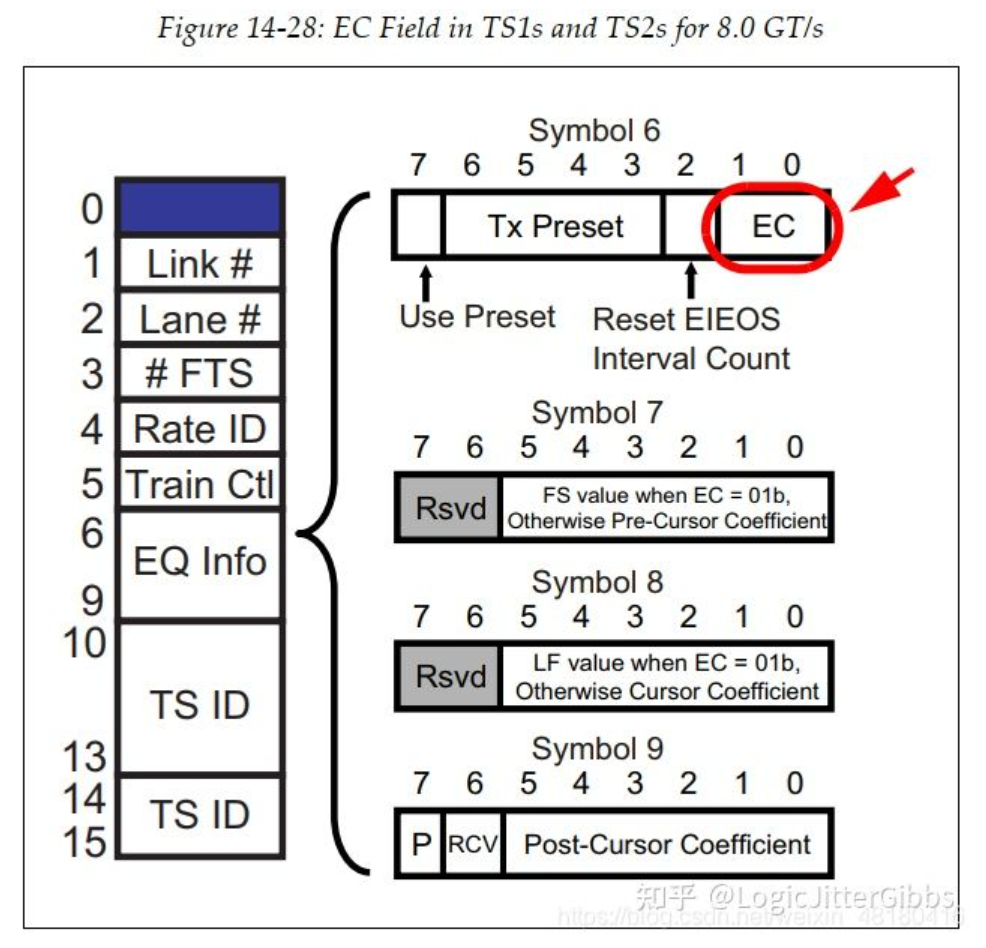

在TS1和TS2的格式中包含EC字段,0--Phase0, 1--Phase1, 2--Phase2, 3--Phase3

下面介绍EQ过程的LTSSM状态机的跳转及TS交互

EQ过程的LTSSM状态机的跳转及TS交互

当Link Training到2.5GT/s, L0状态后,硬件自动发起Speed Change到8GT/s(或者从8GT/s速率Speed Change到16GT/s),与之前介绍的Speed Change到5GT/s不同的是多了EQ的过程。

状态机从

L0->RcvrLock->RcvrCfg->Speed->RcvrLock->Equalization->RcvrLock->RcvrCfg->Idle->L0

Equalization->RcvrLock是比 speed change 到 5GT/s 多出的部分

RcvrLock:

与Speed Change到5GT/s相同,都是交互TS1进行Lock;

RcvrCfg:

与Speed Change到5GT/s不同,DSP发给USP是EQ TS2或128b/130b EQ TS2而不是普通的TS2;

DSP会从它的Lane Equalization Control (LEC) 寄存器和Lane Equalization Control 2(LEC2) 寄存器获知以下参数:

- DSP Tx preset/Rx preset hint, USP Tx preset/Rx preset hint ---- 8GT/s

- DSP Tx preset/Rx preset hint, USP Tx preset/Rx preset hint ---- 16GT/s

然后DSP将USP需要用到的Tx preset/Rx preset hint发送给USP。 Receiver均衡器是否采用Rx preset hint是可选的

注: GEN4时也可以是USP将寄存器的内容发送给DSP,与上述过程相反。

Speed:

除了改变速率,见系列博文(一) Recovery子状态介绍,还存在以下过程:

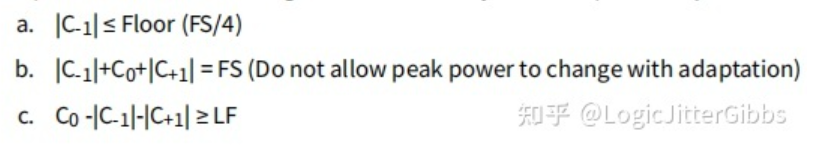

local Tx preset映射为C+1、C0、C-1系数(由MAC或PHY来映射)后,local PHY 提供LF、FS,

MAC检查是否满足以下规则

以下介绍均衡的Phase0~Phase3

均衡阶段:Phase0~Phase3

EQ Phase0: USP echos Preset and Coefficients to DSP

USP会从RcvrLock到Phase 0,USP发送ec0TS1,其中包含Preset和系数,目的是将目前所用到的Preset和系数回传给DSP。

EQ Phase1: 知晓对端的LF、FS,用于 Phase2/3

DSP会从RcvrLock到Phase 1 (DSP不包含Phase 0),DSP发送ec1TS1给USP,其中包含DSP PHY用到的LF、FS、Post-Cursor(因为LF、FS占用了Pre-Cursor和Cursor位);

同样,USP也会发送ec1TS1给DSP,其中包含USP PHY用到的LF、FS、Post-Cursor(因为LF、FS占用了Pre-Cursor和Cursor位);

知晓对端的LF、FS的目的是在Phase 2/3的时候,PHY决定如何去调节系数。(仅Coefficients Request精调时用到)

注意以下几点:

- EQ Phase0和Phase1会应用RcvrCfg时交互的Preset作为初始的Preset值;

- 经过Phase 0/1后,TS1 Order Set可以被正确接收,BER达到了<10^-4的要求;

- 如果认为Phase 0/1后,信号质量达到要求,可以不进行Phase 2/3的调节。

EQ Phase2: USP调节USP的Transmitter

USP作为EQ Master,开始调节DSP的Transmitter。有两种调节方法:

- Preset Request

- Coefficients Request

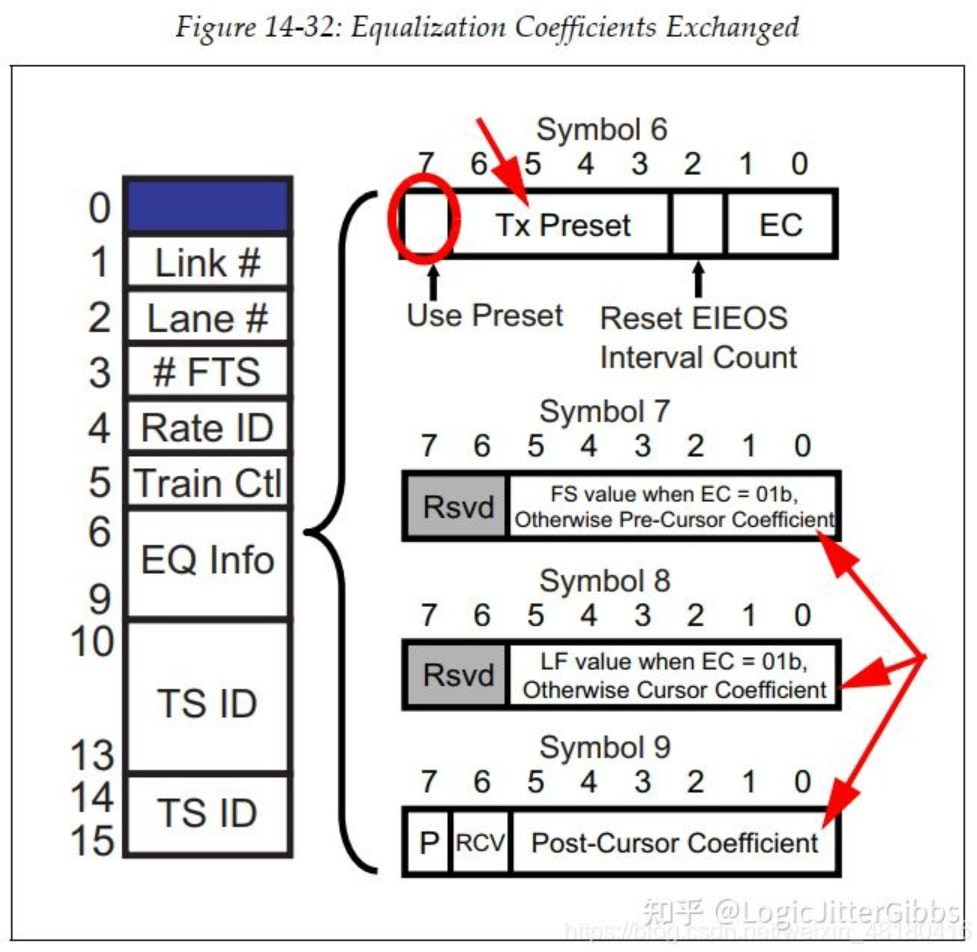

TS1的Symbol 6~Symbol 9是与之有关的字段,如下图:

Preset Request

- USP发送ec2TS1给DSP,其中包含Tx Preset字段和Use Preset=1通知DSP使用Preset Request的方式。

- DSP获取当前Preset后,将其映射(MAC或PHY映射)为Coeff, 检查Coeff、local PHY的LF、FS规则,符合规则Transmitter就会应用此Preset对应的Coeff并设置TS的accept,不符合就设置reject;

- 随后DSP将带有Preset, Coeff, accept/reject信息的TS给USP,当accept时,USP记录Preset、Coeff、评估值,当reject时跳过这个preset,继续评估下一个preset。

- 评估所有的预设的Preset(不一定是所有的preset),重复1,2,3过程;

- 评估完成后,选择最优的Preset,再发起最后一次Preset的评估。

Coefficient Request

上述过程Preset Request完成后会进入Coefficient Request(可选的)

- USP记录最优的Preset对应的Coeff、评估值,USP根据Receiver端的评估值直接调整系数,发送ec2TS1给DSP,其中包含Tx Coeff和Use Preset=0通知DSP使用Coeff Request的方式。

- DSP获取当前的Coeff, 检查Coeff、local PHY的LF、FS规则,符合规则Transmitter就会应用此Coeff并设置TS的accept,不符合就设置reject;

- 随后DSP将带有Coeff, accept/reject信息的TS给USP,当accept时,USP记录Coeff、评估值,当reject时跳过这个Coeff,继续改变系数评估新的Coeff。

- 重复1,2,3过程;

- 直到系数收敛,达到时间窗口,达到评估次数限制后认为达到最优的Coeff。

以Synopsys IP为例

以Synopsys IP为例介绍,Preset Request采用FOM Mode,Coeff Request采用DIR Mode

1. FOM Mode

在EQ Phase 2/3中,MAC选择不同的Preset,remote PHY应用Preset对应的Coeff, 随后Local PHY评估Receiver端的眼图质量,

FOM以0-255的值来表示,数值越高代表眼图质量越好,遍历所有的Preset后选择最优的眼图,即FOM的最大值,最终以此Preset作为Transmitter的系数。

2. DIR Mode

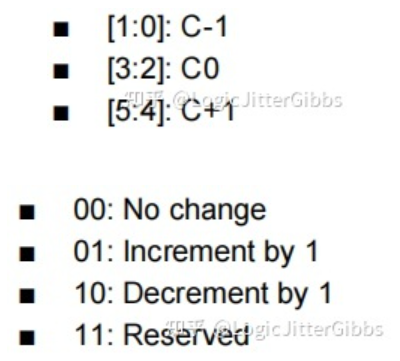

在EQ Phase 2/3中,MAC选择Coeff,remote PHY应用Coeff, 随后Local PHY评估Receiver端,每条Lane会给出6bit, 含义如下:

由于|C0| = FS - |C-1| - |C+1|,只需要根据Local PHY反馈的6bit信号来调整C+1和C-1。

Coeff Request收敛原则如下:

- 连续评估的次数 --- 由寄存器配置,表示评估窗口的深度;

- 检查是否收敛的最小时间 --- 由寄存器配置,指定时间后开始检查是否收敛;

- 窗口内C+1/C-1小于限定的delta值 --- delta值是窗口内多次评估C+1/C-1的偏差值,表示C+1/C-1系数的波动。

EQ Phase3: DSP调节USP的Transmitter

DSP作为EQ Master,开始调节USP的Transmitter。方法同Phase 2。

注意:

- 每条Lane的Preset是相互独立的;

- Spec没有规定评估某个Preset接收信号质量的具体方法,由IP来决定

Speed: 当Final Preset Request被reject了,或是上面的图中的各种超时,从EQ Phase就会跳转回到Speed子状态,说明EQ不成功需要降速,会Revert Speed。

Phase EQ 时长限制

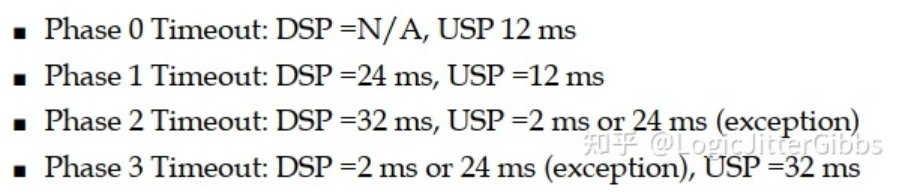

各个Phase有如下的时间要求

- 每个Preset的评估时间不超过2ms,如果超时就会跳过这个Preset,继续评估下一个Preset;

- 所有Phase的时间要求如下:

其中,Phase 2/3时间包含Preset粗调和Coeff精调。

转载评注

在 EQ 过程中,如何得知某个 preset /coeff 的质量情况?

Remote PHY 应用并发送,Local PHY 评估接收端眼图质量, 眼图评估方法由具体实现决定

版权声明

版权声明:本文为CSDN博主「小雨滴落落」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:PCI Express学习篇---物理层LTSSM(三) Recovery.Equalization详解

转载自:知乎

作者:小雨滴落落

推荐阅读

更多招聘及面经请关注FPGA的逻辑。