上篇文章我们大致介绍了7nm实现中Innovus和ICC2常见的DRC问题【后端进阶系列:Innovus+ICC2对比7nm工艺的后端实现(物理篇)】,本篇将简要归纳一下二者在时序(Setup&Hold)、面积、Inst数量、Power和runtime等具体参数上的差异。

设计条件

本次测试使用了ARM Cortex A53核心作为评估对象。RTL基本上只替换了SRAM类型,没有做任何逻辑上的改动。工艺上采用7nm,目标性能在ss corner, 0.675v电压下达到1.67GHz(600ps时钟周期)。优化过程中将Timing优化调整为最高优先级,power与area的约束调到最低。Signoff条件基本采用IP vendor的推荐设置,配合一些笔者经验下Silicon Proven的设置和margin,此部分的具体设置将做一些模糊处理。工具版本基本为2021年的较新版本,同时保证用相同的signoff工具和设置验证不同PR工具的结果。

(表1:设计前提条件)

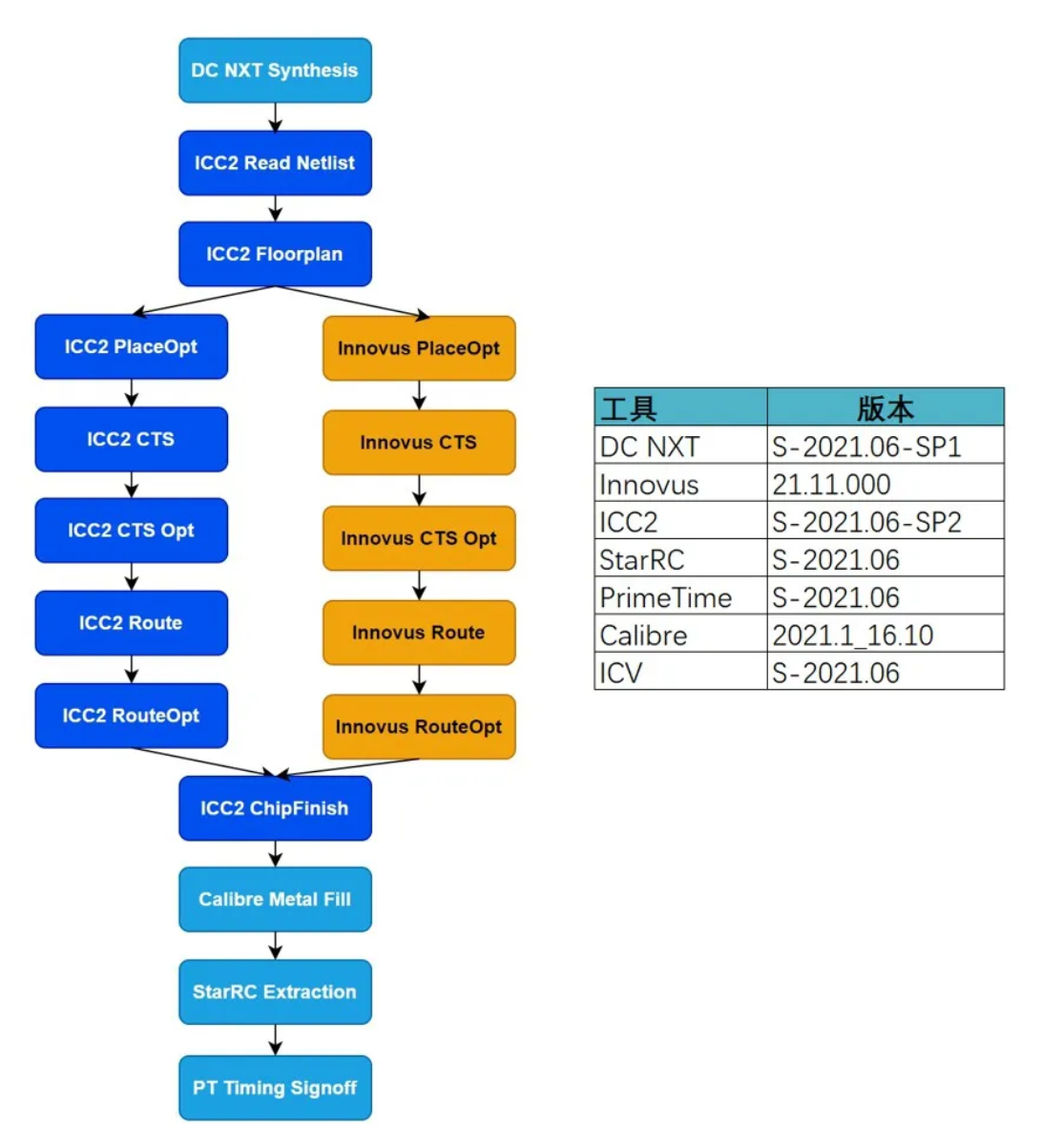

评估流程和对应的工具版本如下:

(表2:评估流程和工具版本工具版本)

Timing优化策略

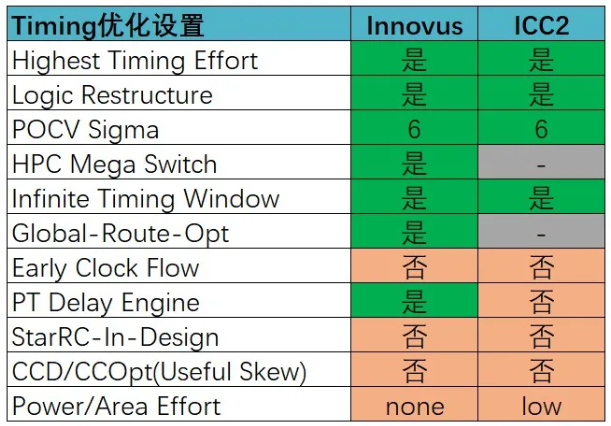

在timing优化过程中,没有使用太多工具的高级功能,仅仅试图找到常规的优化手段下的timing极限结果,因此即使是CCD/CCOpt的useful skew等相对成熟的功能也没有开启。唯一相对高级的功能可能就是logic restructure了。为了保证Innovus对StarRC+PT的timing一致性(correlation),两种优化工具在不同优化阶段的margin其实是不一样的,同时也做了一些比较常规的correlation调整,如:改变uncertainty、设置RC scaling factor和net derate等。最终得到了比较好的Innovus Post-Route和PT STA的一致性,基本可以达到‘所见即所得’,调整correlation的过程将在后续篇幅介绍,本篇不再赘述。所有相关的设置如下表所示:

(表3:优化设置)

QoR结果总结

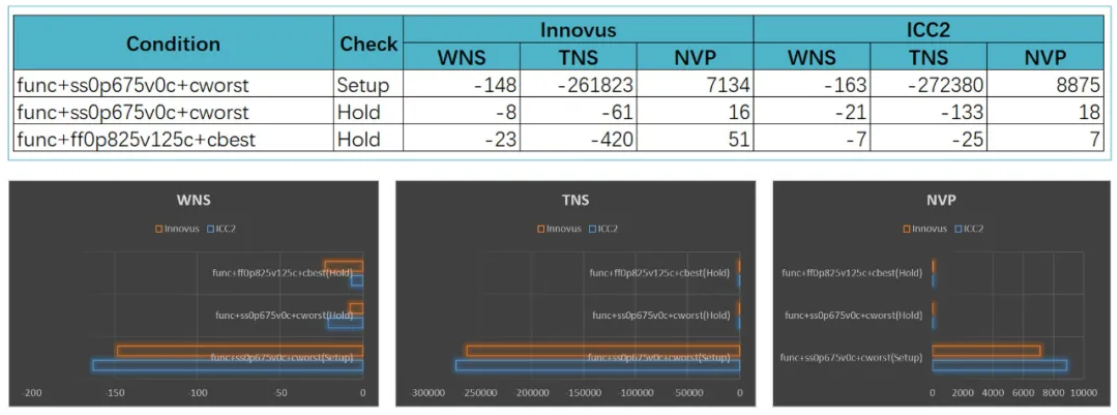

在timing结果方面,比较了一个setup corner和2个hold corner,其他corner的趋势基本相同,为了减小数据量就不再一一列举(以下结果均为PrimeTime结果):

(图表1:Innovus vs ICC2 Timing)

简单地说,优化结果上ICC2比Innovus确实要差一些。但让人诧异的其实并不是ICC2的结果差,而是二者的差距可以说是非常小,TNS的差别不到5%。如果说两三年前Innovus对ICC2的优化能力还是碾压的话,那么在2021年年底的今天,二者在时序优化方面的能力恐怕只在伯仲之间。为了进一步验证这个感受和猜想,笔者特意用P-2019.03-SP5版的ICC2用完全相同的命令组合跑了一遍,得到了下面的结果:

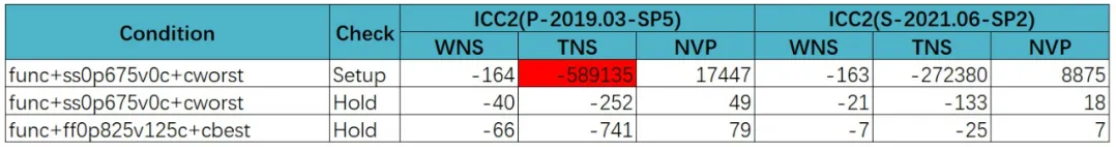

(表4:ICC2 2019vs2021)

可以看出来2年前的ICC2和现在比优化结果差的不是一点半点,说是完全不同的两个工具也不为过。个人看来ICC2有这样的变化趋势其实并不意外,毕竟在人才自由流动的今天,工具已经日渐趋同,想要一直保持绝对的优势是很困难的,唯一的意外就是这追赶的脚步还是慢了点,毕竟ICC2推出至今已经至少五六年了。

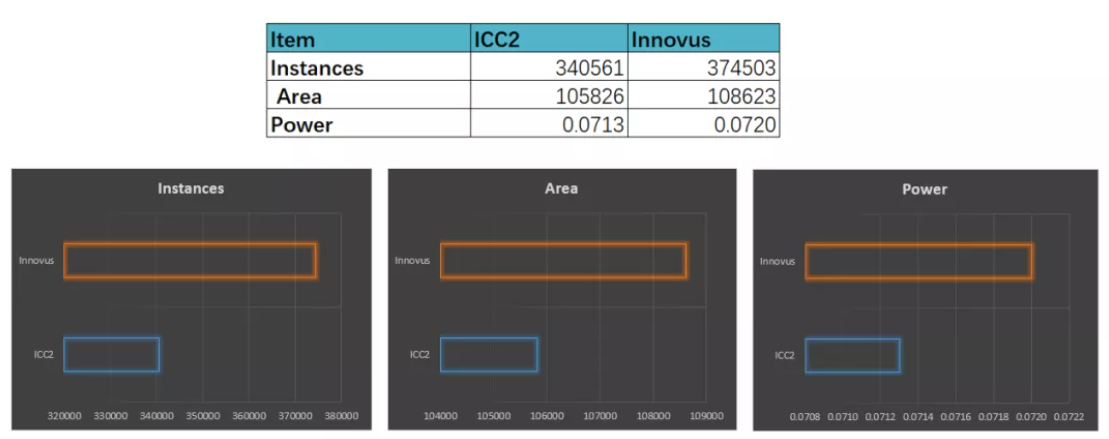

在Instance数量、Area和Power方面,ICC2的结果要稍好于Innovus。但是由于优化过程中把这几类调为最低优先级,因此可以认为工具并没有特别在这几方面做出优化,尤其是Power仅为PTPX vectorless的结果,其实在把所有timing violation修完之前并不能确定两个工具在这几个方面的真实差别,只能算是聊胜于无:

(图表2:Innovus vs ICC2 Inst/Area/Power)

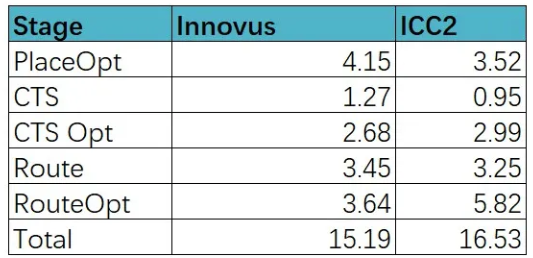

最后是runtime,Innovus仍然在这方面有一定优势,尤其是postroute优化方面:

(表5:Runtime比较)

结论

通过一个模块的实验,可以发现2021年较新版本的ICC2和Innovus在7nm工艺的timing优化方面相差无几,其他主要参数也没有特别明显的区别。但个人认为ICC2即使做到和Innovus相同的QoR也很难挽回流失的市场份额,毕竟很多公司已经在Innovus上花了大量的时间和人力优化流程,在没有绝对利益的前提下很难转向,沉没成本实在是太大了。Synopsys针对Cadence在数字实现工具上真正的胜负手恐怕还在下一代AI平台上:DSO.ai vs Cerebrus。这两个工具目前应用范围还不大,希望可以早日推广开来。另外Fusion Compiler前两年同样做的比较那啥,但笔者最近的实验发现了一些变化,当然这又是另一个有趣的话题,我找时间也会尝试一下,有兴趣的同学敬请关注~

来源:数字后端设计芯讲堂

作者:数字后端设计芯讲堂

推荐阅读

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路

同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。