项目地址

https://github.com/enjoy-digital/litex/wiki

LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

简介

LiteX 提供了轻松创建 FPGA 内核/SoC 所需的所有常用组件:

- 总线(Wishbone、AXI、Avalon-ST)及其互连。

- 简单内核:RAM、ROM、定时器、UART、JTAG 等。

- 通过内核生态系统的复杂内核:LiteDRAM、LitePCIe、LiteEth、LiteSATA等......

- 各种 CPU 和 ISA:RISC-V、OpenRISC、LM32、Zynq、X86(通过 PCIe)等...

- 混合语言支持 VHDL/Verilog/(n)Migen/Spinal-HDL/etc...

- 通过各种桥接器和Litescope进行强大的调试基础设施。

- 通过Verilator直接/快速仿真。

- 为开源和供应商工具链构建后端。

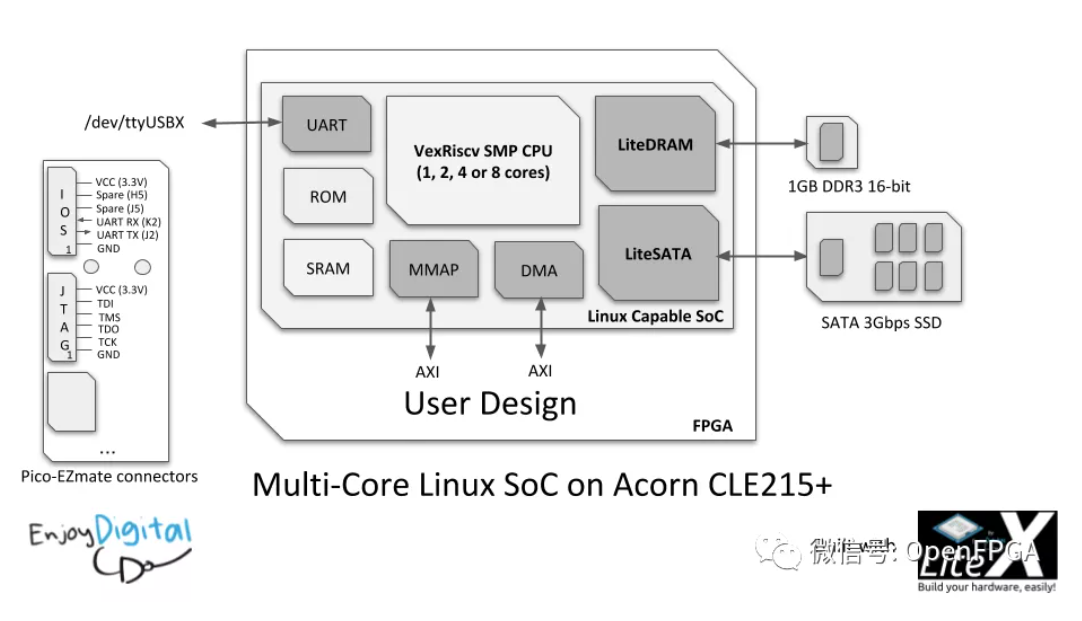

通过将 LiteX 与内核生态系统相结合,创建复杂的 SoC 变得比使用传统方法容易得多,同时提供更好的可移植性和灵活性:例如,基于 VexRiscv-SMP CPU、LiteDRAM、LiteSATA 构建的多核 Linux SoC与 LiteX 集成,在廉价的改造Acorn CLE215+ Mining Board上运行:

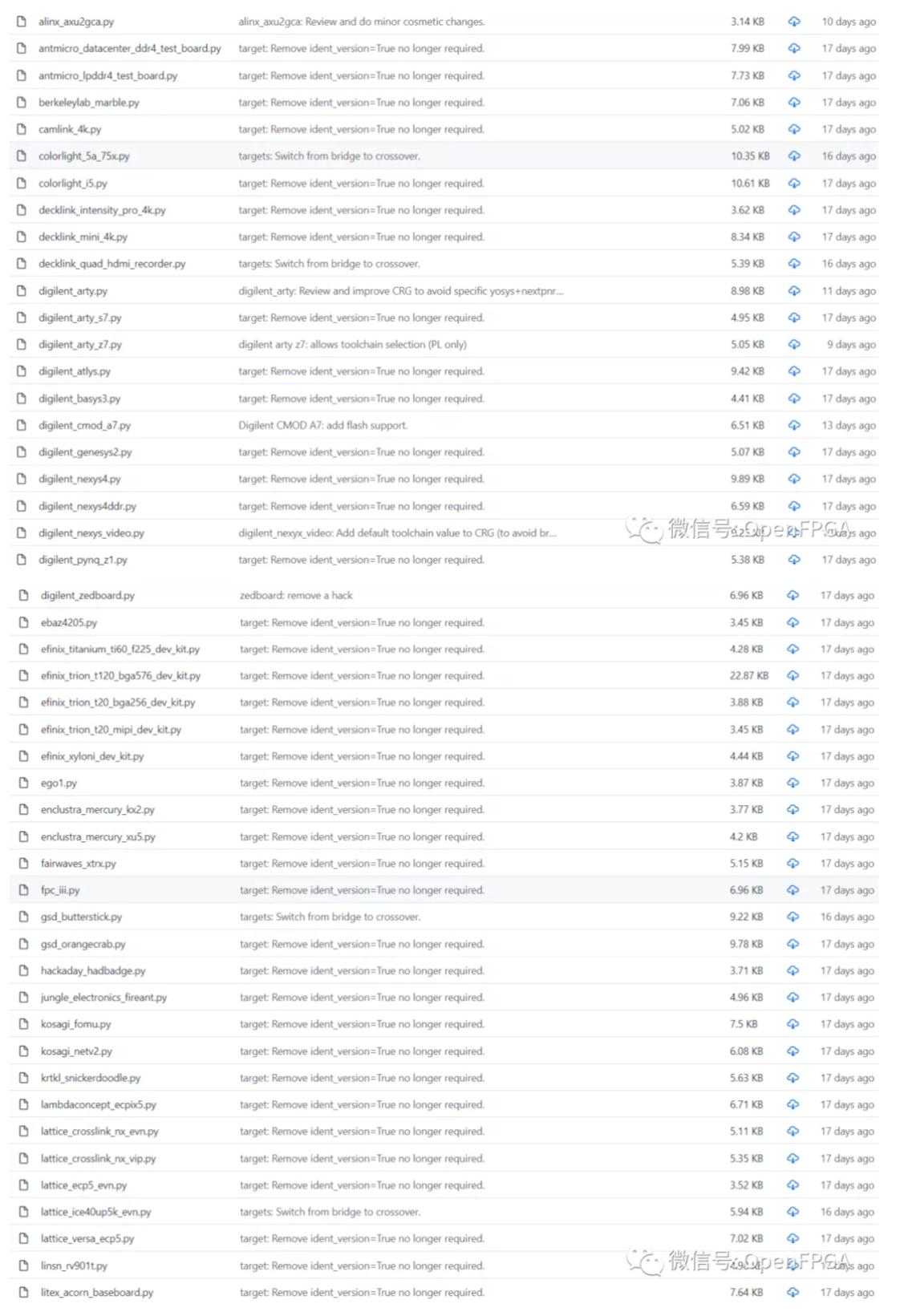

支持的硬件

https://github.com/litex-hub/litex-boards/tree/master/litex_boards/targets

典型的 LiteX 设计流程:

+---------------+

|FPGA toolchains|

+----^-----+----+

| |

+--+-----v--+

+-------+ | |

| Migen +--------> |

+-------+ | | Your design

| LiteX +---> ready to be used!

| |

+----------------------+ | |

|LiteX Cores Ecosystem +--> |

+----------------------+ +-^-------^-+

(Eth, SATA, DRAM, USB, | |

PCIe, Video, etc...) + +

board target

file file

LiteX 已经支持各种软核 CPU:VexRiscv、Rocket、LM32、Mor1kx、PicoRV32、BlackParrot,并且与 LiteX 的核心生态系统兼容:

使用 LiteX 构建的设计示例:

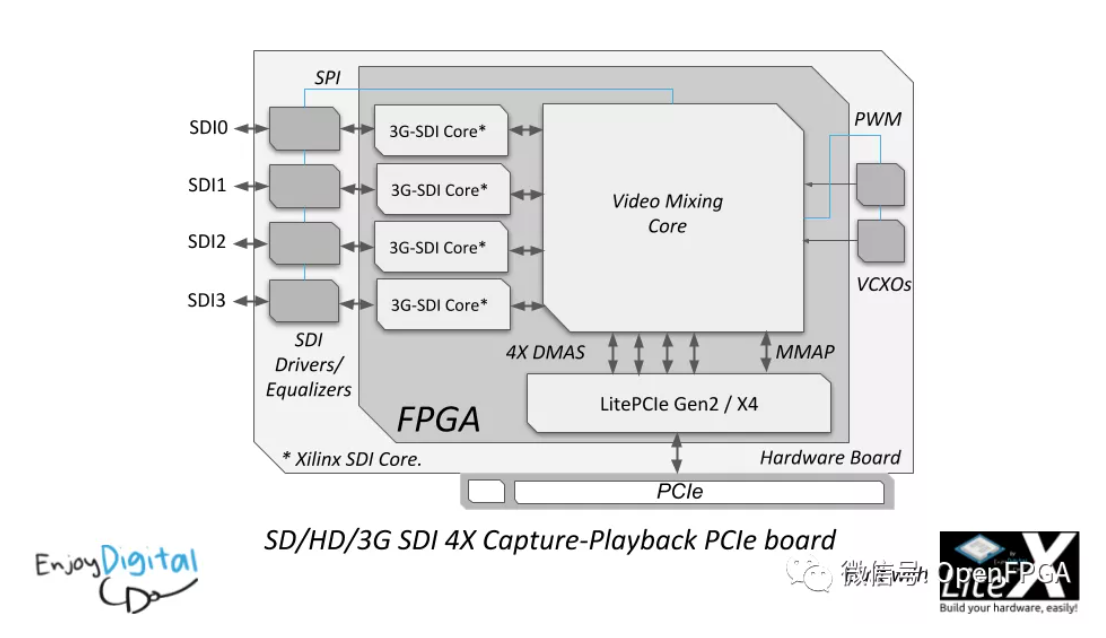

围绕 LitePCIe 构建并与 LiteX 集成的定制 PCIe SDI 采集/播放板,允许完全控制 SDI 流和极低的延迟。

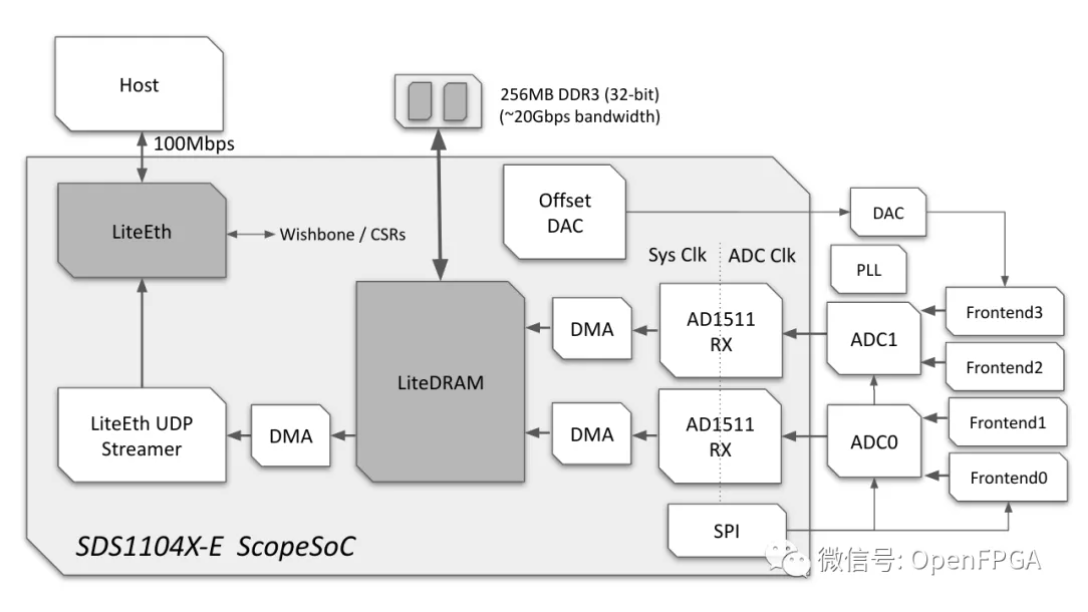

SDS1104X-E 范围的替代固件/网关:

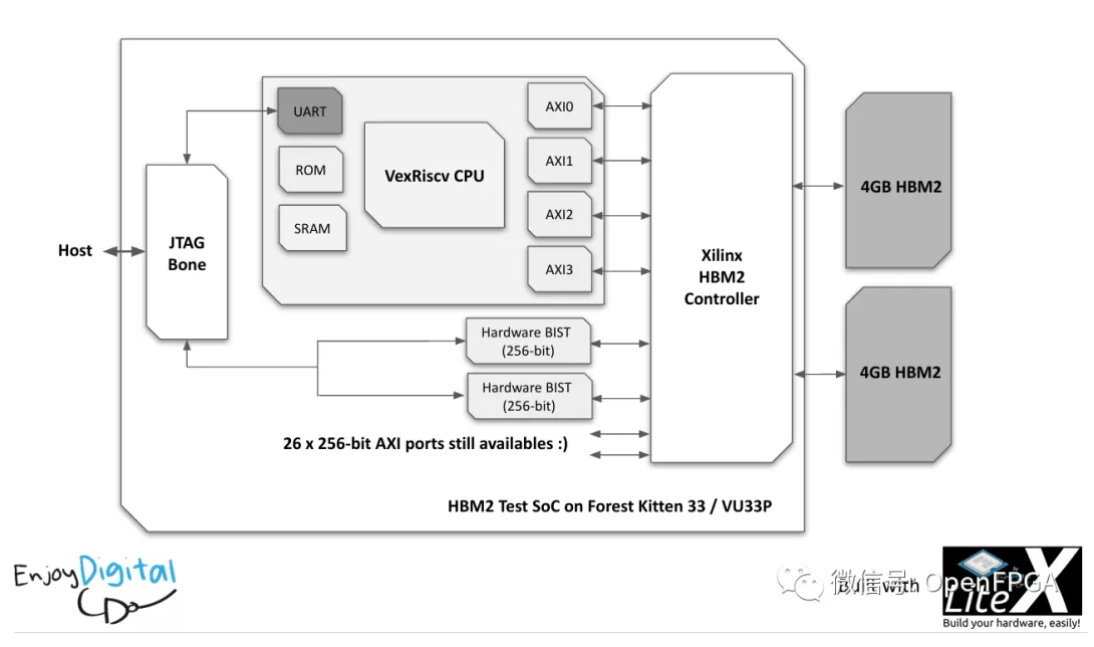

Forest Kitten 33 上的 HBM2 测试基础设施:

快速入门指南

安装 Python 3.6+ 和 FPGA 供应商的开发工具和Verilator(仿真器,可以不安装)。

安装 Migen/LiteX 和 LiteX 的核心:

wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

chmod +x litex_setup.py

./litex_setup.py --init --install --user (--user 安装到用户目录) --config=(minimal, standard, full)需要更新所有存储库:

./litex_setup.py --update注意:在 MacOS 上,确保您已安装HomeBrew。然后做,brew install wget。

注意:在 Windows 上,您可能必须将SHELL环境变量设置为SHELL=cmd.exe.

安装 RISC-V 工具链(仅当您想使用 CPU 测试/创建 SoC 时):

pip3 install meson ninja

./litex_setup.py --gcc=riscv建立目标......:

转到 litex-boards/litex_boards/targets 并执行您要构建的目标。

直接在您的计算机上安装Verilator并测试 LiteX,无需任何 FPGA 板:

在 Linux (Ubuntu) 上:

sudo apt install libevent-dev libjson-c-dev verilator

litex_sim --cpu-type=vexriscv在 MacOS 上:

brew install json-c verilator libevent

brew cask install tuntap

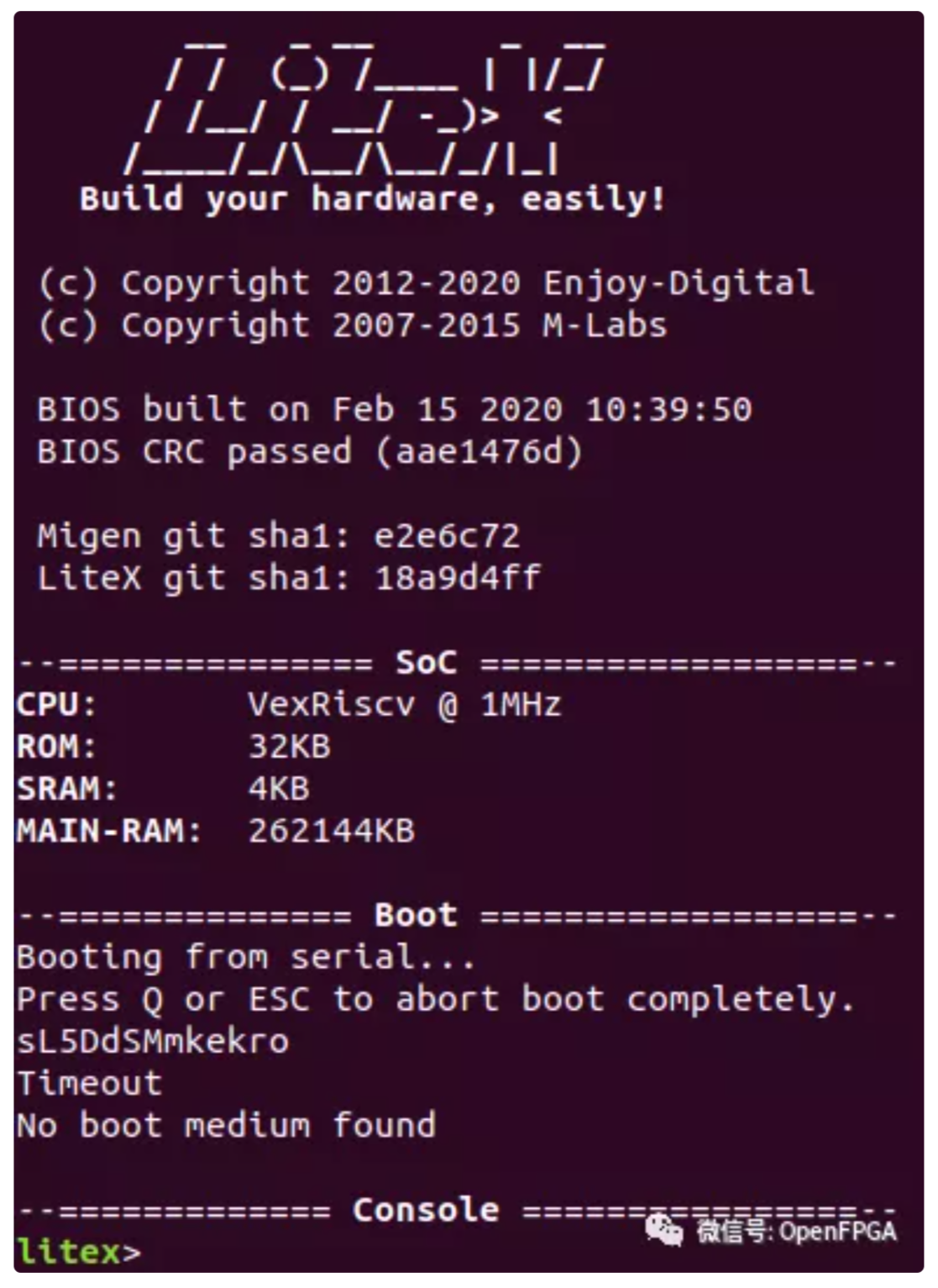

litex_sim --cpu-type=vexriscv在板上的串行端口 115200 8-N-1 上运行终端程序。

应该得到如下所示的 BIOS 提示。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。