本期我们将基于 DDR4 讨论 DRAM 的上电与复位过程。

基于 JESD79-4B / 3.3 节

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

DDR 学习时间 - OpenIC SIG 开源数字IC技术分享

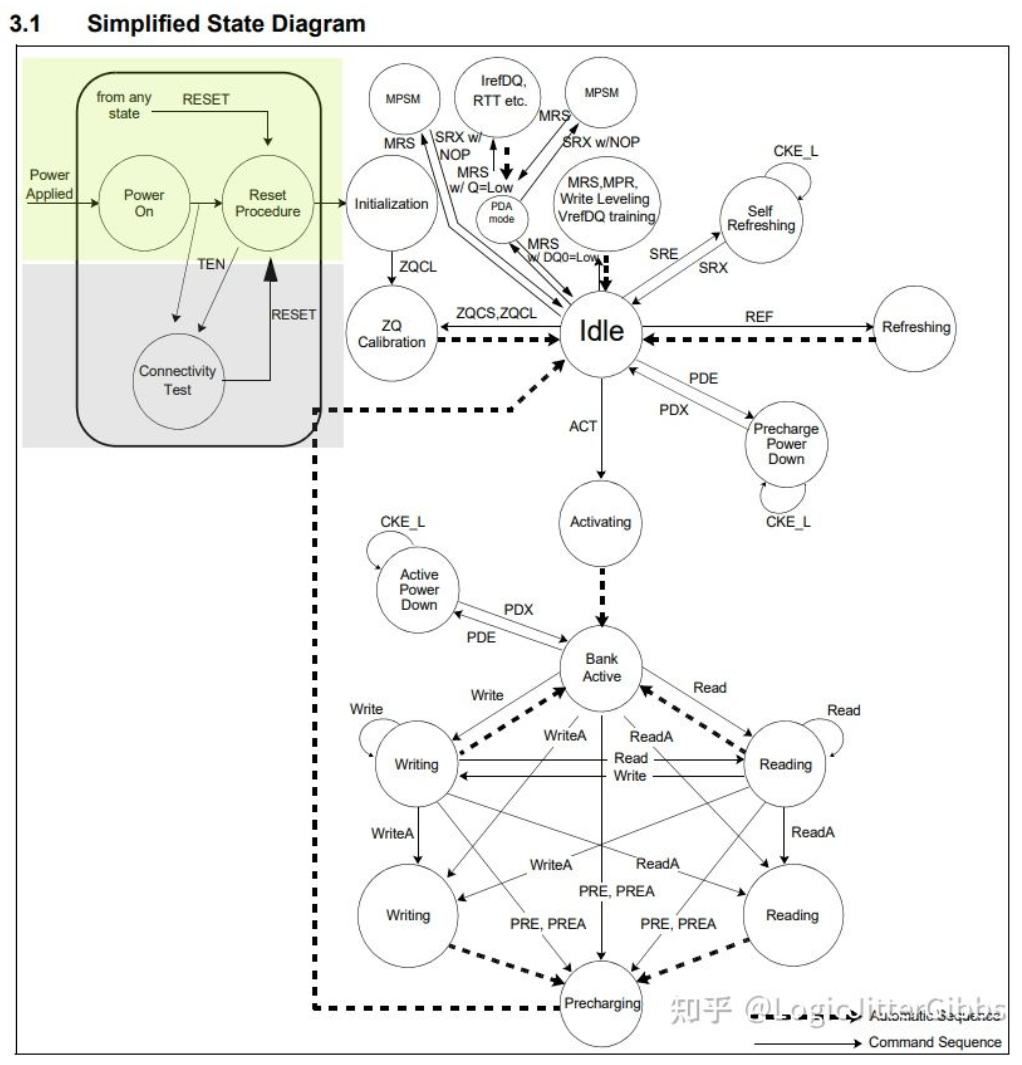

DRAM 状态机中的上电与复位 //Power-on and Reset in DRAM State Diagram

上电(Power-on)/施加电源(Power applied)事件是 DRAM 状态机的入口,大致指 DRAM 的 VDDQ/VDD 等电源的电压上升至常工作电压,并达到稳定这样一个过程。

复位(Reset)行为会清除当前 DRAM 的工作状态,比如 DRAM 存储的数据, MRx 寄存器的值,当前的刷新计数等。

复位有两种触发情况,一是由上电触发。上电事件后总是伴随着一次复位行为。另一种是由外部逻辑,比如 DDR 控制器通过控制 DRAM 的 RESET\_n 信号触发。

上电后或者在 DRAM 后续的任何状态中产生复位事件,都会进入复位流程状态(Reset Procedure),完成后进入 DRAM 的初始化状态(Initialization)。

上图绿色部分是DRAM 状态机中的上电与复位相关的状态。灰色部分的 Connectivity Test 状态在一般的 DRAM 应用中不会实现。

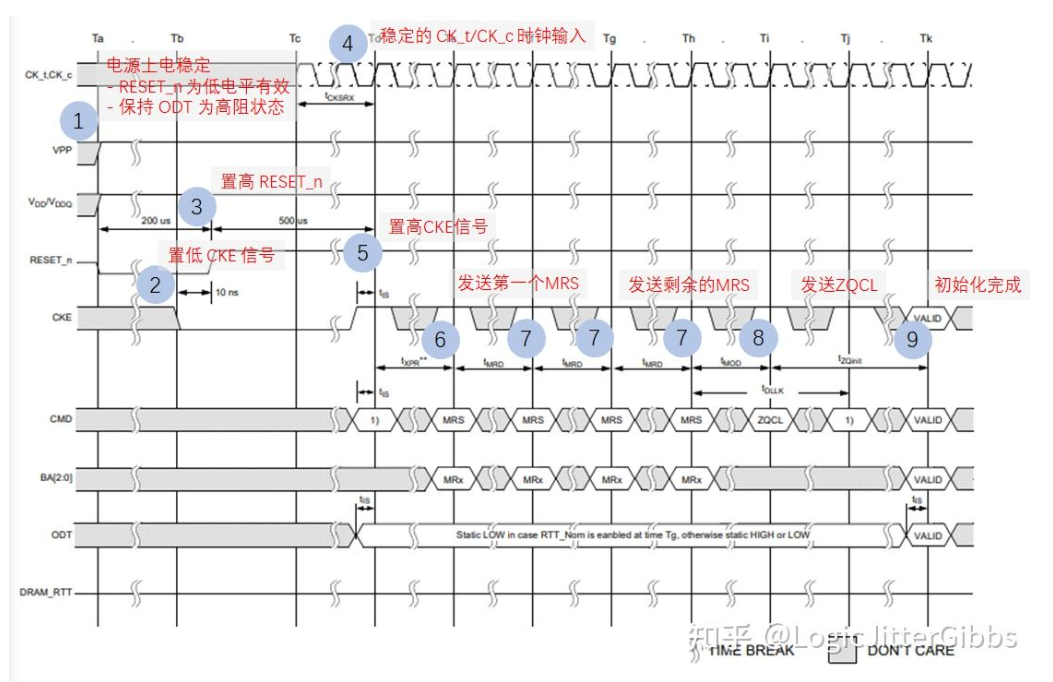

上电初始化流程 //Power-on sequence

本节我们首先讨论上电(Power-up)的初始化流程,复位(Reset)触发的初始化流程与上电类似,后文只将讨论两者间的差异。

上电初始化流程整理

在 JEDEC 79-4B 中上电初始化流程划,基本按照时间顺序,归纳为 15 点,本文整理为 10 点。

- DRAM 外部电源上电,VDD/VPP/VDDQ 之间的上电关系稍后再表。此时,推荐 RESET_n 信号保持低电平使能,其电压值保持在 0.2 * VDD 以下。

- 复位有效时 CKE 信号可以为低,也可以为高电平,但在 RESET_n 信号置高前至少 10ns,置低并保持 CKE 信号为低电平。

- 在电源稳定后,延迟 200us,即 RESET_n 信号保持 200 us,RESET_n 信号置高,使 DRAM 退出复位状态

在 RESET_n 置高后,延迟 500us ,使能外部时钟输入 CK_t/CK_c 以及有效信号 CKE。

期间 DRAM 会进行内部初始化,此时不需要外部的时钟输入

CK_t/CK_c 必须早于 CKE 信号有效 10ns (或者 5 个时钟周期,取较大值)前稳定。在一些功耗管理粗放应用中,可以早早地产生 CK_t/CK_c 。

- 在 CKE 信号有效前,保持 DRAM 片上终结电阻(ODT, On-Die-Termination)为高阻状态。CKE 信号高电平有效后,将 ODT 信号置为静态的低电平或者高电平信号。

- 在 CKE 信号有效后,在发送 MRS 命令配置 MR 之前,延时最小 CKE 复位退出时间 tXPR。

- 控制器向 DRAM 发送 MRS 命令,配置 MRx

DDR4 配置 MRx 的顺序为 MR3-6-5-4-2-1-0 - 控制器向 DRAM 发送 ZQCL 命令,开始 ZQ Calibration

- 等待 tDLLK 以及 tZQ 时序后,也就是等待 DRAM 完成 ZQ Calibration。

- DRAM 初始化结束,可以进行读写相关的训练。

上电初始化 9 个顺序事件

接下来我们完全按照时间顺序来梳理下,将上电初始化流程划分为 9 个时间顺序的事件:

电源上电并稳定

- RESET_n 为低电平有效

- 保持 ODT 为高阻状态

- 延迟 <= 200 us - 10ns,置低 CKE 信号。高则置低,低则保持。

延迟至 200us

- 置高 RESET_n,撤除复位信号

- 延迟计数器清零

- 延迟 <= 500 us - 10ns, 产生稳定的 CK_t/CK_c 时钟输入

延迟至 500us

- 置高 CKE 信号

- 将 ODT 信号驱动为高电平或者低电平

- 延迟计数器清零

- 延迟 tXPR,发送第一个 MRS 命令

- 延迟 tMRD,发送下一个 MRS 命令,直至配置完所有 7 个 MR

- 延迟 tMOD,发送 ZQCL 命令

延迟 tZQinit,ZQ Calibration 完成,初始化完成

注意:在事件 7-8 的 MRS 和 ZQCL 命令之间必须插入 DES 命令,(Device Deselect 命令:CKE 与 CS_n 置高)

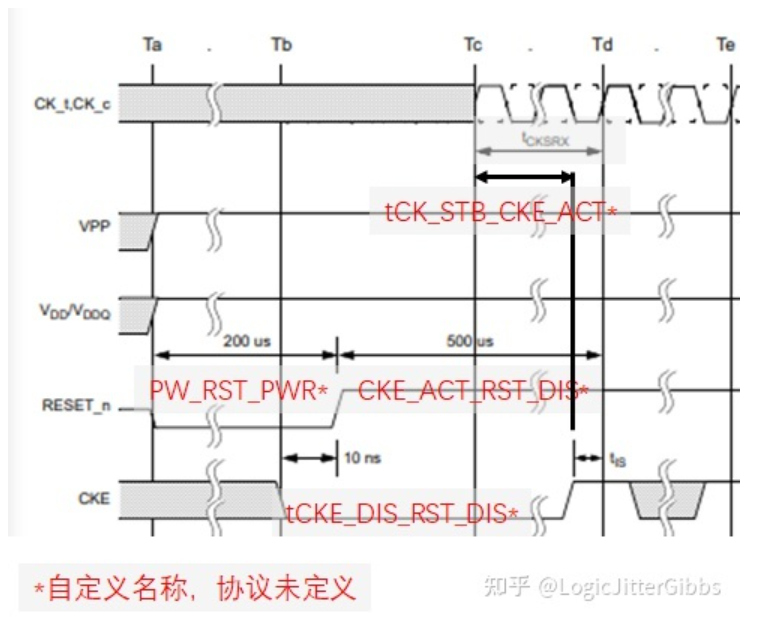

复位初始化流程 //Reset Initialization with Stable Power

这里的复位初始化特指的是电源稳定情况下的复位过程。上文讨论的则是电源上电触发的复位。

在 DRAM 运行的任意时刻,DRAM 控制器都可以置低 RESET_n 触发复位流程,将 RESET_n 电平降低至 0.2 * VDD 之下。此时,无需考虑其他 DRAM 接口信号的电平。

RESET_n 信号有效保持时间为 tPW_RESET。在 RESET_n 信号移除前至少 10ns,置高 CKE 信号,这与上电初始化的需求相同。

在 RESET_n 信号移除后,初始化流程也与上电初始化完全相同。

其他主题

最后,我们讨论几个和初始化有关的次级话题。

时序参数

初始化中有 5 个固定的时延参数,和其他几个随 DRAM 速率或者容量变化的时序参数。

固定时延参数

时序名,协议定义,中文释义,最小/最大/典型值,协议定义出处

tPW_RESET,RESET pulse width,复位脉冲宽度,1us (MIN),JESD79-4B- 8.6.1

tPW_RST_PWR, RESET_n need maintain during power-up Init,上电初始化复位信号需要保持的时长,200us(MIN),JESD79-4B- 3.3.1

tCKE_ACT_RST_DIS, RESET_n de-assert to CKE assert during Init,初始化中RESET_n 移除和 CKE 有效之间的间隔,200us(TYP),JESD79-4B- 3.3.1

tCKE_DIS_RST_DIS, CKE pull low before RESET_n de-assert during init,初始化中 CKE 置低与 RESET_n 移除的间隔,10ns(MIN),JESD79-4B- 3.3.1

tCK_STB_CKE_ACT, CK stable before CKE assert during init,初始化中 CK 稳定和 CKE 有效之间的间隔,MAX(10ns,5ntCK),(MIN),JESD79-4B- 3.3.1

协议中没定义名字,这是笔者自己取的

其他时序参数

下述是初始化过程中涉及的其他时序参数,这里不再展开:

- tXPR

- tMRD

- tMOD

- tZQinit

- tIS

- tCKSRX

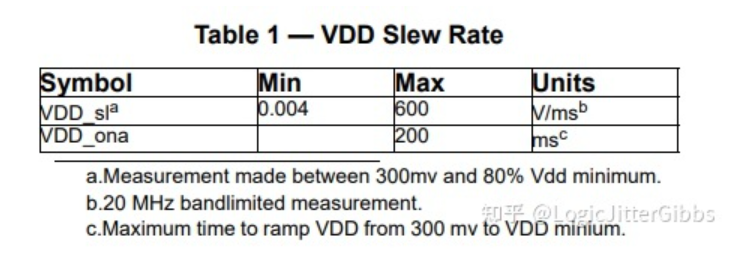

上电电源需求

上电时序和最大电压的需求

- 电压上升(ramp)期间,VDD ≥ VDDQ,但是 VDD 不能超出 VDDQ 0.3 V.

- VPP 电压必须和 VDD 同时或者更早地上升,并且 VPP 电压必须大于或者等于 VDD

- DDR4 VDD 典型工作电压值为 1.2V,VPP 为 2.5V

- VDD 和 VDDQ 必须由同一个外部电压转换电路驱动

- VTT 在电压上升期间完成后,最高电压不能超过 0.76V

- Vref CA 必须始终保持为 VDD/2.

电源电平变化率需求

DRAM VDD 引脚的电压 在从 300mV 上升到 0.8 * VDD.MIN时,上升率需要在 0.004 和 600 V/ms 之间。

从 300mV 到 VDD.MIN 的上升时间必须小于 200ms。

如果上升率采用协议上限的 600 V/ms,对于工作电压为 1.2V 的 DDR4 来说,300mV 上升到 0.8 * VDD.MIN 的时间大概为 1ns。

DDR3 与 DDR4 的区别

两者的上电与复位初始化区别不大,主要区别在于:

MR 数量和初始化 MR 顺序不同,两者都是不按顺序来的

- DDR4 初始化 MR 的顺序为 MR3-6-5-4-2-1-0

- DDR3 只有 4 个 MR,顺序为 MR2-3-1-0

在非上电复位流程中。RESET_n 有效的最小时长不同

- DDR4 设置了 tPW_RESET 时序参数,最小值为 1us

- DDR3 没有设置专门的时序参数,协议 3.3.1 节规定最小值为 100ns

电源方面

- DDR3 没有 VPP 电源

- DDR3 不区分 CAVref 和 DQVref,统称为 Vref,始终保持为 1/2 VDDQ

结语

本期我们讨论了:

- 上电与复位状态在 DRAM 工作状态机中的位置

- 上电初始化流程

- 复位初始化流程与上电初始化的差异

其他主题

- 初始化中三个固定的时延参数,和其他时延参数

- 上电过程中的电源需求

- DDR3 与 DDR4 的差异

关于作者

ljgibbs , 主业是某 Fabless 的 SoC Designer,业余时间是 OpenIC SIG 专栏作者与开源开发者。

感兴趣的领域包括:AXI 等片上总线、DDR、嵌入式系统与计算机架构、FPGA 、计算机网络通信、半导体行业与市场、翻译&写作、电影&历史。

关于《DDR 学习时间》专栏

在 DDR 学习时间专栏中,目前有几个 Part:

- Part-A DRAM 课程、论文以及其他在线资源的学习

- Part-B 基于 DDR4 Spec 的 DDR 特性学习

- Part-D DRAM 系统的调试、验证与测试

- Part-Z DRAM 相关杂谈

计划开设下一个 Part

- Part-S DDR 仿真与实例

关于连载《DDR 学习时间》专栏的 OpenIC SIG

OpenIC SIG(简称 OICG),开源数字 IC 特别兴趣小组,致力于分享开源项目与知识。

欢迎关注/支持/加入我们!contact_us@digitalasic.design

DDR 学习时间 - OpenIC SIG 开源数字IC技术分享

转载自:知乎

作者:LogicJitterGibbs

推荐阅读

- PCI Express Technology 3.0:地址空间与事务路由4.5-4.6小节(完)

- PCI Express Technology 3.0:地址空间与事务路由 4.3-4.4节

- PCI Express Technology 3.0:地址空间与事务路由4.1-4.2节

更多招聘及面经请关注FPGA的逻辑。