使用Verilog可以方便地实现复杂的设计。现在,设计复杂性增加,设计需要针对低功率、高速和最小面积进行优化~

ALU设计

算术逻辑单元(ALU)在大多数处理器中用于执行算术和逻辑运算。处理器根据操作代码(opcode)一次执行一个操作。对于8位处理器,ALU用于对两个8位操作数(Operand,操作数是需要对其执行操作的数据)执行操作。同样,对于16位处理器,ALU用于对两个16位数字执行操作。

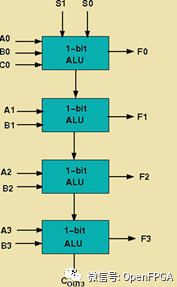

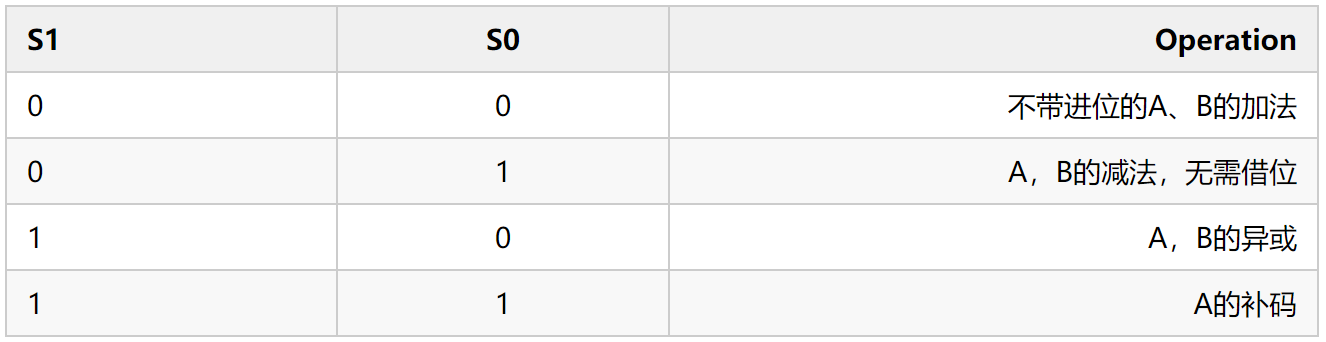

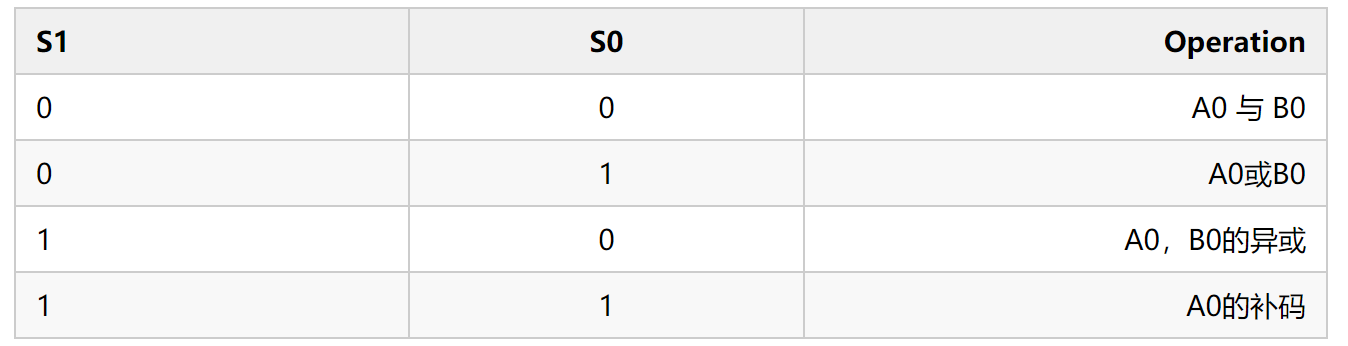

如图7.1所示,ALU体系结构用于对两个四位数字A(A3为MSB,A0为LSB)、B(B3为MSB,B0为LSB)和进位输入C0执行操作,ALU生成输出F(F3为MSB,F0为LSB)和输出Cout3。在实际的基本设计方案中,设计一位运算器来对单个数据位执行操作。根据S1、S0指定的操作码位执行该操作。如图所示,ALU设计用于执行四条指令。表7.1对ALU和功能进行了说明,这些操作取决于所选线路“S1”和“S0”的状态。在此示例中,操作码为2位,由“S1”和“S0”表示。

图7.1四位ALU体系结构

表7.1四位ALU真值表

逻辑单元设计

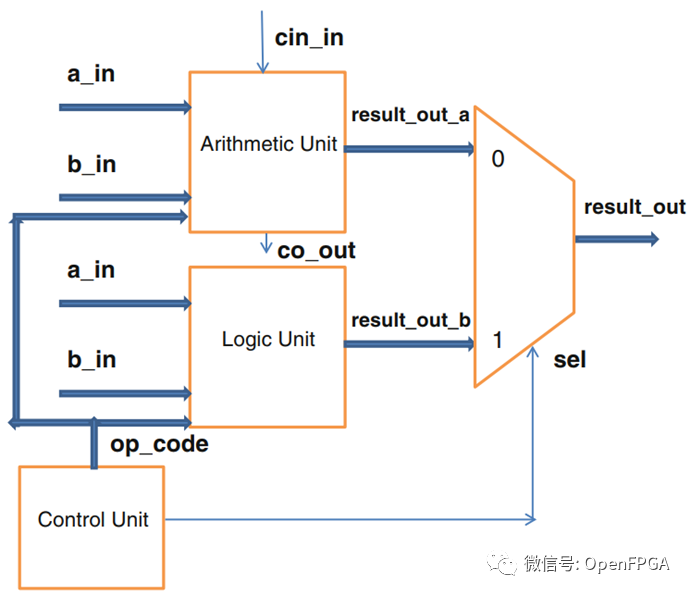

在实际的ASIC/FPGA设计场景中,建议使用有效的Verilog RTL描述设计功能。因此,在微体系结构层面,设计被划分为多个模块。设计的划分为设计师提供了更好的理解和可视性。考虑一个场景来实现8位ALU的设计功能,该设计被为单独的逻辑单元和算术单元。可以通过使用高效的Verilog RTL来描述单独的算术和逻辑单元功能,以获得更好的可读性和更好的综合结果。

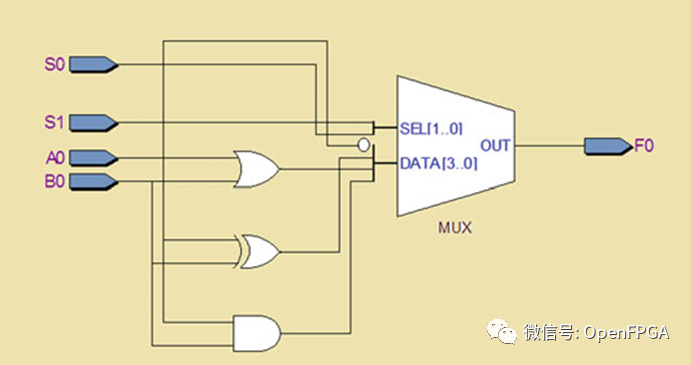

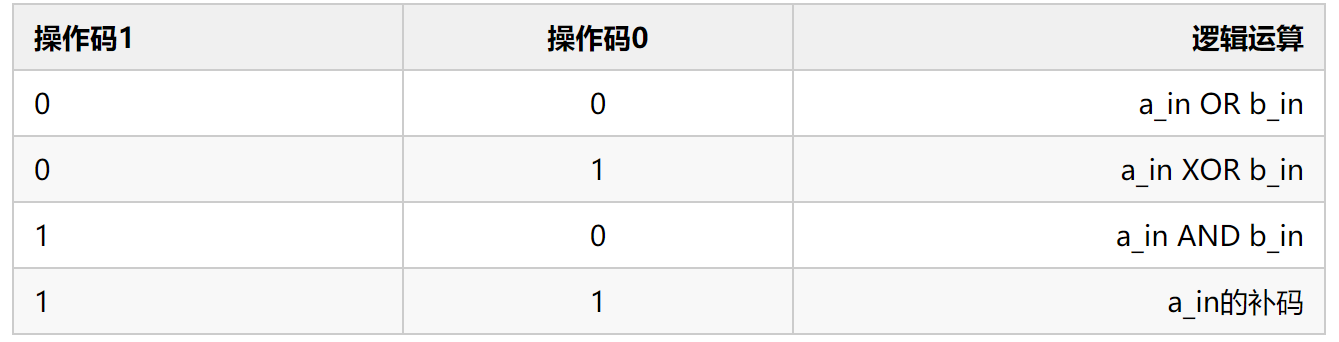

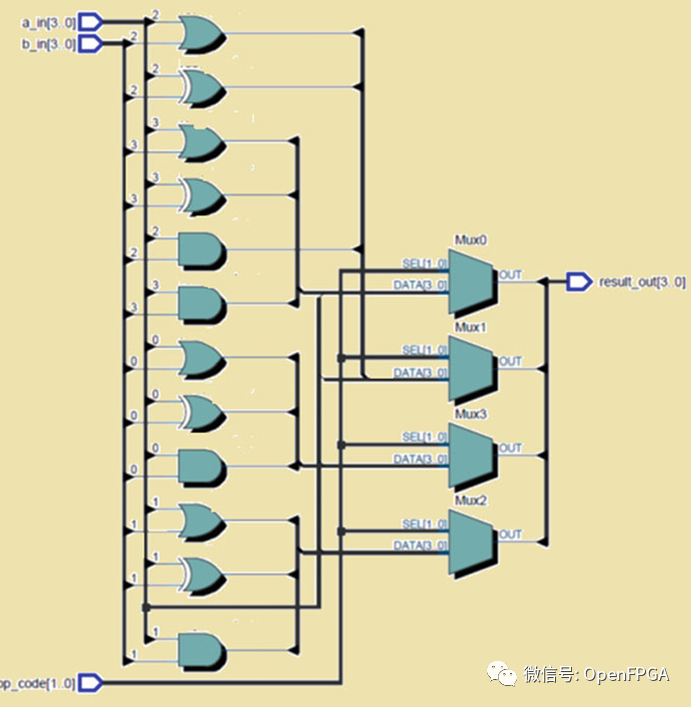

图7.2如下所示,用于实现四个逻辑操作,这些逻辑操作在功能表中进行了描述。逻辑单元是执行AND、OR、XOR或补码运算。下表7.2描述了不同的逻辑操作。通过使用一个输入A0和另一个输入逻辑“1”的加法器执行补码运算。

这种设计的问题是由于使用了并行和多路复用逻辑,这种技术效率很低,因为它需要更多的面积和功率,没有有效的实施机制。如果“S1”、“S0”是延迟到达的信号,并且如果在寄存器中使用该块来寄存器路径,则可能存在时序冲突。另一个重要方面是本设计中未使用的资源共享概念。下面示例描述了从输入A0和B0到多路复用器数据输入的数据路径,控制路径是多路复用器“S1”和“S0”的控制线。如图7.2所示,逻辑单元一次执行所有操作,其中一个操作结果的结果为“F0”。

图7.2单位逻辑单元

表7.2单位逻辑单元操作表

因此,建议使用“case”构造,通过共享公共资源,为逻辑单元编写有效的Verilog RTL。下一节描述逻辑单元的Verilog RTL,以推断并行逻辑和具有寄存器输入和输出的逻辑。

用于推断并行逻辑的逻辑单元

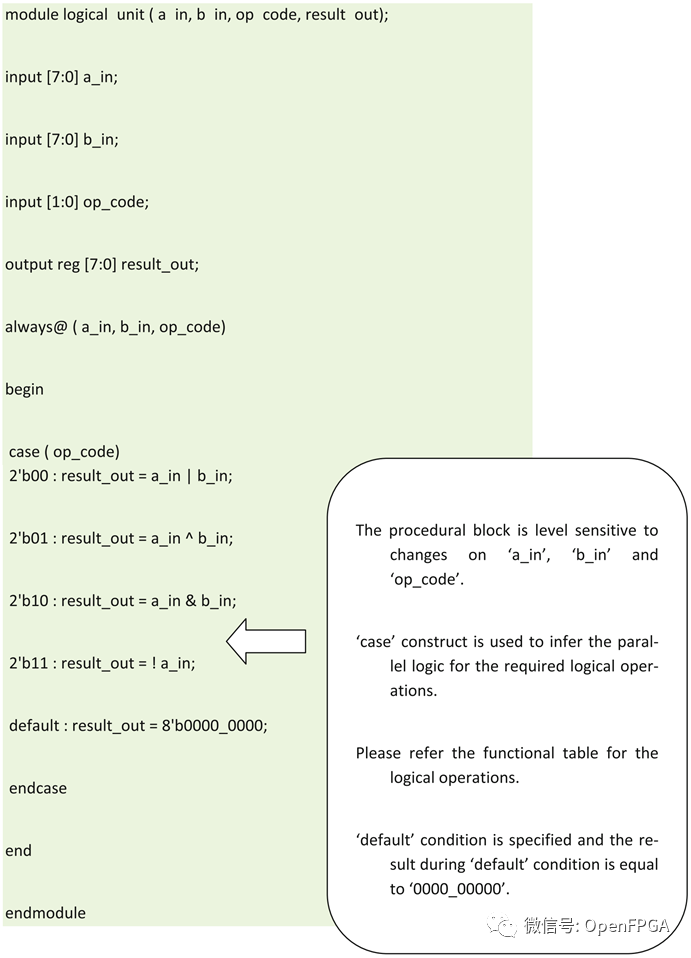

示例7.1描述了对两个8位二进制输入“a_in”和“b_in”执行操作的功能。使用表7.3中描述的功能执行操作。Verilog RTL使用乘法器编码推断并行逻辑。

如例7.1所述,通过使用带有“case”结构的程序“always”块来描述功能。描述了所有情况条件,在“default”条件期间,逻辑单元生成等于“8”b0000_0000”的输出“result_out”。

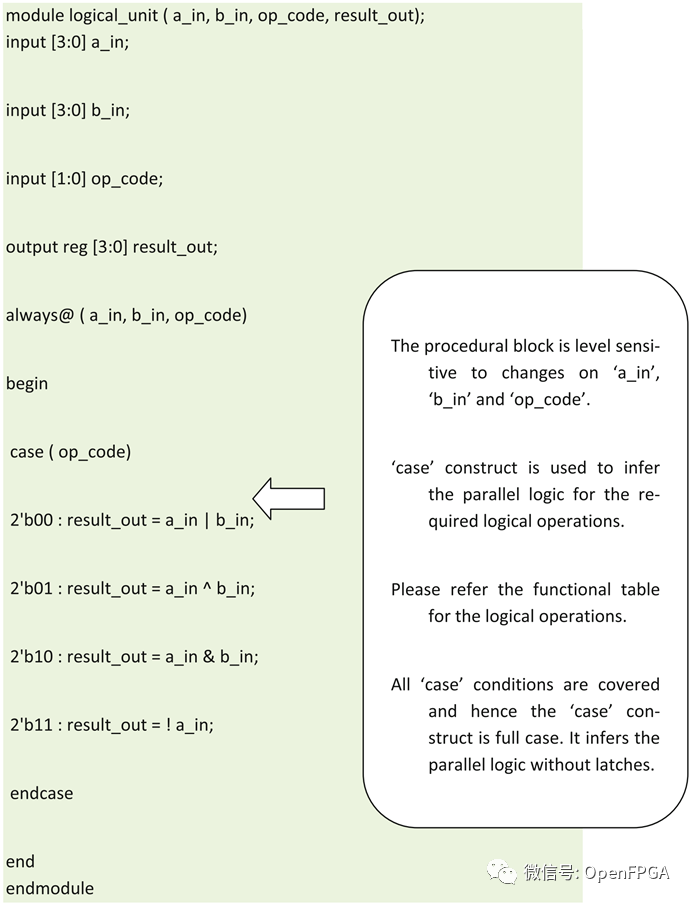

逻辑单元的功能可以使用full-case构造进行建模。如例7.2所述,通过使用带有完整“case”结构的程序“always”块来描述功能。所有case条件都使用full-case结构进行描述。

图7.3所示为使用8位逻辑单元的full-case结构的综合逻辑。如上图所示,它推断出具有多路复用逻辑的逻辑门。在实际场景中,建议使用加法器作为公共资源来实现逻辑和算术单元。

表7.3表8位ALU操作表

示例7.2使用full-case构造的8位ALU的Verilog RTL

图7.3 8位逻辑单元的综合逻辑

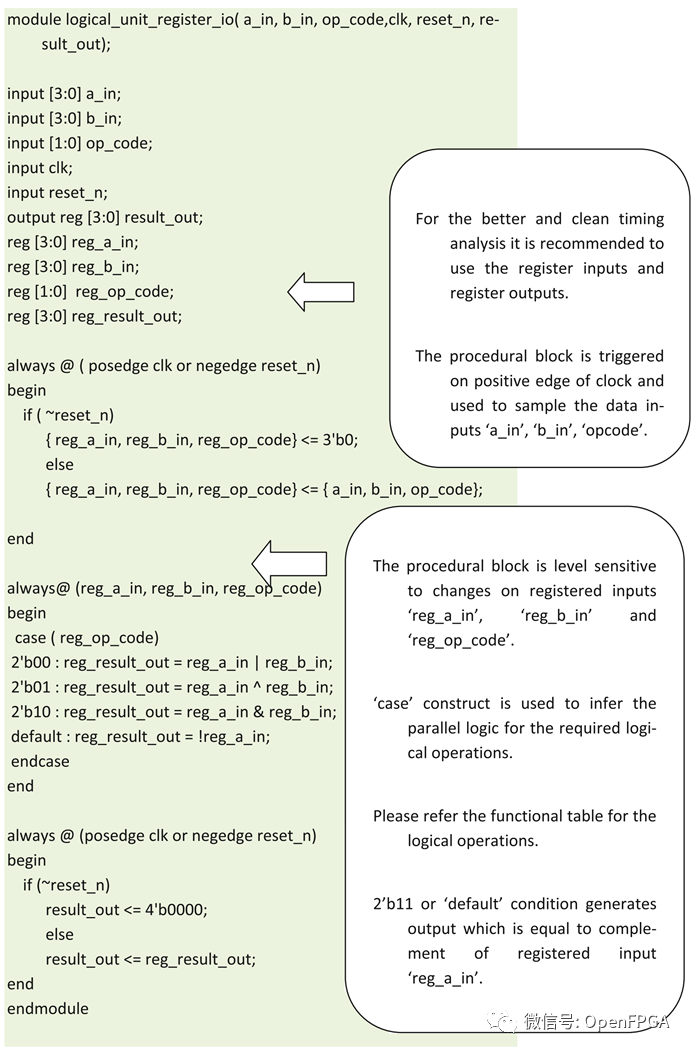

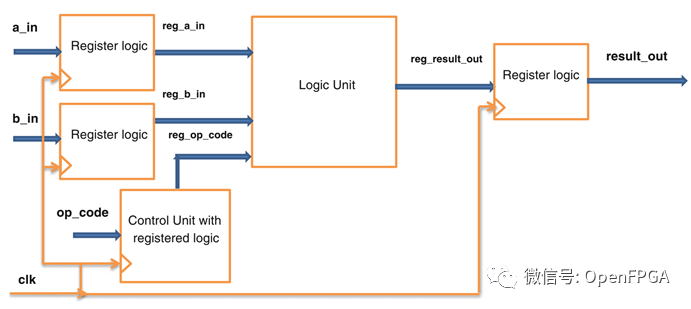

具有寄存器输入和输出的逻辑单元

为了高效和干净的时序分析,建议使用寄存器输入和寄存器输出。如果所有输入都是在时钟的活动边缘上采样的数据,并且所有输出都是在时钟的活动边缘上寄存器和捕获的,那么该设计可以更好地分析寄存器到寄存器的时序路径。寄存器输入和寄存器输出可提供干净的数据路径,这样的输出就是无故障或无危险(glitch or hazard free)。为了提高性能,可以使用流水线来减少数据到达时间。有关定时分析的详细信息,请参阅后面文章。

示例7.3使用寄存器输入和寄存器输出逻辑。在时钟“clk”的正边缘对输入进行采样或捕获。在复位条件“reset_n=0”期间,逻辑单元被初始化为逻辑“0”。

示例7.3带寄存器输入和输出的8位逻辑单元的Verilog RTL

图7.4具有寄存器输入和输出的综合逻辑单元

上面的示例生成逻辑单元,所有输入和输出都记录在时钟的正边缘。读者需要假设每个寄存器都有一个异步复位输入“reset_n”。综合逻辑如图7.4所示。

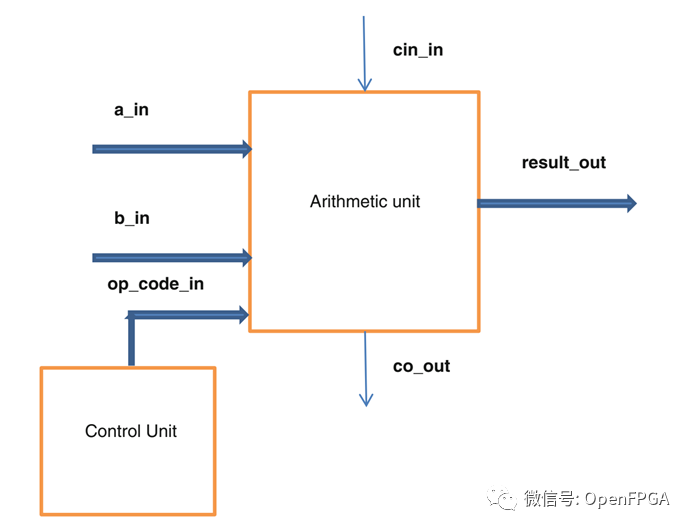

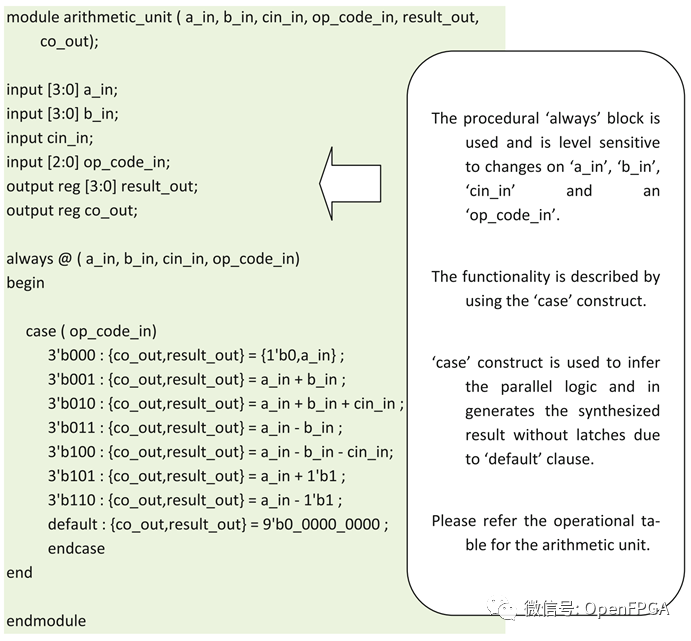

算术单元-ALU

算术单元用于执行加法、减法、增量(自增++)和减量(自减--)等算术运算。这些操作在两个不同的操作数上执行。功能表7.4给出了需要执行的不同操作的相关信息。算术单元一次只执行一个操作。图7.5描述了不同输入和输出信号的信号连通框图(示例7.4)。

表7.4算术单元的运算表

图7.5ALU单元框图

示例7.4算术单元的Verilog RTL

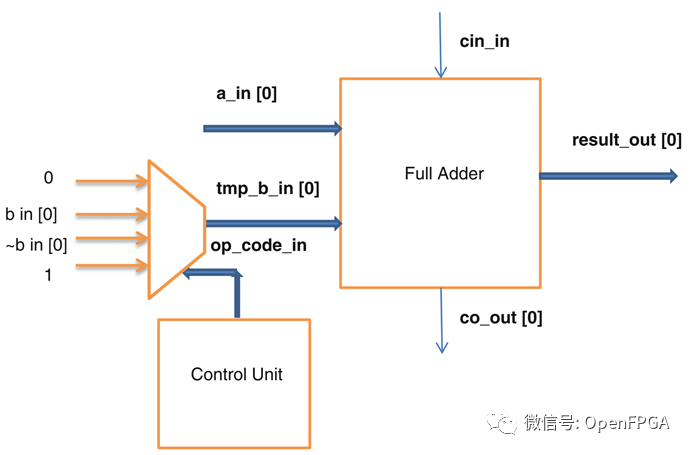

图7.6一位算术单元综合结果

一位算术单元的综合逻辑如图7.6所示。该逻辑使用全加器作为执行加法和减法运算的部件。使用2的补码加法执行减法。综合逻辑还包括多路复用器4:1,根据操作码在全加器的一个输入端传递所需的操作数。

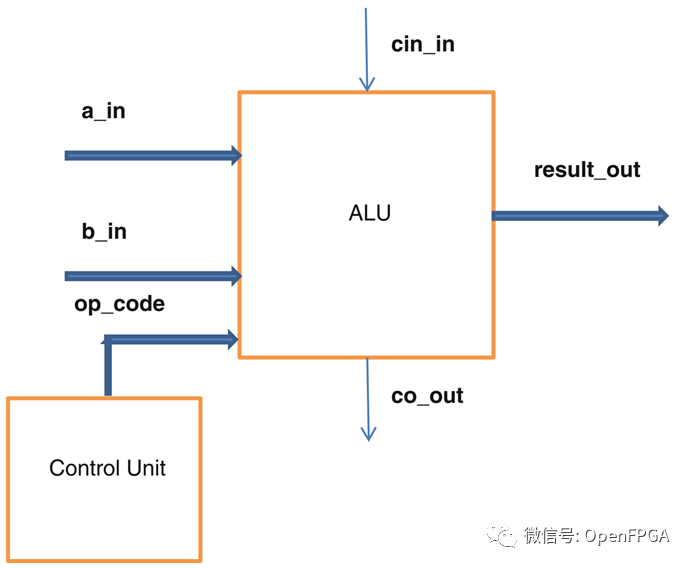

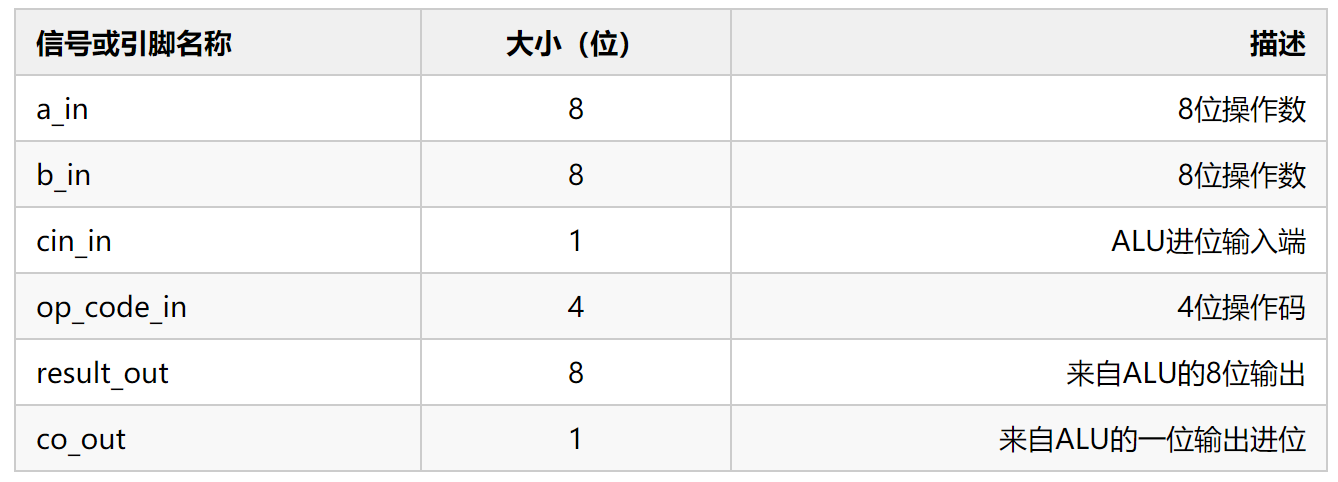

算术和逻辑单元

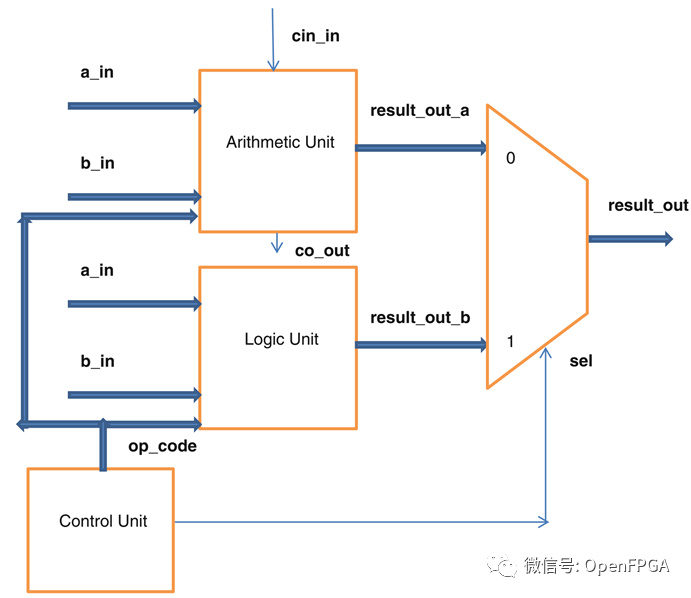

图7.7说明了ALU及其相关逻辑电路,用于对两个8位数字“a_in”和“b_in”执行操作。对于逻辑运算,将忽略进位输入(cin_in),并根据指令的操作代码生成输出“result_out”。根据操作代码,ALU可以执行算术或逻辑运算。在算术运算期间,若结果大于8位,则进位输出“co_out”设置为逻辑“1”,表示进位传播超出MSB(表7.5)。

表7.6描述了11条指令的ALU设计在输入和输出端所需的位数。该表描述了七条算术指令和四条逻辑指令。引脚或信号说明如表7.5所示。

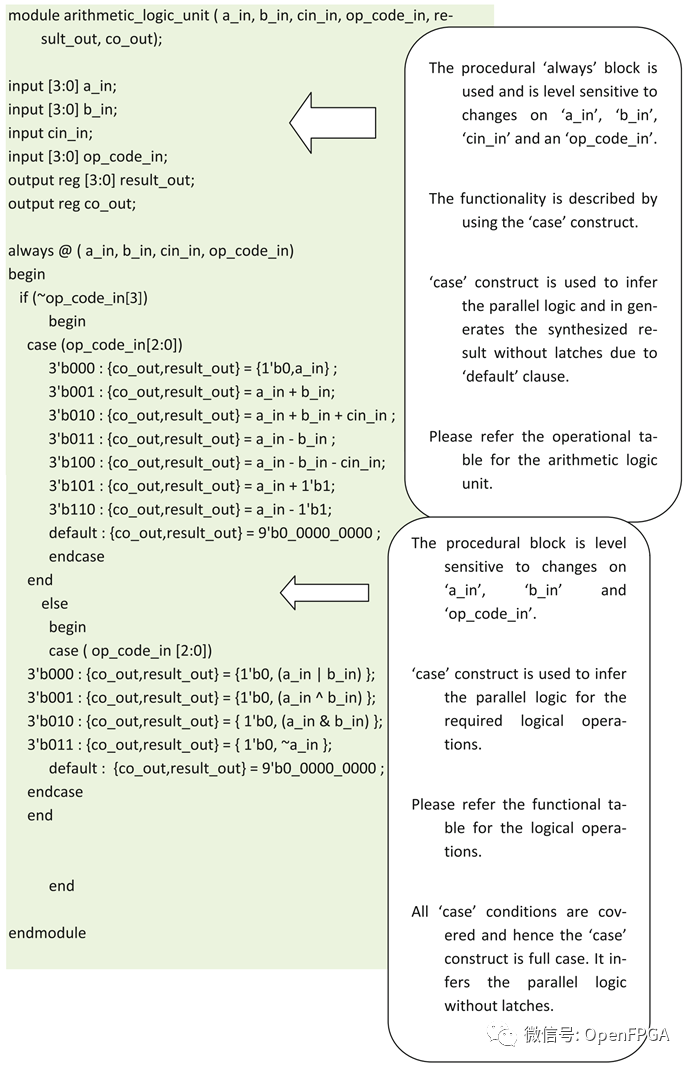

示例7.5中描述了使用两种不同的“case”结构来推断并行逻辑的有效Verilog RTL描述。对于 “op_code_in[3]=0” 执行算术运算,当op_code_in[3]=1时,它执行逻辑运算。

图7.7 ALU顶层图

表7.5 8位ALU的信号或引脚说明

表7.6 8位ALU的操作表

示例7.5 8位ALU的Verilog RTL

图7.8综合的8位ALU

8位ALU的综合图如图7.8所示。如图所示,它由算术运算和逻辑运算的并行逻辑组成。在输出端使用多路复用器生成算术或逻辑运算结果。该逻辑没有使用资源共享和面积、功率优化。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。