神经网络加速器设计需要了解的那些事

注:以下分析均基于参考文献[1]。

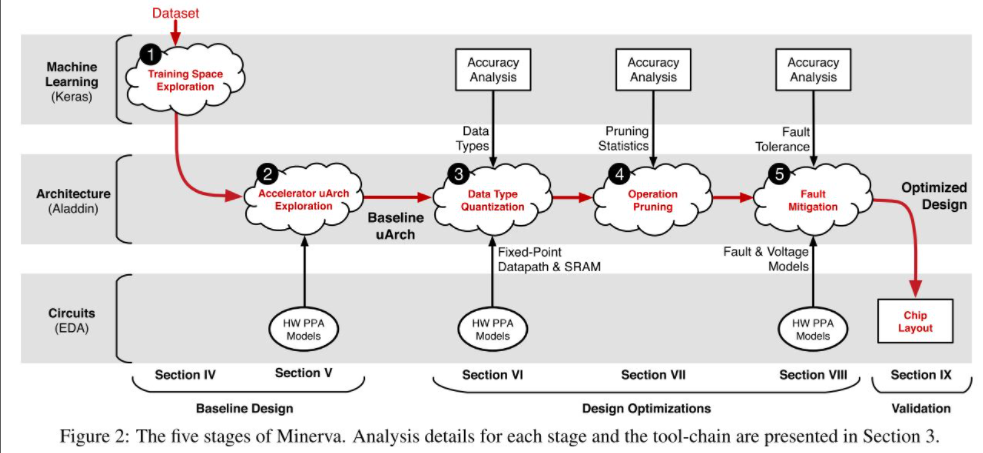

Minerva这篇文章介绍了一种当前低功耗神经网络加速器设计的方法。同时,本文结合该方法,利用当前设计低功耗神经网络的技术,设计了一个低功耗的神经网络推断加速器。Minerva给出的设计方法非常具有参考价值,它的设计流程是我们设计加速器时应该遵守的。Minerva的设计流程如图1(原文Figure 2)所示,把设计加速器的流程分成3个层次——软件层,体系结构层,电路层。

图 1

- 软件层:软件层设计就是设计算法并利用高级程序语言实现,软件层建模的优势在于可以高效地对算法的性能经行评估,如数据量化、剪枝、降低SRAM电压等优化后的精确度评估。从图1的设计的流程图就可以看出来,优化算法如果先在软件层次上先进行验证,再布署到体系结构层面上,能提高设计的效率。

- 体系结构层:体系结构层次的设计是连接软件层和电路层的桥梁,把一个复杂的算法直接变成硬件电路是很困难的。设计电路实现某个算法的时候,应当考虑如何更合理、更高效地部署自己的硬件,如:是否采用流水线进行一系列的运算,计算过程的中间值是否需要先写回到存储器中。体系结构层次的设计会影响电路的PPA(Power-Performance-Area),因此这一层次的仿真建模在设计加速器时也是必不可少的。

- 电路层:电路层次的设计实现就包含了硬件描述语言的建模实现,后端版图的设计实现。电路层次的实现就是将加速器实现为一个固定的硬件电路,之前在软件层和体系结构层的仿真都会在这里得到验证,得到最终的结果。

从图1的体系结构层可以看出,该论文使用3种方法优化神经网络加速器的功耗。数据量化,采用动态定点的办法,即网络中每一层参数的值的小数点所在位不同(确保整数部分不溢出),使用尽量小的数据位宽,如图2(原文Figure 7)。

图 2

- 剪枝。该论文使用的就是常规的剪枝方法,剪枝能够减少网络的参数规模和计算量,有利于实现低功耗的加速器。但是并没有提到稀疏性问题。降低SRAM的电压。

- 降低电压是低功耗技术的一种,但是低电压会让数字信号的噪声容限变低,最终导致在读取SRAM时错误率提高,从而影响神经网络的精度,如图3(原文Figure 10)所示,本文以手写数字识别的DNN算法为例,对比了No Protection、Word Masking、Bit Masking三种情况,SRAM读取错误率对神经网络精度的影响。Word Masking是在检测到亚稳态时将这次读到的数据位全部置0,Bit Masking是检测到亚稳态时用符号位代替错误的数据位。本文使用的是Bit Masking,这个方法效果好,但是更复杂。(至于怎么检测,论文没提到,我也不清楚,欢迎讨论)

图 3

总结:本次论文提出的关于神经网络加速器的设计方法,我觉得是非常通用和值得借鉴的。我们之前写着玩的一个神经网络加速器的问题就是没能够对算法进行正确的评估,同时缺少体系结构层面的建模,导致我们每次有新的想法都去改RTL,效率很低,并且可靠性不够。还是要多学习优秀的设计思路。

参考文献

[1] B. Reagen et al., “Minerva: Enabling Low-Power, Highly-Accurate Deep Neural Network Accelerators,” in Proceedings of the 43rd International Symposium on Computer Architecture(ISCA), 2016, pp. 267–278.

窥探神经网络加速器的数据复用

注:本文所有分析均基于参考文献。

1. Deep convolutional neural network architecture with reconfigurable computation patterns[1]

针对深度卷积神经网络,很多加速器的设计是基于一种固定的计算模式(computation pattern),在应对不同规模的网络时,会出现资源利用率低、存在无用访存操作等问题。本文提出了一种DNA(Deep Neural Architecture)结构,通过算法和硬件协同优化达到针对不同模型可重配置计算模式的目的。对AlexNet,针对每一层的不同特点,对每一层的操作进行不同的配置后, 将大大节约访存时间和能耗。从算法来看,介绍了3种数据复用模式,如图1。

图 1

根据循环嵌套顺序的不同,数据复用模式可以分为Input Map复用、Weight复用、Output复用。不同的复用模式在硬件层面做成可配置的计算模式,针对不同的模型便可以实现提高资源利用率的效果。

图2和图3介绍了Convolution Mapping的一种常规方法OOM(Output Oriented Mapping)及其局限性,并介绍了一种方法POOM(Parallel Output Oriented Mapping)提高资源利用率。

图 2

图 3

在硬件架构设计上为了实现可重配置的功能,设计了如图4的data path。

图 4

图4(a)中绿色和红色的部分体现了3种数据复用模式(IR、WR、OR)。图4(b)中的Data Sharing Level也体现出了图3中介绍的Mapping方法。图5是测试结果,可以看出在可重配置计算模式的实现下,Buffer access, DRAM access, total energy都有明显的减少,说明DNA架构在提高资源利用率和减少访存上是有明显作用的。

图 5

结果分析:对每一层的数据复用模式(计算模式)进行不同的配置后,与把所有层的计算模式配置成同一种固定模式相比,能很明显地节约数据搬运的消耗。因为传统方法对data buffering要求很高,所以需要经常访问DRAM,而全连接层一次需要用大量的权重进行计算,所以配置成WR模式。总结:本文核心思想便是通过设计可重配置的硬件结构来解决单一模式加速器资源利用率低、访存存在很大浪费的问题,从最后的结果看来,针对神经网络每一层的不同特点配置计算模式,将很大程度上改善这两个问题。

2. Understanding Reuse, Performance, and Hardware Cost of DNN Dataflows: A Data-Centric Approach[2]

这是今年Micro的一篇很硬核的论文。过去的很多有关编译分析工具的工作都是在分析如何将DNN模型部署到给定的硬件架构上,没有阐明软件映射和硬件数据流之间的关系。本文提出了一种Data-Centric方法,并设计了MAESTRO(Modeling Accelerator Efficiency via Spatio-Temporal Reuse and Occupancy)用于在给定DNN模型和硬件配置时,不同数据流对运行时间和功耗的影响。数据复用的很多背景知识在前一篇文章中已有介绍,本文的重点是用他们设计的指令来描述一个数据流。图6便简单说明了把循环嵌套用data-centric的方法描述。

图 6

关于MAESTRO更具体的内容见图7。

图 7

它的输入描述性文件有3个部分:硬件资源、data-centric方法下的数据流、DNN model。在经过它的一系列tensor analysis, cluster analysis, reuse analysis, performance analysis, cost analysis后输出Performance和cost的分析报告,重点关注的就是运行时间和功耗。测试时使用MAERI和Eyeriss两篇文章中的硬件结构,DNN选择AlexNet和VGG16,分别使用MAESTRO和RTL仿真,测试结果误差很小(绝对误差3.9%),见图8。

图 8在文章最后还介绍了一种基于MAESTRO的工具design space exploration tool(DSE),此工具可以根据输入的面积和功耗限制,去搜索4种硬件参数的最优解(the number of PEs, L1 buffer size, L2 buffer size, and NoC bandwidth),不过关于DSE介绍得很少,有兴趣可以自行阅读。这个工具能快速的搜索设计空间是因为它可以跳过很多invalid搜索(算法上应该做了剪枝)。总结:不同的数据复用模式对网络在硬件上的运行时间和能耗开销有很大影响,本文提出的工具对不同硬件数据流在不同的硬件结构上运行的效果进行分析,误差很小。这种思路可以在很多方面借鉴,具体欢迎讨论。题外话:我对于这种方法性的工作是非常崇拜的,私以为这样好的工作必须是对硬件架构、算法设计非常熟悉的人才能做出来,所以还要多努力啊...

参考文献

[1] F. Tu, S. Yin, P. Ouyang, S. Tang, L. Liu, and S. Wei, “Deep convolutional neural network architecture with reconfigurable computation patterns,” IEEE Trans. Very Large Scale Integr. Syst., vol. 25, no. 8, pp. 2220–2233, 2017.

[2] H. Kwon, P. Chatarasi, M. Pellauer, A. Parashar, V. Sarkar, and T. Krishna, “Understanding Reuse, Performance, and Hardware Cost of DNN Dataflows: A Data-Centric Approach,” in Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture, 2019, pp. 754–768.

END

知乎:

https://zhuanlan.zhihu.com/p/91258132

https://zhuanlan.zhihu.com/p/88927564

推荐阅读

更多内容请关注其实我是老莫的网络书场专栏