绪论

2018年第23届Asia and South Pacific Design Automation Conference(ASP-DAC)的Tutorial-3的题目为_Machine Learning for Reliability Monitoring, Mitigation and Adaptation_[1]_,_即使用机器学习来监测、缓和与自适应成电路中的各种可靠性问题。在此Tutorial中,集成电路可靠性的相关技术被机器学习分割为了两个部分,一部分是非机器学习的传统监测手段,一种是以机器学习为基础的老化监测、缓和与自适应。Tutorial将大部分篇幅花在了机器学习相关的老化监测介绍上,而对于传统的技术手段则以列举几个例子而简略带过,此专栏会按照这个Tutorial的结构,从头到尾详细说明现有的集成电路可靠性相关的技术方法。

纳米尺度下的集成电路可靠性机制

Tutorial从几个方面总结了纳米尺度下的集成电路可靠性机制:

- 电路老化

- 软错误与噪声

电路老化

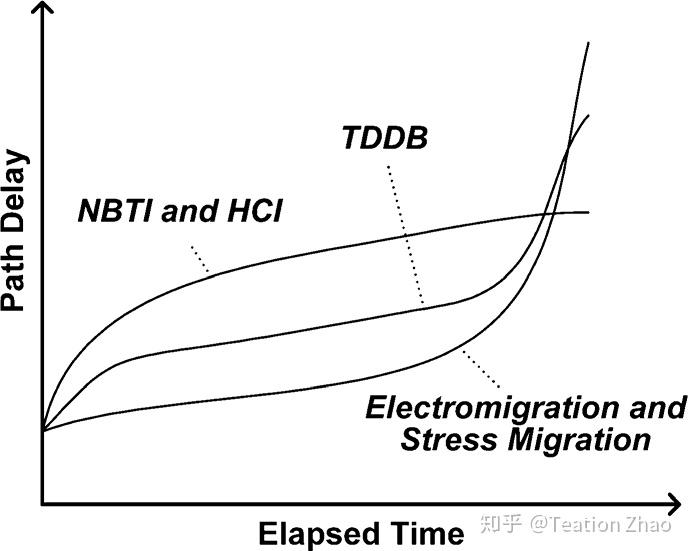

电路老化是指集成电路中的硬件在工作过程中部分特征参数随着时间退化,可以简单的总结为晶体管老化导致阈值电压升高,最终导致晶体管失效以及金属线老化导致电阻升高最终断裂。而晶体管的老化机制在纳米尺度下有三个主要效应占据主导,分别是:Bias Temperature Instability(BTI,偏压温度不稳定性),Hot Carrier Injection(HCI,热载流子注入)以及Time Dependent Dielectric Breakdown(TDDB,经时介质击穿)。而互连线的老化则表现为Electro-migration(EM,电迁移)。电路老化带来的是电路硬件上的参数退化,最终结果都是无法避免的电路失效。如下图1[2]所示,并且从短期来看,影响集成电路特征参数的老化效应主要是NBTI与HCI,而从长期来看,最终导致集成电路失效的效应则可能是TDDB与EM。

图1 各种老化效应的比较

- BTI

BTI中占主导地位的则是NBTI(Negative BTI),这是一种发生在PMOS中的效应,硅表面的空穴被Si-SiO2界面的Si-H键输入,当H原子分离,产生界面态,向介质中扩散,产生一个正电荷,导致晶体管阈值电压退化。NBTI存在两个阶段:压力阶段与恢复阶段。晶体管打开时,Si-H在电场作用下持续断裂,H持续向氧化物介质中扩散,导致阈值电压的持续退化,为压力阶段;而当晶体管关断,H从氧化物中向界面反向扩散,重新形成Si-H键,表现为阈值电压恢复,为恢复阶段。在电路中,BTI主要受到晶体管占空比(SP,Signal Prabability)的影响[3]。

- HCI

HCI是由于载流子在沟道中受到漏极附近强大的沟道电场的作用,导致其越过Si-SiO2势垒注入到氧化物介质中形成陷阱,造成阈值电压的退化。与BTI不同的是,HCI没有恢复阶段,因此HCI造成的老化是不可逆的。在电路中,HCI主要受到晶体管翻转率(SA,Switch Activity)的影响[4]。

- EM

EM是电路中金属线中的电子与金属原子发生物理碰撞,导致金属原子的移动,进而形成金属上的空洞,导致电阻增加,最后导致金属线的断裂。

- TDDB

TDDB是指MOS管在正栅压下的Na离子发射,由电场的驱动飘逸至Si-SiO2界面,聚居于界面缺陷内,导致局部Na离子浓度升高,局部电场增强,引起局部的隧道击穿,最终导致介质击穿。

软错误与噪声

在晶体管受到高能粒子辐照的时候,可能会发生电平翻转,导致软错误的发生。软错误具有一定的自限性,比如翻转的晶体管其电平没有被读取就被重新赋值,或者电路中存在ECC/EDC容错机制,能够有效地抑制辐照造成的软错误。一个典型的噪声是Power Supply Noise(PSN,电源噪声),电路中的电源电压并不是理想的一个稳定的值,而是处于一个不停波动的状态,电源噪声会带来IR voltage drop等负面效应。

软错误与噪声都不会带来电路硬件参数上的退化,这也是这两个效应同样作为可靠性因素与电路老化的区别。

集成电路老化监控技术分类

Tutorial除了以机器学习为分界线外,还将传统老化监测技术分为两大类,总共三类,分别是:

- In-situ Sensors(原位老化传感器)

- Replica Circuits(备份电路/金丝雀电路)

- Machine-Learning Techniques(机器学习技术)

In-situ Sensors

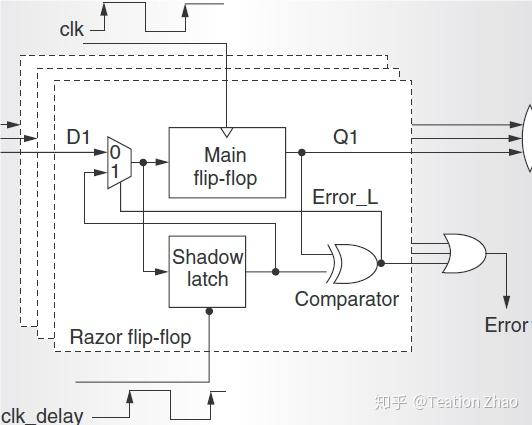

原位传感器的概念是相对于备份电路存在的,即传感器直接放置在被监测的关键路径/电路模块里,能够直接测量被测电路的相关电路参数,例如关键路径的路径延迟、SRAM中的阈值电压等等,Tutorial直接列举了三个例子来说明原位传感器,分别是如图2所示的Razor Flip-flop[5],Canary Flip-flop[6]以及Early Capture Scan Cell[7],但原位传感器技术作为可靠性的一个关键技术路线,其内容完全不止如此,还可以分类为老化预警与延迟测量,其中老化预警的代表性论文就是Razor Flip-flop与Canary Flip-flop,以延迟时钟/延迟数据路径来得到一组被测信号与正确信号,通过比较两个信号值之间的差异,得到错误信息;而延迟测量则是通过延迟链或者将关键路径接成环形振荡器来得到路径当前的电路延迟信息,进而对电路老化进行预测。

图2 Razor Flip-flop

原位传感器这种技术手段的优势,相较于备份电路,在于能够直接在真实环境中测量电路参数,得到的结果相对而言更加可信,能够避免PVT(工艺、电压、温度)对测量带来的影响。其缺点也明显,由于原位传感器需要放置在被测路径里面去,则需要对电路设计本身进行修改或插入,对原电路的布局布线与时序收敛造成影响,对电路性能造成不可忽视的影响。

Replica Circuits

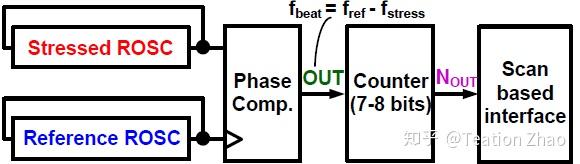

相对于原位传感器,使用一个原电路中的关键路径的复制电路/相似电路,放置于原电路旁但与原电路相隔离,由于复制电路与原电路相隔离,不在设计中执行任何功能,因此对复制电路的测量相对而言更加方便和丰富,通过测量复制电路在特定负载情况下(大于或等于原电路的工作负载)的老化状况,以推测原电路的老化程度。这样做的好处则是能够对备份的电路的参数进行更加细致的测量且不会对原电路的性能造成任何影响。备份电路也可以大致分类两类:基于反相器链/延迟链/关键路径电路复制的备份电路,另一个是基于环形振荡器的备份电路。但是随着研究者们的研究的深入,发现备份电路存在精度低的问题,由于备份电路独立放置于原电路旁,其V、T两个条件近似相等,但是P即制造工艺上的区别却无法忽视,制造工艺上的误差会带来两个相同的电路老化速率不同,进而导致备份电路的测量精度下降,这也是原位传感器相对于备份电路的一个巨大优势,因为原位传感器直接测量原电路,不受 PVT的影响。典型的备份电路如下图3所示的环形振荡器[8]。

图3 Ring Oscillator Surrogate Cirtuits

Machine Learning Techniques

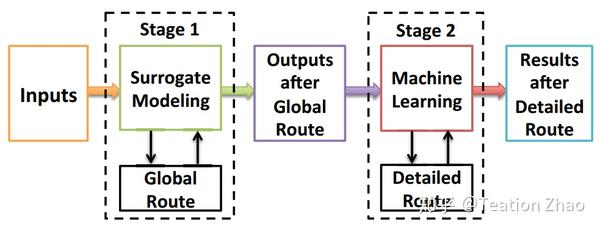

基于机器学习的可靠性技术主要应用在两方面。第一方面是对老化延迟或软错误率等可靠性物理指标的细粒度预测,相比于原位监测器与复制电路的方法,机器学习的方法更多考虑了系统运行过程中工作量对系统可靠性的影响,从而在设计阶段对大量的工作量数据与可靠性量化数据进行训练,得到一个关于工作量与可靠性之间的预测模型。进而在系统运行阶段,利用硬件对工作量数据实时监测,并将数据反馈给软件模型进行可靠性的预测。这种方法可以在没有明显的老化延迟或软错误发生的情况下,细粒度对系统可靠性进行预测,但其有效工作的条件之一是电路实际的工作量与训练时采用的可预期的工作量是相关的,这可能不适合经常执行一些特殊工作量的系统,并且这种方法得到的并不是真实的可靠性数据,而是模型预测的结果。第二方面是老化监测中关键路径的选取,待监测关键路径受工作条件、工作量等诸多在设计阶段无法考虑在内的因素影响,因此利用机器学习技术可以更好的在系统运行过程中将这些因素考虑在内,动态选择具有不同特征的待监测路径对象,典型例子如图4所示的使用机器学习进行超大规模集成电路布线[9]

。

图3 机器学习在超大规模集成电路中布线的应用

参考

- ^J. Xiong, "Tutorial-1: Machine learning and deep learning," 2018 23rd Asia and South Pacific Design Automation Conference (ASP-DAC), Jeju, 2018, pp. 19-25.

- ^Y. Sato et al., "A circuit failure prediction mechanism (DART) for high field reliability," 2009 IEEE 8th International Conference on ASIC, Changsha, Hunan, 2009, pp. 581-584.

- ^W. Wang, S. Yang, S. Bhardwaj, S. Vrudhula, F. Liu and Y. Cao, "The Impact of NBTI Effect on Combinational Circuit: Modeling, Simulation, and Analysis," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 18, no. 2, pp. 173-183, Feb. 2010.

- ^A. Bravaix, C. Guerin, V. Huard, D. Roy, J. Roux, and E. Vincent, “Hot-carrier acceleration factors for low power management in DC-AC stressed 40nm nMOS node at high temperature,” in Reliability Physics Symposium, 2009 IEEE International. IEEE, 2009, pp. 531–548.

- ^Ernst, Dan, et al. "Razor: circuit-level correction of timing errors for low-power operation." IEEE Micro 24.6 (2004): 10-20.

- ^Shah, Nimay, et al. "Built-in proactive tuning system for circuit aging resilience." . IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, 2008. DFTVS'08.

- ^Yi, Hyunbean, Tomokazu Yoneda, and Michiko Inoue. "A Scan-Based On-Line Aging Monitoring Scheme." Journal of Semiconductor Technology and Science 14 (2014): 124-130.

- ^Keane, John P., et al. "Process and reliability sensors for nanoscale cmos." IEEE Design & Test of Computers 29.5 (2012): 8-17.

- ^Li, Xiaodong, et al. "Online estimation of architectural vulnerability factor for soft errors." Computer Architecture, 2008. ISCA'08. 35th International Symposium on. IEEE, 2008.

END

知乎:https://zhuanlan.zhihu.com/p/112259956

推荐阅读

更多内容请关注其实我是老莫的网络书场专栏