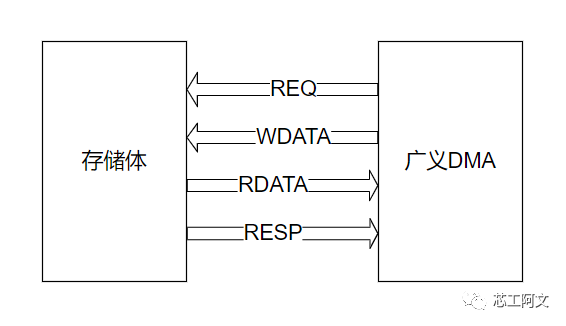

前文将所有数字芯片的硬件模块都近似等效为DMA,包括CPU。在此基础之上,继续天马行空,我觉得芯片设计中的SoC体系结构,可以简单的划分为三部分,分别是广义DMA,存储体和连接通道,如下所示。

首先说DMA。在这里,我自己造了一个概念,就是这个广义DMA。一般来说,DMA就是处理数据搬运的硬件逻辑,可以卸载CPU负载、协调源端和目的端之间的差异等等,仅仅是数据搬运工。前文我将更多的功能特性加入到了DMA,也就是我想说的广义DMA。所谓广义DMA,在使能之后从指定地址读取描述符,执行描述符的内容,再将执行结果放入指定位置。该描述符内容不仅仅是数据搬运,还包括输出的计算处理;指定位置也可以用于保存描述符,也就是说DMA在执行过程中,还可以更新描述符内容。由此看来,很多模块均可归类至广义DMA,包括CPU核、AI/GPU核、硬件加速器等等,有一定的逻辑运算和数据处理能力,但不具有长久保持数据的模块,需要作为Master的角色到存储体获取描述符和数据。

然后是存储体,这个比较简单,也就是数据生成或消耗功能的模块,作为Slave,响应来自其余模块的读写请求。数据生成,也就是接收其余模块的读请求,数据消耗,对应为写请求。在此定义下,Memory、IO接口、配置寄存器等等,均属于存储体,比如网络接口,将数据写出去,打包后发送,对应于数据消耗,显示接口,将数据驱动到显示部件,也属于数据消耗,键盘等输入设备,对应数据生成,需要被读取。

另外就是两者之间的连接通道,在极简模式下,包括请求通道REQ、写数据通道WDATA、读数据通道RDATA和响应通道RESP。

以上就是极简的系统结构模型。基于该模型,做一些简单的思考,我觉得很多系统是可以匹配的,甚至是鲲鹏Server芯片,AI/GPU等系统芯片,或者是小小的MCU芯片。只是使用场景不同,带宽/延时差异,问题着重点也是不一样的,需要创造更多的模块去缓解甚至解决,会有不同速率的Memory,更大容量的Memory,不同计算场景的DMA或者相同的DMA实现很多份,或者是同一个模块需要同时实现存储体和DMA,等等。

把CPU近似为DMA,已经在前文有描述,这里可以再讲讲PCIe的角色。在RC系统内,PCIe呈现的就是一段地址区间,可以被CPU进行读写,在枚举阶段将该空间分配至EP设备的Bar空间。理想情况下,只要通过访问Bar空间给一个初始条件,EP设备就可以无限运行,通过读写操作访问系统内的存储体。这个其实就满足了上文描述的广义DMA模型。再有一个场景,如果这个Bar空间可以被其余DMA访问,比如CPU,比如另外一个PCIe Port发出来的读写请求,那么这个PCIe Port又对应为存储体场景,这里其实描述的就是PCIe Peer-to-Peer场景。不仅仅是PCIe,其余很多模块都兼具存储体和DMA的两个角色,而且这个才是常态。

个人感觉基于该极简模型,可以帮助理解系统结构,并逐步深入去了解系统内部的各种实现细节。

最后再给自己提几个问题,基于该模型进行深入思考。如何实现高效的连接通道,解决性能、延时、阻塞、死锁和活锁?如何组织管理存储体?存在多个DMA时,如何确保数据准确,处理其竞争关系?DMA和存储器若路径过远,导致大延时,又该如何处理?是否需要将DMA划分为三六九等,各有所长,各取所需?

作者:芯工阿文

原文链接:芯工阿文

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。