编者按

“软硬件融合”图书是相关技术详解,会不定期更新。“软硬件融合”公众号关注行业热点,撰写对技术、行业发展的一些看法。“软硬件融合”技术交流群聚集了软硬件领域的大佬和相关领域的投资人。相互学习,相互帮助,共同发展。

“软硬件融合”幻灯片是整个知识体系的精炼,字斟句酌,全程干货密集。差不多一个季度更新一版,在分享、交流、碰撞中不断地调整、优化、迭代。即将跟大家见面的是第六个版本。

文章末尾有幻灯片PDF版本的下载地址。

0《软硬件融合》的写作背景

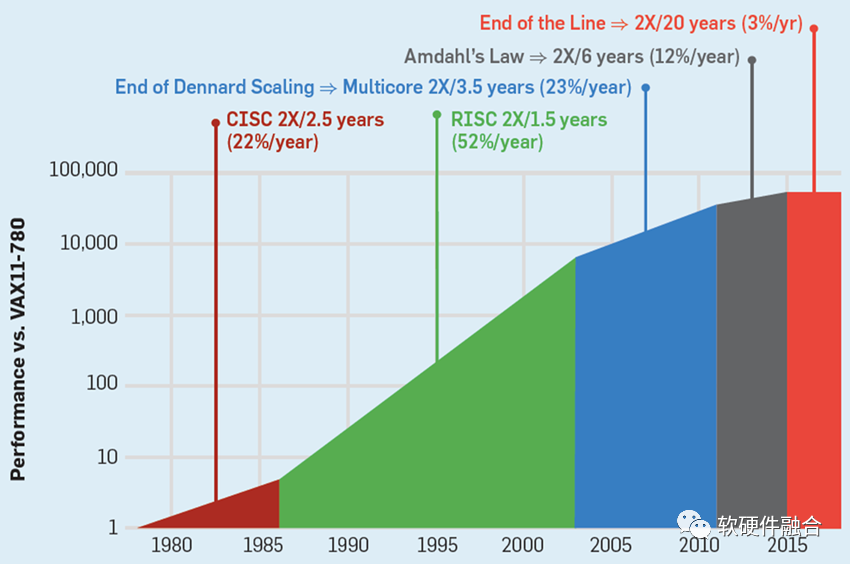

软件热点层出不穷,并且快速迭代;CPU性能瓶颈,摩尔定律失效;图灵奖获得者J&D给出的解决方案是特定领域架构DSA。

软件业务“硬件加速”,如网络、存储、虚拟化、安全、数据库、视频图像、深度学习等场景的加速,目前是各自为战的“孤岛”。

云计算等“宏”场景,是多种复杂场景的叠加。挑战在于如何把这么多场景优化融汇到一套平台化方案里。并且,既满足性能加速的要求,又满足灵活性的要求。

提出了全新的设计理念和方法——软硬件融合,期望实现软件灵活性和硬件高效性的统一。

1(挑战)云计算等复杂计算场景挑战

1.1 云计算IaaS层核心服务

和边缘计算、自动驾驶(终端)等相比,云计算系统复杂度最高,对性能、灵活性以及底层软硬件的各种要求也最高。

云计算是由IaaS、PaaS以及SaaS等组成的分层服务体系,计算、存储和网络是IaaS层核心的三类服务:

- 计算类服务。各类云主机,类型有:通用型、计算优化型、内存优化型、存储优化型、网络优化型、异构加速(GPU/FPGA/DSA/etc.)型等。涉及技术:异构加速、网络VPC/EFA等、本地/远程存储、虚拟化、安全等。

- 网络类服务。类型:虚拟网络VPC、业务负载均衡等。涉及技术:网络控制面/数据面编程,高性能网络优化,高速网络接口等。

- 存储类服务。本地块存储、远程块存储、对象存储、归档存储等。涉及技术:热/温/冷存储服务器,动态映射,NVMe/RDMA等,压缩/加密/冗余等。

1.2 云计算的特点

- 超大的规模。AWS拥有超过400万台服务器,分布在全球22个地理区域和69个可用区。

- 大量的数据。到2025年,全球数据量超过175ZB,复合增长率27%,云端数据存储占比超过50%。

- 复杂的网络。关键是带宽和延迟,还要关注域间隔离和跨域访问,以及访问控制、快速网络变更等。

- 虚拟化和多租户。主机/容器等虚拟化,是云计算的基础,用于资源隔离。多租户共享资源,提高资源利用率,降低成本。

- 安全问题。网络安全、数据安全、可信根及“零信任”、可信计算等。

- 弹性和可扩展性。横向扩展,资源数量的增减;纵向扩展,资源容量或性能的升降。

- 复杂系统解构。微服务/云原生,更多东西向流量。复杂系统不断解构,与多租户、多系统共存。

- 可迁移性和硬件接口一致性。运行实体和硬件环境解耦:虚拟化屏蔽硬件差异,VM等在不同服务器迁移。硬件接口直通VM等,不同供应商硬件接口一致性。

- 特定场景服务。通过CPU、内存、存储、网络和弹性加速的组合,扩展出特定资源优化的实例类型。

1.3 底层硬件架构挑战

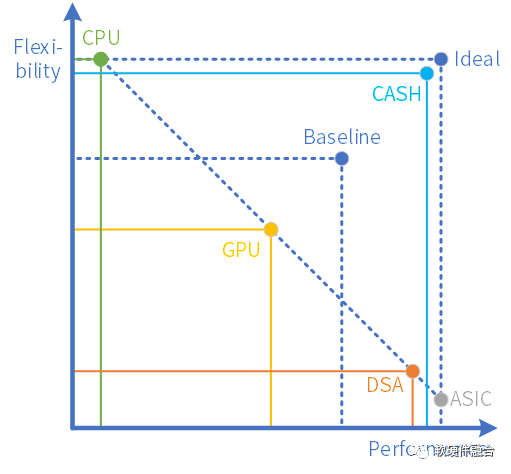

- 性能和灵活性兼顾。CPU灵活,但性能较差;ASIC性能很好,但灵活性差。性能和灵活性,要均衡,更要兼顾。

- 业务异构加速。可加速部分的占比,CPU和加速器交互成本,系统复杂度,加速效率,更多场景覆盖,开发门槛等。

- 工作任务卸载。数据、控制平面,局部卸载or整体卸载。现有系统兼容,“用户无感”,不同任务/系统间的交互。

- 业务和基础设施分离。业务和基础设施相互干扰,基础设施资源占比越来越大;基础设施工作任务整体卸载。

- 接口的弹性。接口既要虚拟化,又要标准化,还要多种设备类型共存,更高的要求是接口的高可扩展性和可编程性。

- 硬件引擎的虚拟化和个性化。类似于CPU多线程,硬件引擎需要支持多线程处理,每个线程有自己的现场、处理程序等。

- 硬件的可编程性和功能扩展。CPU性能不够,ASIC处理固定,需要实现ASIC级别的可编程性。如何快速方便的、高性能的功能扩展。

- 支持软件的差异化和迭代。芯片NRE费用高,设计周期2年,生命周期4年。如何覆盖不同客户软件的差异性和长期快速迭代。

- 硬件高可用。高可用是复杂场景的关键要求,硬件级别实现稳定性和冗余设计等。

最大的挑战:一个平台应对上述所有挑战。

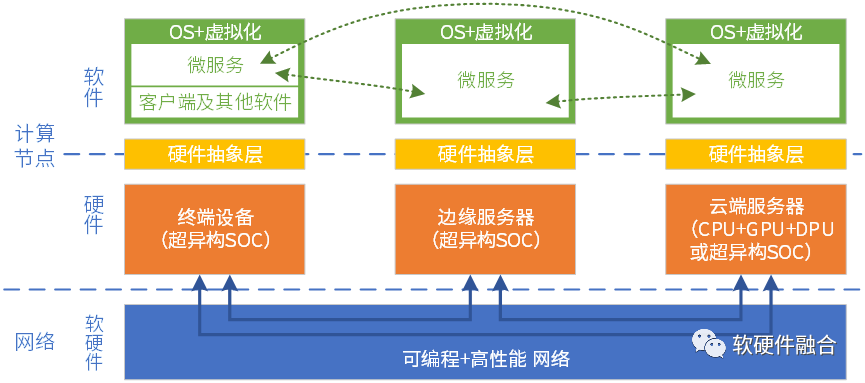

1.4 云网边端融合的挑战

云计算、边缘计算、终端以及网络,算力需求不断提高,系统复杂度不断提高,对硬件的灵活可编程性要求也越来越高。

微服务可运行在云端、边缘端,甚至终端本地,需要云数据中心内部,以及跨云边端的硬件平台一致性。

需要芯片、系统、框架和库、以及上层应用的多方协同。

2(理论)软硬件融合综述

2.1 软硬件融合的背景

软件应用层出不穷,并且快速迭代。两年一个热点,已有热点技术仍在快速演进。(同领域)不同用户业务的差异化,以及业务的长期快速迭代。

硬件越来越复杂,门槛越来越高。2D工艺->3D堆叠->4D Chiplet互联,芯片规模越来越大。芯片越来越复杂,越来越难以驾驭,一次性成本及研发风险越来越高。

CPU性能瓶颈。但单台服务器承载的工作负载数量和单个负载的算力消耗仍在增加,需要硬件加速。

ASIC/DSA灵活性不够。难以满足复杂场景的多样和变化,也使得芯片无法大规模落地。

软硬件之间的鸿沟越来越大。CPU软件性能低下,定制ASIC难以大规模复制。软件迭代越来越快,硬件迭代却越来越慢。芯片高投入高风险,制约着软件的发展。

2.2 软件和硬件的定义

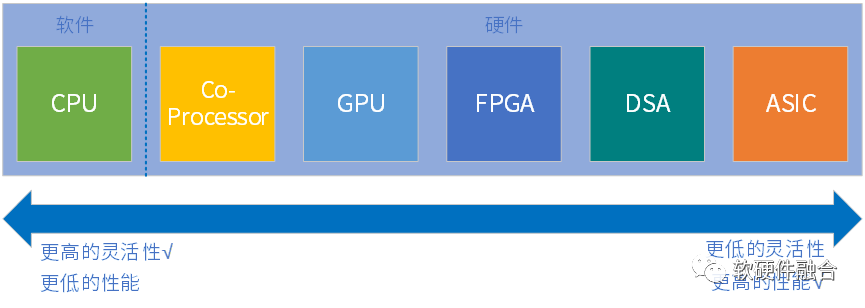

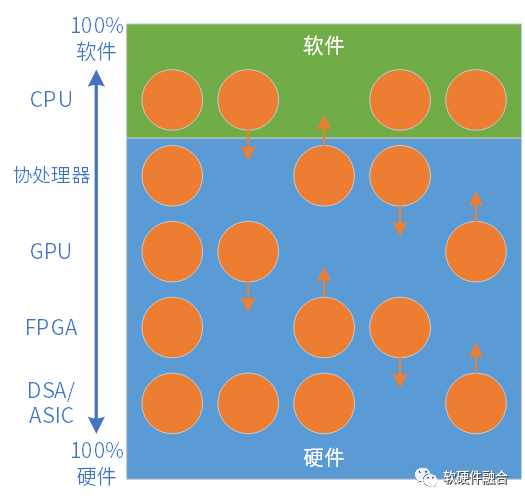

指令是软件和硬件的媒介,指令的复杂度(单位计算密度)决定了系统的软硬件解耦程度。

按照指令的复杂度,典型的处理器平台大致分为CPU、协处理器、GPU、FPGA、DSA、ASIC。

从左往右,单位计算越来越复杂,性能越来越好,而灵活性越来越低。

任务在CPU运行,则定义为软件运行;任务在协处理器、GPU、FPGA、DSA或ASIC运行,则定义为硬件加速运行。

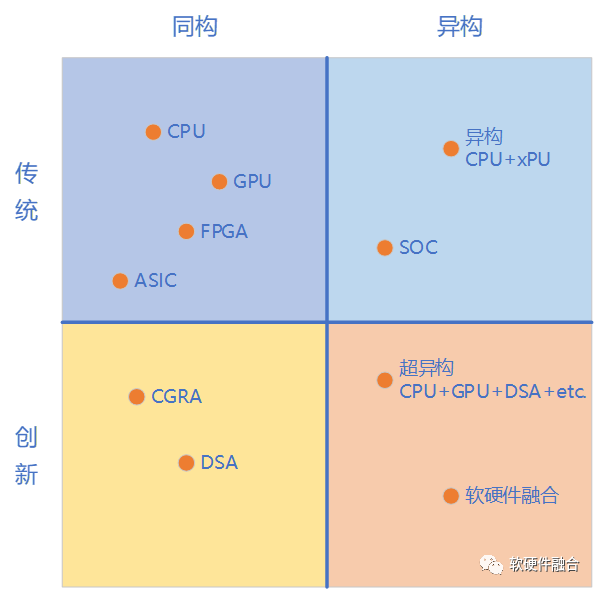

2.3 软硬件在不断融合

各类处理器都在不断拓展自身的边界:.

- CPU集成协处理器,不断扩展硬件加速指令集。例如Intel Xeon支持AVX和AMX。

- GPU集成CUDA核,还集成DSA性质的Tensor核。

- FPGA集成CPU以及ASIC,例如Xilinx Zynq SOC。

- ASIC不断回调,变成部分可编程的DSA。

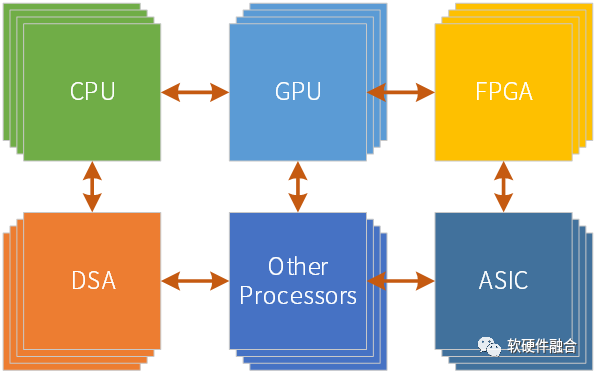

异构/超异构计算成为发展趋势:

- 既要性能不断提升,还要保持灵活可编程性。

- 单类型引擎同构,优劣势共存;异构/超异构计算,分工协作,优势互补。

- 数据中心异构/超异构越来越多,如GPU、DPU等。

2.4 软硬件融合

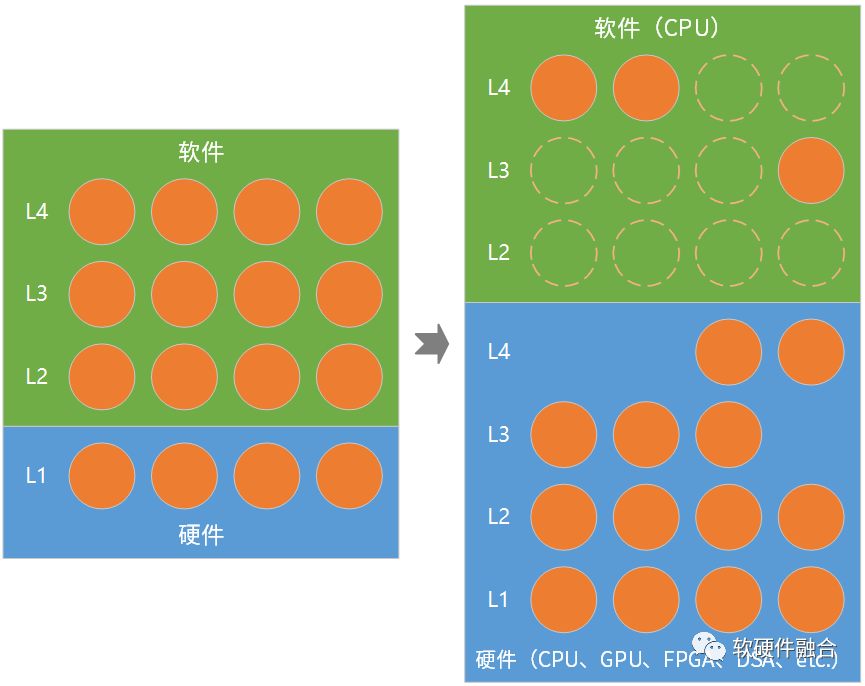

复杂系统,由分层分块的各个组件,即工作任务(Workloads),有机组成。

把工作任务映射到处理引擎:

- 坐标:假设CPU是100%软件,ASIC是100%硬件。其他处理引擎介于两者之间,是不同比例软硬件混合态。

- 均衡:根据任务特点,映射到最合适的处理引擎。注意:基于软硬件引擎的分层跟系统分层两者不一定相同。

- 动态:任务最合适的处理引擎,并非一成不变,而是随着系统发展有可能下沉(Offload)/上浮(Onload)。

软硬件融合不改变系统层次结构和组件交互关系,但打破传统软硬件的界限,系统的、动态的重构软硬件划分/协同,达到新的整体最优。

传统分层很清晰,下层硬件上层软件。软硬件融合的分层分块,每个任务模块都是不同程度软硬件解耦基础上的再协同。

整个系统呈现出:软件中有硬件,硬件中有软件,软硬件融合成一体。

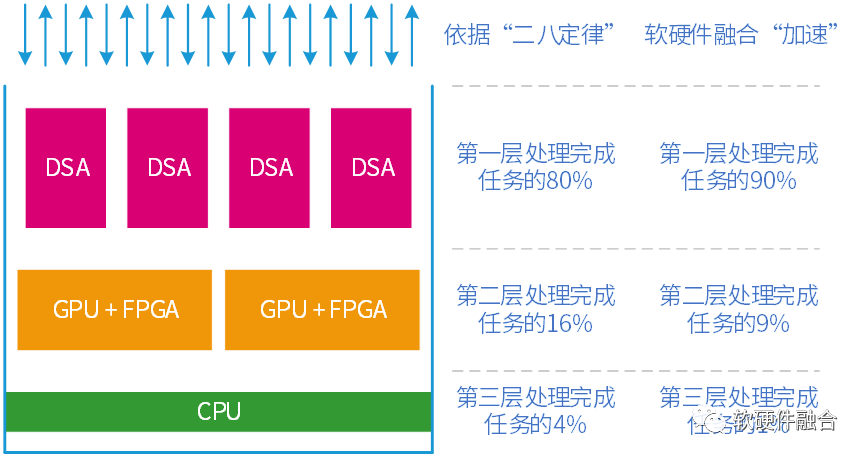

①复杂分层的系统、②CPU性能瓶颈、③超大规模以及④特定场景服务,使得:软硬件融合当前主要是系统不断卸载。

无规模,不卸载(Offload)。哪些任务适合卸载?①性能敏感,占据较多CPU资源;②广泛部署,运行于众多服务器。

宏观的看,分层的系统,越上层越灵活软件成分越多,越下层越固定硬件成分越多。

庞大的规模以及特定场景服务,使得云计算底层工作任务逐渐稳定并且逐步卸载到硬件(被动趋势)。

软硬件融合架构,使得“硬件”更加灵活,功能也更加强大,使得更多的层次功能向“硬件”加速卸载(主动抢占)。

软硬件融合总结:

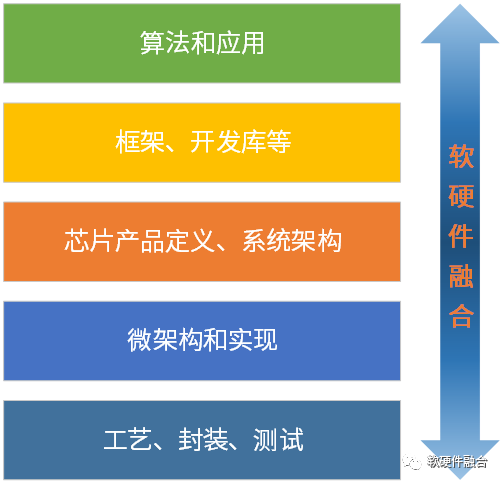

- 软硬件融合承上启下,从芯片产品定义和系统架构开始,逐步拓展到整个开发栈。

- CPU + 协处理器+ GPU + FPGA + DSA + ASIC等多种处理引擎协同的超异构混合计算;

- 每个工作任务都是在软硬件均衡/解耦基础上的再协同;

- 连接(软件之间的连接、软硬件的连接、硬件之间的连接)和调用的极致性能和灵活性;

- 兼顾软件灵活性和硬件高性能,既要又要。

软硬件融合的意义:

- 软硬件融合,既是理论和理念,也是方法和解决方案;

- 让硬件灵活、弹性、可扩展,弥补硬件和软件之间的鸿沟;

- 应对云计算、人工智能及自动驾驶等复杂场景的挑战;

- 解决芯片一次性成本过高导致的设计风险;

- 等等。

2.5 软硬件融合设计方法学

- 个体和系统。众多个体的集合,会涌现出超越个体特征的某些更高级的特征。

- 内涵和外延。系统的边界在哪里?既要考虑系统内涵的业务场景,还要考虑系统的外延约束。

- 简单和复杂。给用户的产品有多简单,背后所隐藏的技术细节就有多复杂。

- 开放和封闭。开放和封闭,是不同的商业模式。行业未来,封闭还是开放?

- 快与慢。天下武功,唯快不破;重剑无锋,大巧若工。快和慢时刻相伴。

- 通用和专用。通用CPU唾手可得,简单灵活,但性能较低。定制的专用加速器,开发门槛高,但性能更好。

- 集中和分布。云端集中,终端分布,边缘端介于两者之间。该集中还是分布?

- 量变到质变。超大规模的服务器数量,其许多特征需求,跟单体系统需求,非常的不同。

- 软件和硬件。软件定义硬件强调系统而忽略个体;软硬件融合更好的协调系统和个体的关系。

2.6 软硬件融合的应用领域

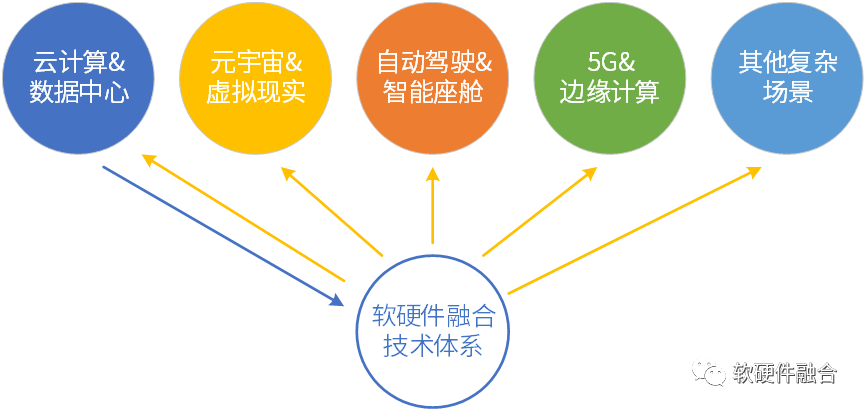

软硬件融合,从微观和宏观的视角,本质上解决(相比目前,复杂度数量级提升的)复杂计算的问题。

系统越复杂,软硬件融合的价值越凸显:

- 云计算规模庞大,算力要求最高,系统最复杂。最先遇到各种挑战,最需要软硬件融合。

- 面向未来:系统越来越复杂,算力需求越来越高。复杂计算场景,超异构计算,算力需求再上多个数量级。

- 软硬件融合相关技术,从云计算抽象出来,指引包括云计算在内的各种复杂计算场景的芯片及系统设计。

3(技术)软硬件融合技术基础

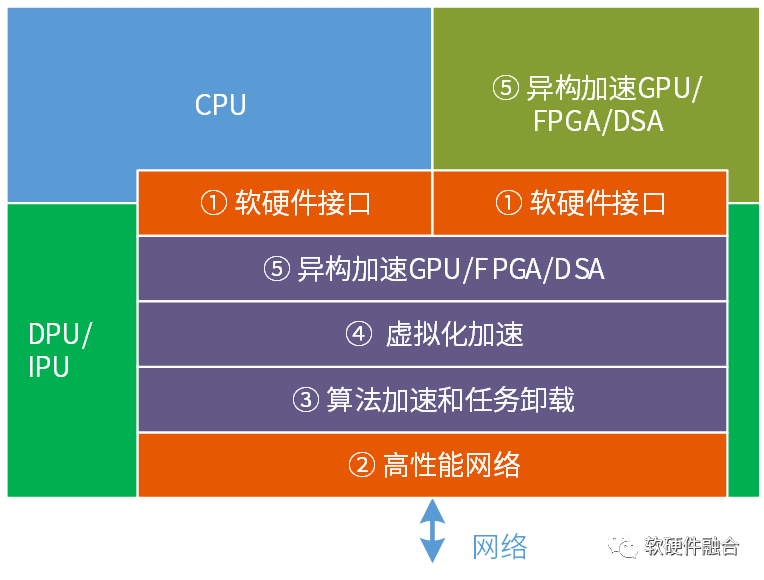

软硬件融合技术主要包括:

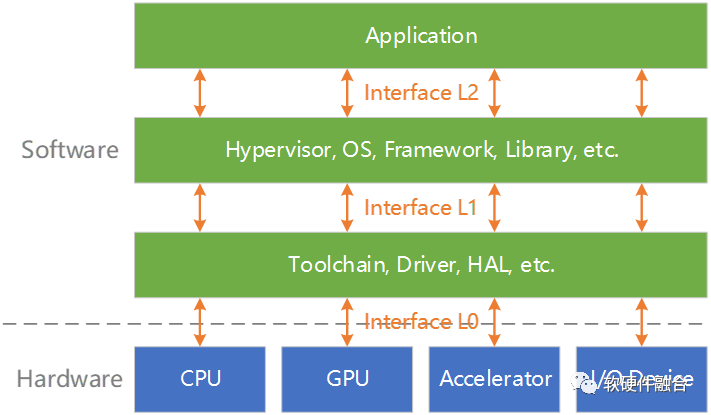

- 软硬件接口,软件和硬件高效的数据交互;

- 高性能网络,例如RDMA和拥塞控制;

- 算法加速和任务卸载,算法硬件实现以及任务卸载框架;

- 虚拟化的硬件加速,虚拟化处理的高性能实现;

- 异构计算加速平台,独立/集成的GPU/FPGA/DSA异构加速平台。

3.1 软硬件接口

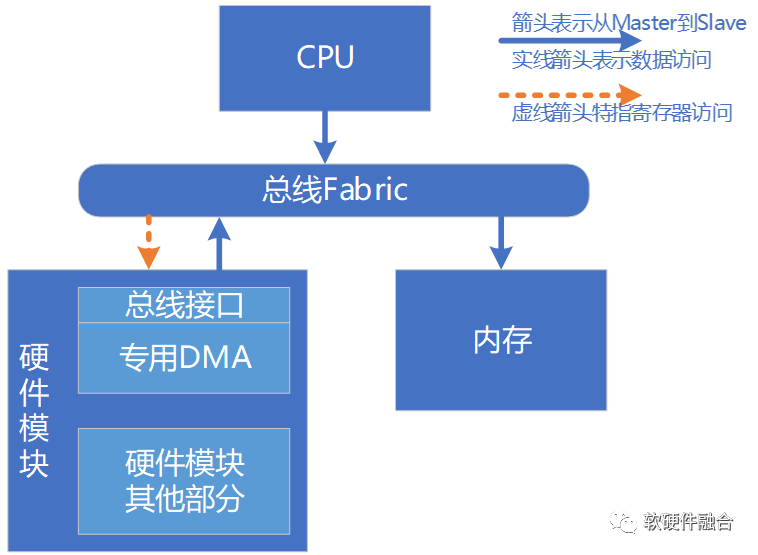

软硬件接口定义:CPU软件和其他硬件组件之间数据通信的接口,既包括数据面交互,也包括控制面交互。

可以是IO设备接口,可以是加速器接口;更广义的,也可以是封装的高层次服务接口。

基于生产者消费者模型,驱动和设备。

组成部分:软件驱动、设备的硬件接口子模块、共享队列以及传输的总线。

软硬件接口演进:

- 软件轮询硬件寄存器

- 硬件中断

- 硬件DMA

- 共享队列

- 用户态软件轮询

- 多队列并行

3.2 网络高性能

云计算系统持续解构,东西向网络流量越来越多,占比越来越大;服务器堆栈延迟的问题凸显。主要措施:

- 网络容量升级:例如,网络带宽升级,把整个网络从25Gbps升级到100Gbps;例如,更多的网络端口。

- 轻量协议栈:数据中心网络跟互联网不在一个层级,物理距离短,堆栈延迟敏感,不需要复杂的用于全球物理互联的TCP/IP协议栈;

- 网络协议硬件加速处理;

- 高性能软硬件交互:高效交互协议+ PMD + PF/VF/MQ等,如AWS EFA;

- 高性能网络优化:多路负载均衡、乱序交付、拥塞控制等,实现低延迟、高可靠性(低性能抖动)、高网络利用率,如AWS SRD。

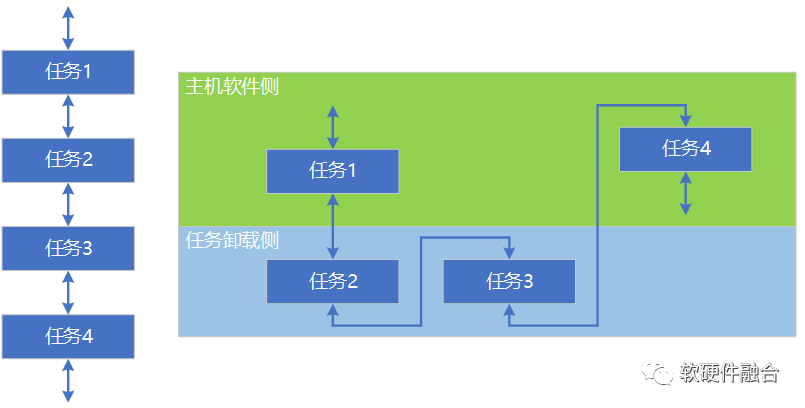

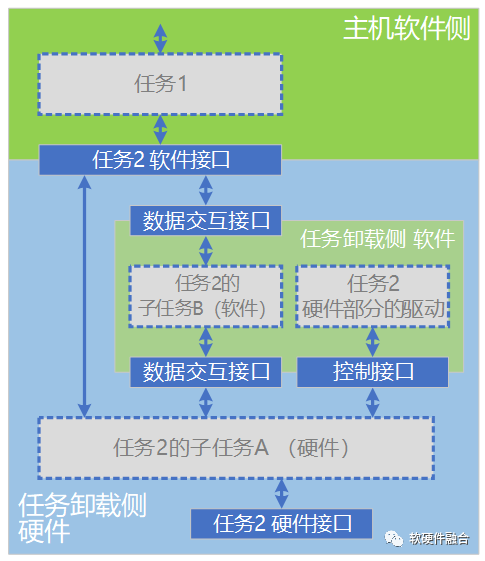

3.3 算法加速和任务卸载

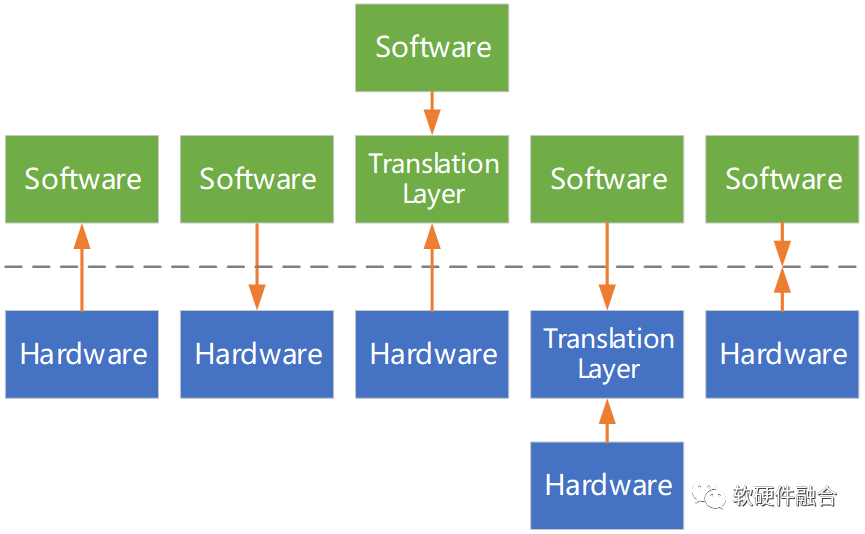

任务卸载:主机软件任务卸载到独立硬件;任务卸载以算法“加速器”为核。任务卸载原则:原有调用关系不变。

软件调用软件转换成软件调用硬件、硬件调用软件或硬件调用硬件。

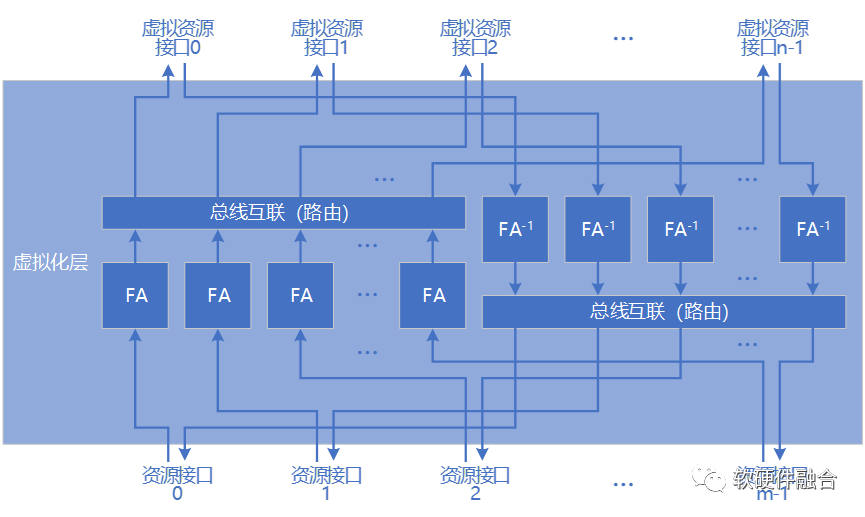

3.4 虚拟化的硬件加速

抽象是对原有对象的封装,虚拟化是抽象后的复制;虚拟资源通过时间、空间的分割以及抽象模拟共享物理资源。

例如,网络虚拟化是虚拟地址到物理地址的映射,存储虚拟化是虚拟块/盘到物理块/盘的映射。

虚拟化模型:

- 数学模型:y=FV(x)

- 通过接口呈现虚拟化特性

虚拟化的硬件处理:

- 流水线:指令流驱动vs 数据流驱动

- 映射机制:映射算法vs 映射表

- 缓存机制:主动vs 被动

3.5 异构计算加速

云计算异构加速主要用于业务应用:

- 权衡1:既要保证加速的性能,还要考虑加速的弹性。

- 权衡2:独立或集成。

云计算中的异构计算主要包括:

- 基于GPU的异构加速。GPGPU+CUDA,GPU异构加速本质是众多并行的高效能通用处理器,CUDA编程友好性。

- 基于FPGA的异构加速。FPGA的硬件弹性跟云非常契合,加速框架Shell/引擎Kernel,运行时RT,开发Stack等。

- 基于DSA的异构加速。DSA是从ASIC回调,相比ASIC具有一定通用性,可以覆盖较多的场景。

4(案例)DPU,云计算软硬件融合的核心承载

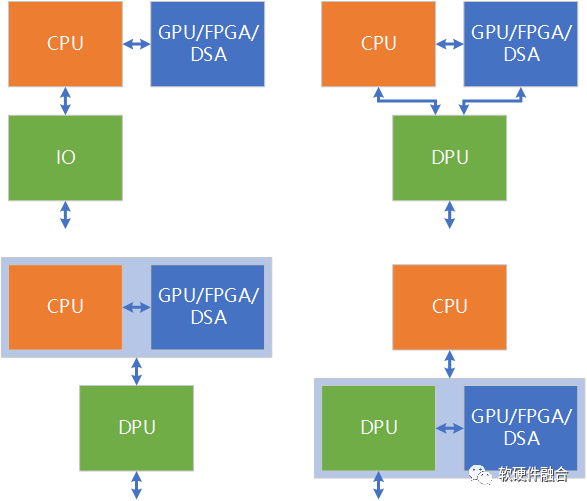

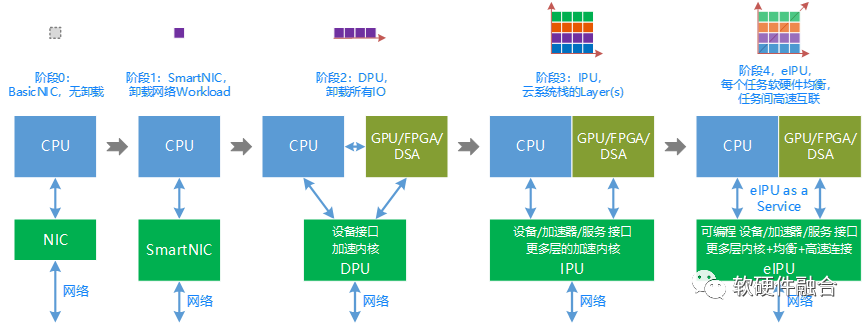

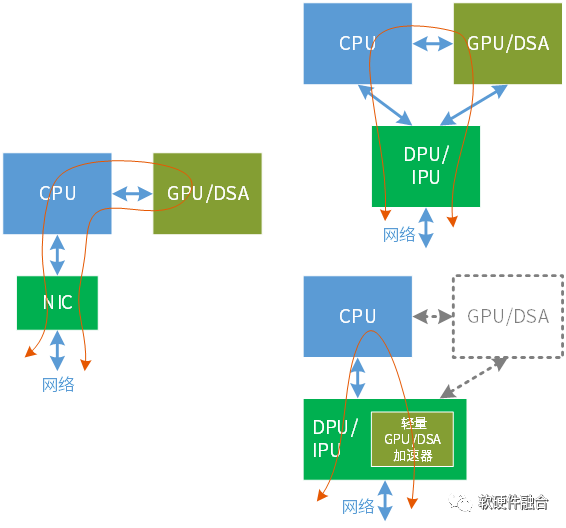

4.1 CPU卸载视角:DPU是集成加速平台

需要有独立的加速平台,不断的把工作任务从CPU软件卸载,并硬件加速。

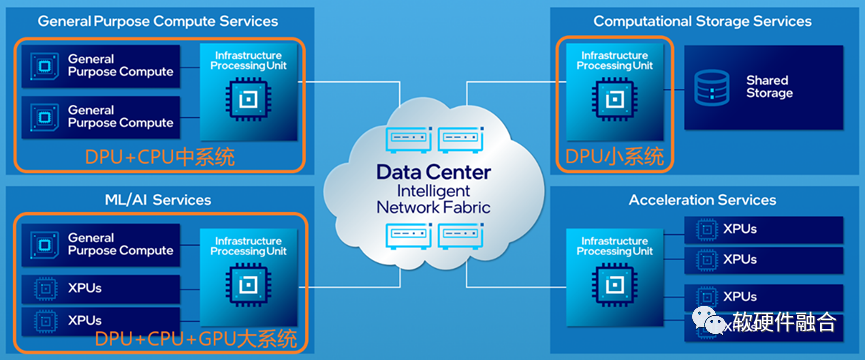

DPU/IPU用于基础设施层的通用任务加速,GPU/FPGA/DSA用于应用层的弹性业务加速。

NVIDIA 2020年5月发布DPU,10月份大张旗鼓宣传;作者2020年8月份提出四阶段论;Intel 2021年6月份发布IPU。

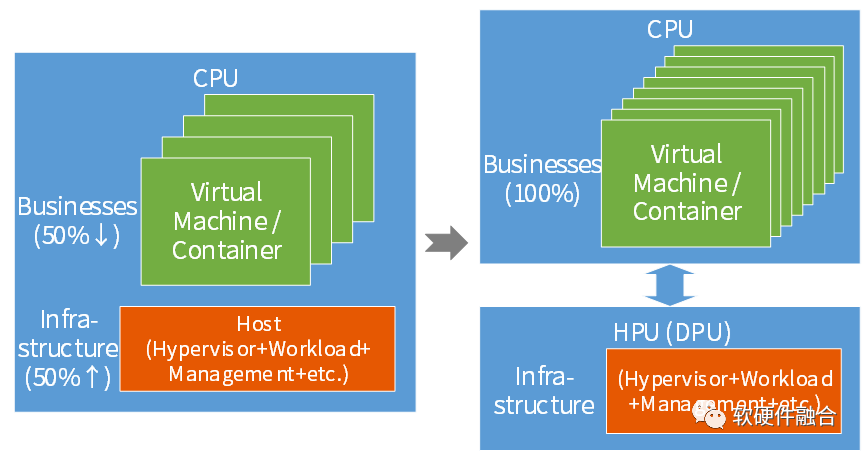

4.2 业务基础设施分离,释放AI强劲动力

CPU资源完全交付;传统客户方便上云;主机侧独立安全域;物理机+虚拟机优势合并;统一公有云和私有云运维。

CPU性能瓶颈,I/O带宽持续增大,I/O成为系统瓶颈。

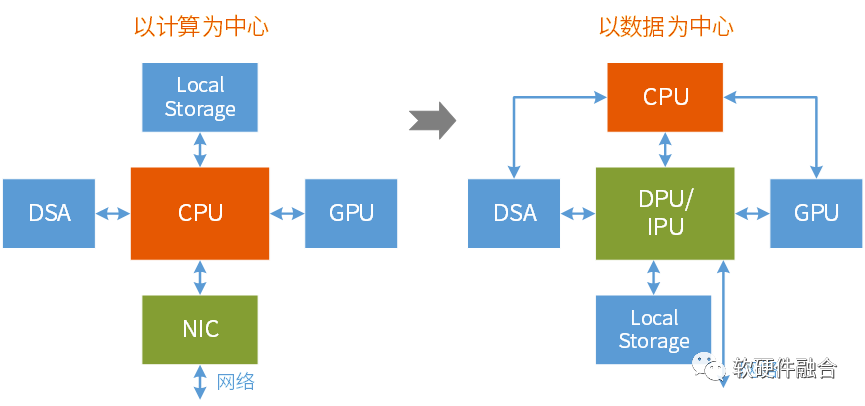

4.3 以数据为中心

大数据、AI等场景呈现“高数据量低计算量”的特点,云计算复杂系统解构,进一步增强了这一特点。

以计算为中心,指令控制流驱动计算;以数据为中心,数据流驱动计算。注意:DPU本身要完成大量工作任务处理。

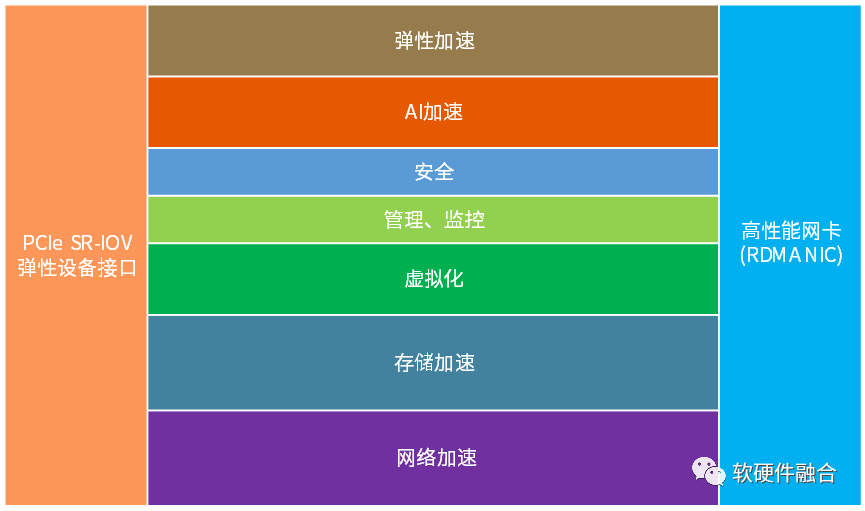

4.4 DPU/IPU的常见功能

DPU基本功能:支持网络、存储、虚拟化和安全的加速处理,融入IaaS服务,支持业务VM/容器,缺一不可。

4.5 AWS Nitro系统

AWS Nitro系统包括:VPC加速卡、EBS加速卡、本地存储加速卡、Nitro控制器、安全芯片以及Lite Hypervisor。

第一代Nitro是一个ARM CPU(Graviton?),后续几代逐步加入各类可编程加速引擎,成为DPU SOC。

4.6 Intel Mount Evans IPU

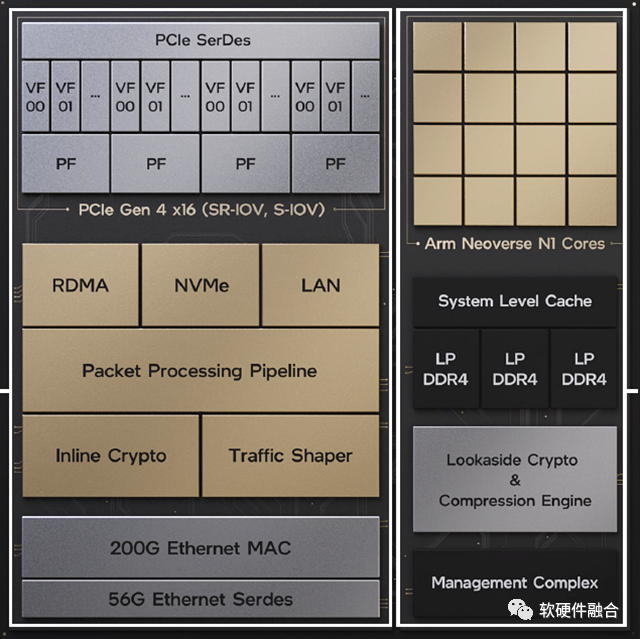

Intel IPU,具有一定通用特征的“DPU”。现在特征:16核ARM N1,P4可编程网络包处理DSA,RDMA/RoCEv2。

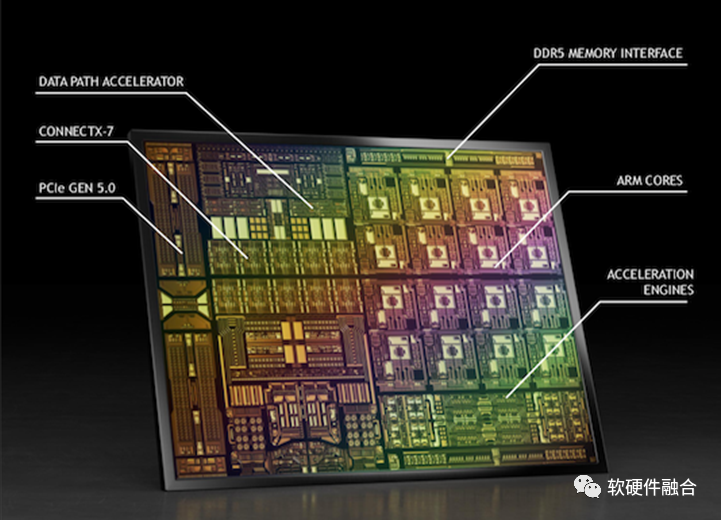

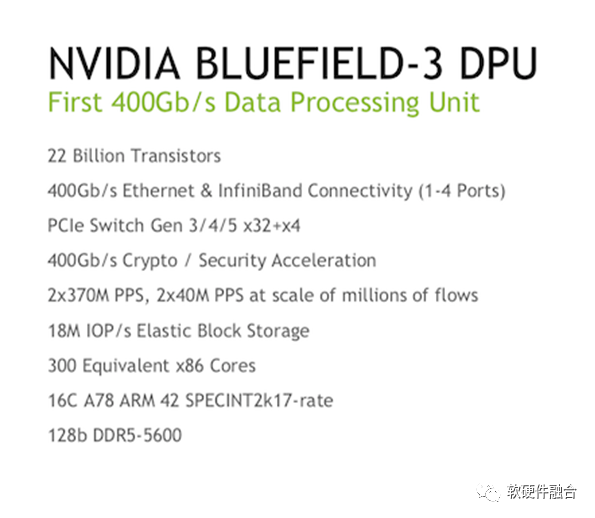

4.7 NVIDIA Bluefield-3 DPU

优势:硬件的网络虚拟化,RDMA高性能网卡,安全类Feature;

待改进:非标准接口,功能扩展性和差异化,网络数据面可编程。

5(架构)基于软硬件融合的超异构计算

5.1 DPU是云计算的核心

CPU、GPU和DPU,既相互协作,又相互竞争。

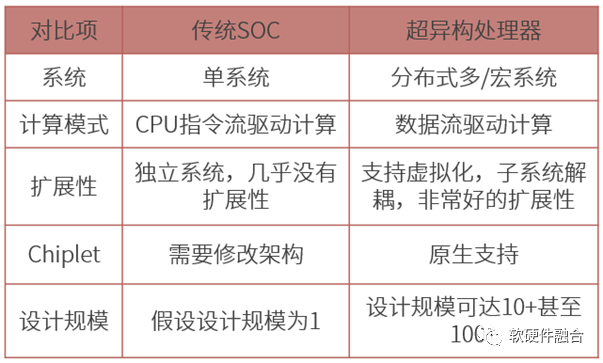

传统观点,DPU是CPU的任务卸载加速。软硬件融合观点:DPU成为云计算的核心,独立CPU/GPU是DPU的扩展。

5.2 DPU是超异构计算的起点

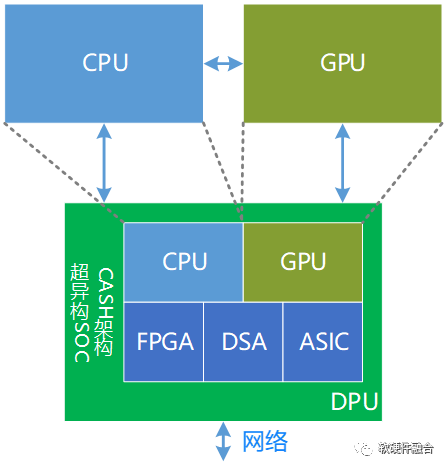

DPU包含嵌入式CPU/GPU,随着工艺和封装的进步,DPU演进成更大规模的超异构计算芯片。

DPU是超异构的起点(4阶段):

- Level 01,DPU是CPU的任务卸载/加速。CPU性能瓶颈。把网络、存储、虚拟化及安全等任务从CPU卸载到DPU加速,减轻CPU的压力。

- Level 02,IPU是基础设施,支撑上层应用。IPU成为集成加速平台,既完成基础设施层工作任务处理,也完成部分业务应用的加速,支撑CPU和GPU的应用层工作。

- Level 03,DPU/IPU是计算的核心。IaaS甚至PaaS、SaaS等云计算核心服务,融入到DPU软硬件。DPU图灵完备,并且是数据的入口。这使得DPU成为核心,而CPU和GPU成为扩展。

- Level 04,DPU/IPU的本质是超异构计算。算力持续提升,数据中心的超异构计算,DPU是核心承载。基于超异构的复杂计算,需要在极致灵活性的基础上,提供极致的性能。

5.3 如何提升宏观算力

性能和算力的概念是一致的:性能,代表了微观个体的计算能力;算力,代表宏观众多个体计算能力的总和。

实际总算力= 单位处理器性能x处理器数量x 利用率;

单位处理器性能= 指令复杂度x 频率x 并行度。

挑战:提升性能会降低灵活性,没有灵活性芯片就无法大规模(即处理器数量)。

如何提升宏观算力:

- 指令的复杂度。通过DSA架构创新,以及异构/超异构计算,融合多种类型引擎协作完成计算。

- 提高运行频率。优化设计,选择最优的流水线级数以及工艺进步。

- 提高并行度。集成更多的处理引擎。

- 优化I/O和处理的匹配度。通过架构、工艺和封装优化I/O。

- 实现芯片的更大规模落地。均衡芯片的性能和灵活可编程能力,实现宏观总算力最大化。

- 优化宏观算力的利用率。通过云计算、边缘计算、MSP、分布式云、云网融合等手段,提升算力利用率,降低算力成本。

5.4 算力平台的优劣势分析

5.5 算力革命:基于软硬件融合的超异构计算

CASH,Converged Architecture of Software and Hardware,软硬件融合架构。

只考虑芯片,难以实现通用灵活性;只考虑软件,难以构建超大规模芯片架构。

唯有软硬件融合,才能实现既要又要。

5.6 通用超异构处理器

为什么要通用?

- 定制芯片覆盖场景小,生命周期短,难以大规模落地。

- 大芯片NRE费用不断增加,需要足够“通用”灵活可编程,才能大规模落地,才能摊薄单芯片成本。

- 基于通用的“定制”,多层次“可编程”能力。

6(生态)构建软硬件融合的开放生态

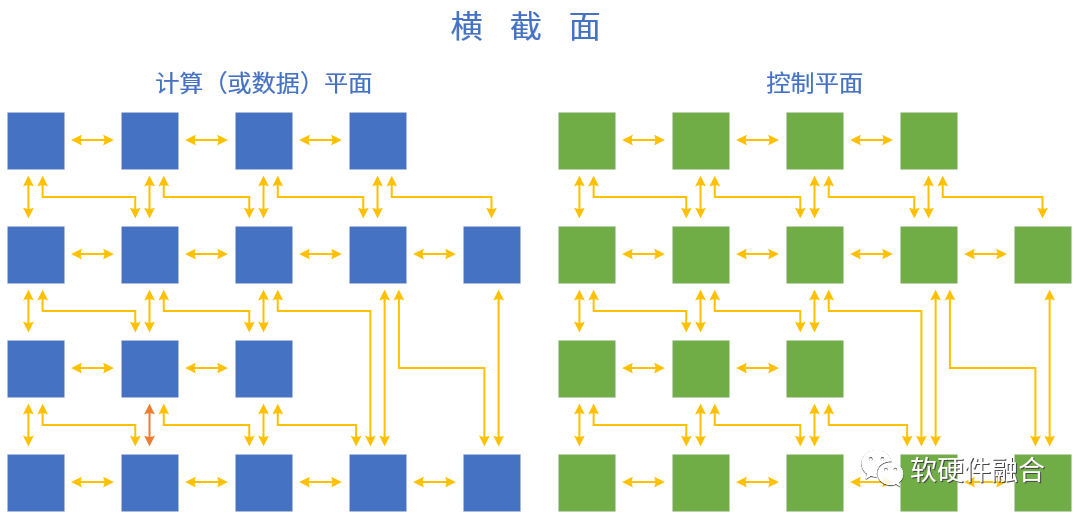

6.1 计算平面和数据平面

基于软硬件融合的超异构计算:计算(或数据)平面由CPU、GPU、DSA等各类处理引擎组成,控制平面运行在CPU。

6.2 泛义的软硬件接口

泛义的接口:

- 块和块之间、层和层之间的接口;

- 软件和软件之间、硬件和硬件之间、软硬件之间的接口。

软件和硬件之间的接口:

- 硬件定义接口,软件适配;

- 软件定义接口,硬件适配;

- 硬件/软件定义接口,软件接口适配层;

- 硬件/软件定义接口,接口适配层卸载;

- 软件硬件设计遵循标准接口(标准、高效、开源、迭代)。

6.3 处理器引擎的金字塔和倒金字塔分层结构

世间万物由基本粒子组成,复杂处理由基本计算组成。指令复杂度越高,处理器架构形态就越多,覆盖的场景就越小。

6个主要的处理器引擎类型:

- CPU,基础指令构成,只有CPU一个子类型。最好的灵活可编程性,可以用在任何领域,但性能相对最低。

- Co-processor,基于CPU的扩展指令集的运行引擎,如Intel的AVX、AMX。

- GPU,小处理器众核并行,NP、GraphcoreIPU等都在这一层级。较好的软件编程能力,覆盖领域和场景较多,但性能居中无法极致。

- FPGA,硬件可编程,需要通过逻辑或软件编程。

- DSA,具有一定程度上的可编程,覆盖的领域和场景比ASIC要大,但仍需要很多面向不同领域的DSA。

- ASIC,理论上最复杂的“指令”,单个ASIC覆盖的场景非常小,因此存在数量众多的各类ASIC引擎。

6.4 构建软硬件融合的开放生态

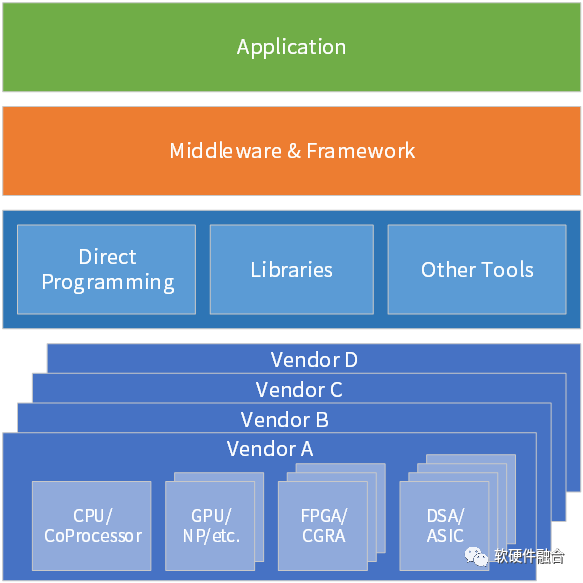

计算的任务,跨越不同类型处理器引擎,跨越不同厂家芯片,跨越云边端:

- 从CPU到ASIC,越来越多的不同领域/场景的处理引擎。即使同领域/场景,不同厂家的实现架构也会不同。

- 领域/场景越来越碎片化,构建生态越来越困难。需要从硬件定义软件,逐步转向软件定义硬件(符合“软件定义一切”大趋势)。

- 软件原生支持硬件加速。软件设计控制平面和计算平面分离,把计算平面下沉到硬件。软件定义一切,硬件加速一切。

- 当异构处理器的引擎架构越来越多,(不同厂家)芯片数量越来越多,所处的环境(云网边端)也越来越多,需要构建高效的、标准的、开放的生态体系。

6.5 软硬件融合.乌托邦

超异构计算架构:

- CPU+GPU+FPGA+DSA等多种架构处理引擎组成的超异构混合计算;

- 实现既要又要:接近CPU的灵活性,接近ASIC的性能。

平台化&可编程:

- 两个一切:软件定义一切,硬件加速一切;

- 两个完全:完全可软件编程的硬件加速平台,完全由软件编程决定业务逻辑;

- 一个通用:能够满足多场景、多用户的需求,能够满足业务的长期演进。

标准&开放:

- 接口标准、开放,持续演进;

- 拥抱开源生态;

- 融入云原生;

- 用户无(硬件、框架等)平台依赖。

(正文完)

来源:软硬件融合

微信公众号:

相关文章推荐

更多软硬件技术干货请关注软硬件融合专栏。