转发自公众号“FPGA加速器”,欢迎关注。软件定义智能网卡采用bump-in-the-wire协同计算方式,如何支撑应用开发和加速成为关键。根据软件定义智能网卡设计目标,从网络和应用两种任务处理特点出发,单一的流水线很难覆盖多维目标。软硬件协同的异构计算方式在宏观上指明了计算实现路线,能否应用于智能网卡微观设计。

FIA组成

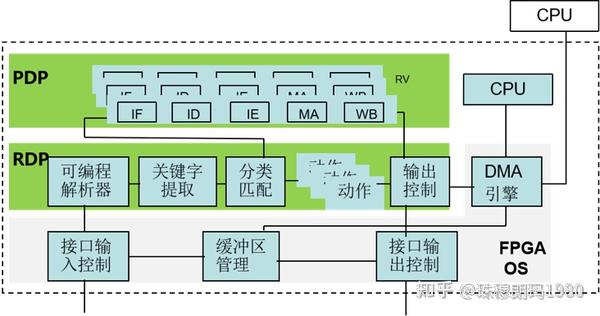

回归计算机Mainframe发展初期的IO处理机,技术螺旋式发展思路,高山设计了FPGA在线加速的智能网卡架构FIA。FIA主要包括面向分组处理的可重构分组处理流水线RDP(Reconfigurable Datagram Pipeline),面向数据处理加速的可编程深度处理引擎PDP(Programmable Data Processor),可编程硬件FPGA逻辑抽象FPGA OS,以及控制器CPU。

(1)FPGA OS

FPGA逻辑资源抽象FPGA OS提供了基本的网卡分组处理功能,如网络接口输入输出控制、网络分组缓冲区管理、服务器质量保障,以及DMA等。FPGA OS为其他功能的实现,提供了框架,并保证了FIA的移植性。

(2)RDP(Reconfigurable Datagram Pipeline)

可重构分组处理流水线RDP主要根据FPGA OS提供的分组的metadata信息,解析报文头,提取分组关键字、关键字查表,执行动作等。RDP是智能网卡中分组处理的基本流水线,采用模块化设计,可以灵活插入其他网络功能,如校验、重组、加解密等等。RDP的实现可以采用通用的分组处理流水线,也可以采用PISA架构的RMT流水线。

(3)PDP(Programmable Data Processor)

可编程深度处理引擎PDP主要根据RDP分类结果,对需要深度处理的报文数据进行再次加工处理。PDP是智能网卡中报文内容深度处理的处理引擎,采用定制的处理器核实现,比如开源的RISC-V处理器核等。基于PDP,也可以实现加解密,协议处理等功能。

PDP和RDP是一种软硬件协同的异构分组处理架构,协议和内容的处理可以在PDP和RDP之间进行灵活的划分。PDP和RDP之间采用数据队列和消息通信接口,避免了通用CPU中Memory Cache架构,支持数据的直接访问处理,减小了数据处理延迟。

(4)控制CPU

采用COST CPU,可以运行操作系统,一方面,对FPGA资源片、功能库等进行管理,另一方面,可以作为部分应用卸载的平台,比如Openflow控制器代理等。

PDP是裸CPU核,支持程序直接运行,而控制CPU运行操作系统,支持程序移植。

FIA结构

(1)独立直连队列结构

在FIA架构下,通常配置部署多个PDP核,RDP处理完成后,根据分类结果,将报文头(或者报文体)分派到与PDP关联的队列中,实现大规模PDP并行处理,实现性能的提升。

(2)环形级联栈结构

在服务功能链的驱动下,PDP另种处理模型是串行流水处理。在这种架构,第一阶PDP从RDP接收报文,处理完成后,再发送到下一阶PDP中进行处理,实现分组的流水处理,实现功能扩展。

独立直连队列结构和环形级联栈结构,可以组合使用。另外,之所以没有采用Network on Chip结构,是因为在64个PDP核的结构下,暂时不需要复杂的NoC互连结构。

FIA特点

(1)在线inline加速的高效性

FIA采用FPGA在线处理的加速框架,在分组传输过程中,实现对分组、协议,甚至是内容的深度处理,避免了数据流在不同加速器之间的读写和调度,减小了处理延迟。

(2)软硬件可编程programming的灵活性

FIA中RDP和PDP均采用可编程的实现方式,如RMT和RISC-V,极大增强了智能网卡功能的扩展性。另一方面,定制的RMT和RISC-V实现,保证了分组的处理性能。

(3)近数据near-data的低延迟

FIA中RDP直接将报文数据送到PDP,如RISC-V,进行处理,避免了普通网卡与CPU之间系统总线的传输延迟,以及CPU层次化cache延迟。

小结

软件定义可重构智能FIA主要是从FPGA资源抽象的角度出发,提出了基于RMT的面向分组处理的FPGA硬件资源抽象,以及基于RISC-V的面向数据处理的FPGA硬件资源抽象,充分发挥了可重构PISA和可编程CPU架构的编程和性能优点,为网络功能卸载和用户应用加速开发提供了开放平台。

软件定义智能网卡采用on-path加速模式,可以对在网计算INC、机器学习RNN等进行加速。

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/361232562更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。