一、边沿检测

边沿检测,就是检测输入信号,或者FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测。在检测到所需要的边沿后产生一个高电平的脉冲。这在FPGA电路设计中相当的广泛。

没有复位的情况下,正常的工作流程如下:

(1)D触发器经过时钟clk的触发,输出trigger信号,保存了t0时刻的信号。

(2)同时由trigger通过非门输出信号,保留了当前时刻t1的触发信号

(3)经过与门输出信号pos_edge,neg_edge

- a) 只有t0时刻为高,且t1时候为低的时候,与门输出高,此时为下降沿。

- b) 只有to时候为低,且t1时候为高的时候,与门输出高,此时为上升沿。

当然,在复位的时刻,DFF被复位,无法检测触发信号。

二、边沿检测电路的实现方法;

1、always @ (posedge signal)

不便于处理此类触发信号,除非外部输入信号作为全局时钟使用。另外众所周知由于电路不能能避免抖动现象,所以用这个检测方法是明显不合理的。

2、一级D触发器实现; 我们先看下代码,

module shizhong

(

input clk,

input rst\_n,

input spi\_cs,

output mcu\_write\_done

);

reg spi\_cs\_r0;

always@(posedge clk or negedge rst\_n)

begin

if(!rst\_n)

begin

spi\_cs\_r0 <= 1;

end

else

begin

spi\_cs\_r0 <= spi\_cs;

end

end

assign mcu\_write\_done = (~spi\_cs\_r0 & spi\_cs) ? 1'b1 : 1'b0; //posedge

endmodule

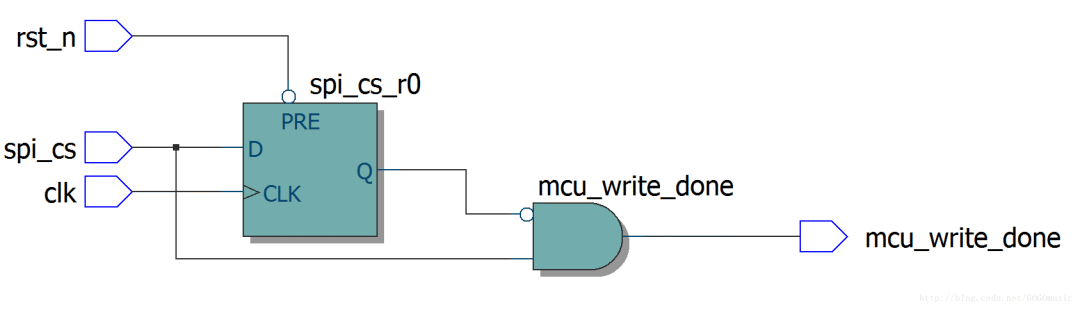

代码综合后RTL视图如下:

正常工作,没有复位的情况下,工作流程如下:

(1)D触发器经过时钟clk的触发,输出spi\_cs信号,保存了t0时刻的信号。

(2)同时由spi\_cs直接输出到与门,保留了当前时刻t1的触发信号

(3)经过与门输出信号pos\_edge,neg\_edge

a) 只有t0时刻为高,且t1时候为低的时候,与门输出高,此时为下降沿。

b) 只有to时候为低,且t1时候为高的时候,与门输出高,此时为上升沿。

一级D触发器在寄存器比较时,前一时刻通过D触发器已经统一到FPGA的时钟域,而当前时刻直接从外部输入,与FPGA整体逻辑电路不在同一时钟域,为提高系统的稳定性我们可以采用第三种方法即二级D触发器。

3、二级D触发器;我们仍然先看代码:

module shizhong

(

input clk,

input rst\_n,

input spi\_cs,

output mcu\_write\_done

);

reg spi\_cs\_r0, spi\_cs\_r1;

always@(posedge clk or negedge rst\_n)

begin

if(!rst\_n)

begin

spi\_cs\_r0 <= 1; spi\_cs\_r1 <= 1;

end

else

begin

spi\_cs\_r0 <= spi\_cs; spi\_cs\_r1 <= spi\_cs\_r0;

end

end

assign mcu\_write\_done = (~spi\_cs\_r1 & spi\_cs\_r0) ? 1'b1 : 1'b0;

endmodule

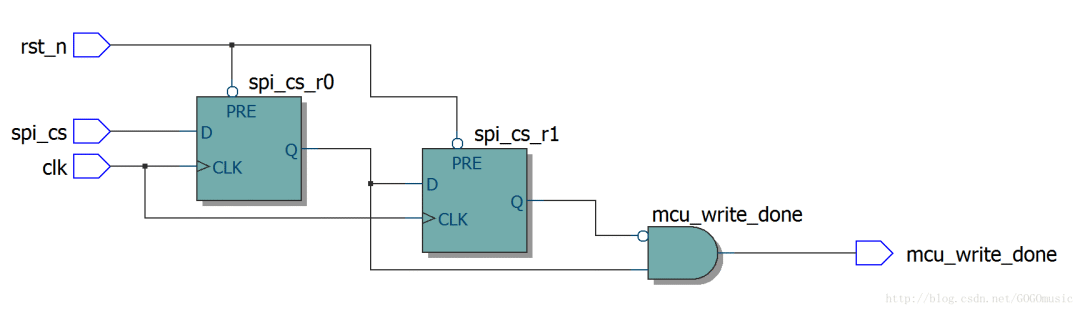

代码综合后RTL视图如下:

正常工作,没有复位的情况下,工作流程如下:

(1)一级D触发器经过时钟clk的触发,输出当前spi\_cs信号,保存了t0时刻的信号。送往与门。

(2)二级D触发器经过时钟clk的触发,输出上一时刻spi\_cs信号,保存了t1时刻的信号。通过非们送往与门。

(3)经过与门输出信号pos\_edge,neg\_edge

- a) 只有t0时刻为高,且t1时候为低的时候,与门输出高,此时为下降沿。

- b) 只有to时候为低,且t1时候为高的时候,与门输出高,此时为上升沿。

利用CLK打两拍,实现了上一时刻信号和本时刻信号和FPGA整体逻辑电路统一到同一时钟域。

这里要加两级的触发器的另一个原因,因触发器跳转产生滞后信号只能在时钟的上升沿,而被检测信号tigger并不一定是在一级触发器跳转的时钟上升沿到来,这样一级触发器所产生的滞后信号与tigger相差就达不到一个CLK周期,所以产生的脉冲信号就小于一个CLK周期了,不利于后面电路对其的应用。

边沿检测应用:

(1)将时钟边沿使能转换为边沿检测使能,使时钟同步化。

(2)捕获信号的突变(UART,SPI等信号使能突变)

(3)逻辑分析仪中信号的边沿检测。

实现指标及存在缺陷:

(1)增大CLK信号可以增强边沿检测的效率,但不能滤去跳变的杂波。

(2)减少CLK可以有效滤去跳变的杂波,但不能及时检测到边沿跳变。

(3)增加DFF能更好的滤除杂波,寄存信号,但同时检测延时大。

END

原文链接: https://mp.weixin.qq.com/s/zCFPXNziVnB_NfFmdI0uqA

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。