之前有朋友总结过SMMU的知识,感兴趣的话看看《ARM系列 -- SMMU(一)》,《ARM系列 -- SMMU(二)》。

在CPU内部,完成地址转换的部件是MMU(Memory Management Unit),基本原理是把CPU的地址空间划分成若干大小相等的空间(段式,页式,段页式),通过重新映射的方式把CPU的地址空间对应到内存的物理地址空间。这种方式,就是把CPU地址分为两个高位和低位部分,低位地址表示在同一个段/页内的地址偏移,而高位地址会被映射到不同的内存位置。MMU要做的就是维护这个地址映射。前文已经介绍过MMU,《ARM系列 -- MMU》。本篇是对前面这几篇的一个补充。

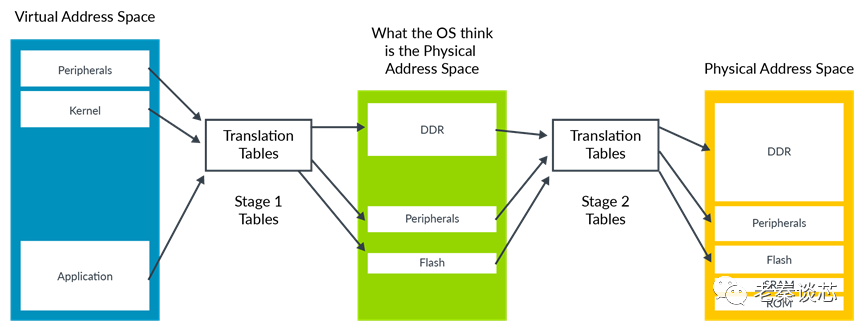

在前面讲虚拟化的时候,也提到过ARM支持两步地址转换Stage 1和Stage2。一般由操作系统控制Stage 1地址转换。之所以要分两步,目的是增加Stage 2允许hypervisor控制虚拟机(VM)的内存视图。也就是说,Stage 2允许hypervisor控制虚拟机可以访问哪些系统资源,以及这些资源在虚拟机地址空间中的位置。Stage 2转换使得虚拟机只能看到分配给它自己的资源,而看不到分配给其它虚拟机或hypervisor的资源。

SMMU是System Memory Management Unit的缩写。从名字看,SMMU是应用于除了CPU以外的系统部件的MMU,也就是维护系统部件的地址转换,起到隔离等作用。

ARM中的SMMU目前架构版本有四个版本,分别是SMMUv3.0,SMMUv3.1,SMMUv3.2,SMMUv3.3,最新的架构版本是SMMUv3.3。ARM提供的最新IP是MMU-700,支持SMMUv3.2,估计不久就会有新的IP出现了。

我们今天来捋一捋MMU-700,简单了解一下这个IP的硬件设计。依据不同的设计需要,MMU-700可以用来做:

- Stage 1地址转换,也就是把虚拟地址(Virtual Address,VA)转成中间地址(Intermediate Physical Address,IPA);

- Stage 2地址转换,把IPA转成PA;

- Stage 1和Stage 2地址转换,也就是先把VA转成IPA,再把IPA转成PA;

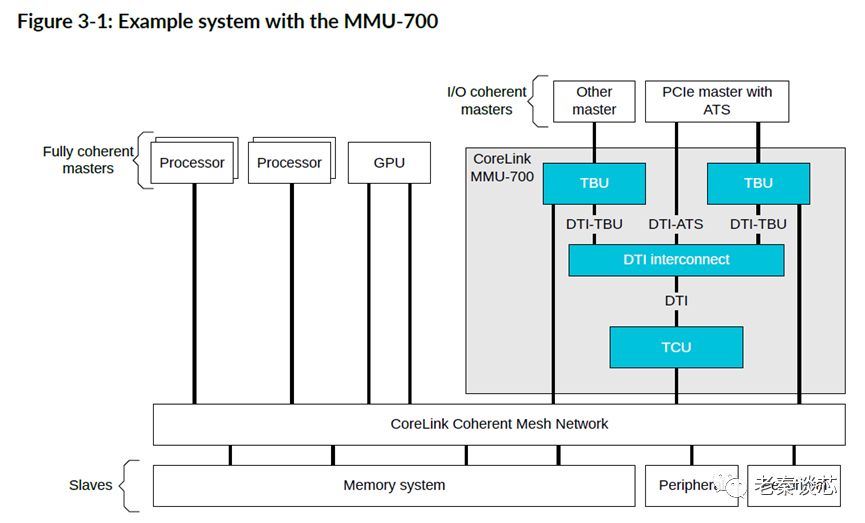

MMU-700里面的重要组件分为三种,分别是:

- TBU(Translation Buffer Unit),使用TLB缓存地址转换表;

- TCU(Translation Control Unit),控制和管理地址转换;

- DTI(Distributed Translation Interface),连接TBU与TCU;

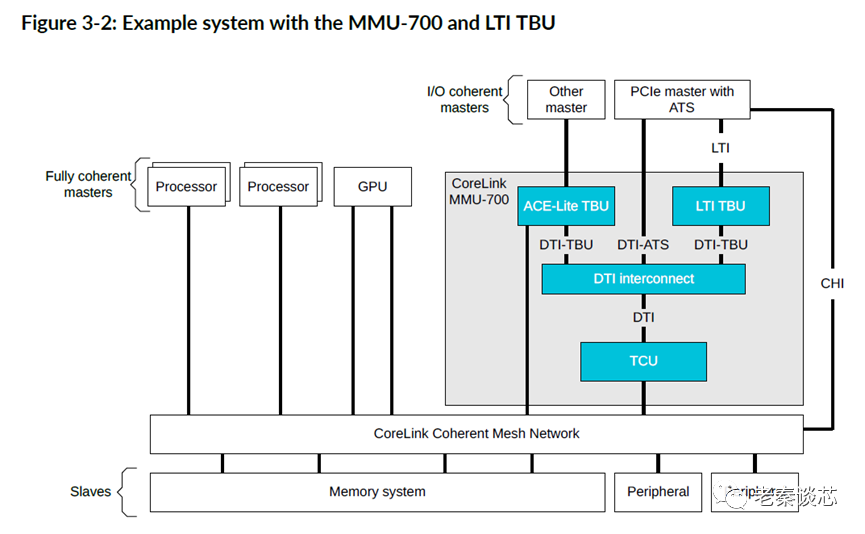

所以在一个子系统里面,可能会有多个TBU,这些TBU需要通过DTI与TCU连接。一个系统集成方案如下两个图所示:

在这两个例子中,PCIe控制器(或者其它的IO控制器)访问系统资源时,发出的地址需要经过转换才能发送到互连网络上进行下一步路由。PCIe控制器的地址先发给TBU,TBU接收到请求以后会去查询内部的TLB,如果这段地址转换在TLB中,则地址转换成功;如果不在TLB中,则TBU需要发送请求给TCU。

这两个例子的不同之处在于TBU与PCIe控制器的接口,第一个例子中,PCIe控制器通过ACE-Lite访问TBU;第二个例子中,PCIe控制器通过LTI访问TBU,PCIe控制器与系统总线还有一个CHI协议连接。MMU-700与MMU-600的一个不同之处就是,MMU-600并不支持LTI。

接下来一个一个分析这几个组件。

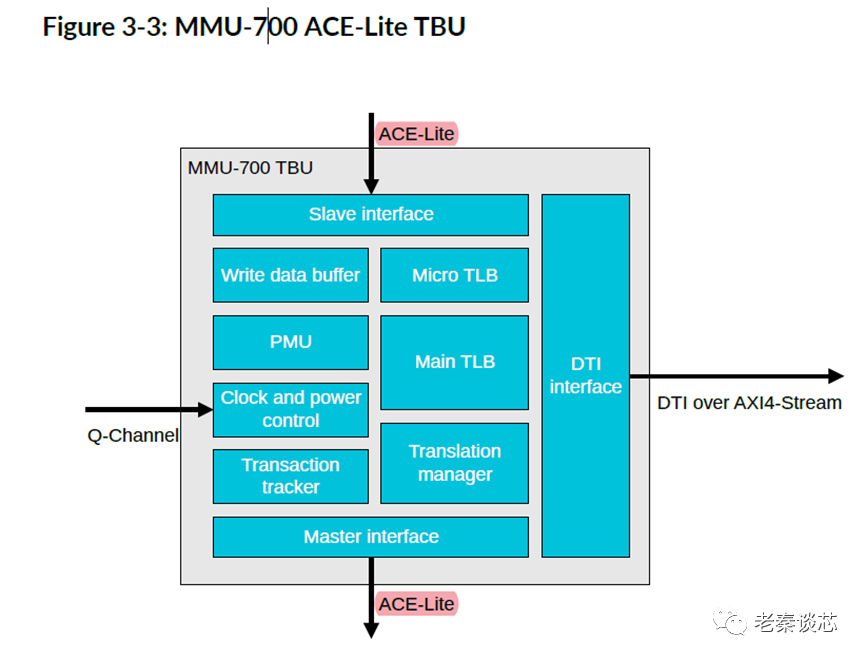

TBU

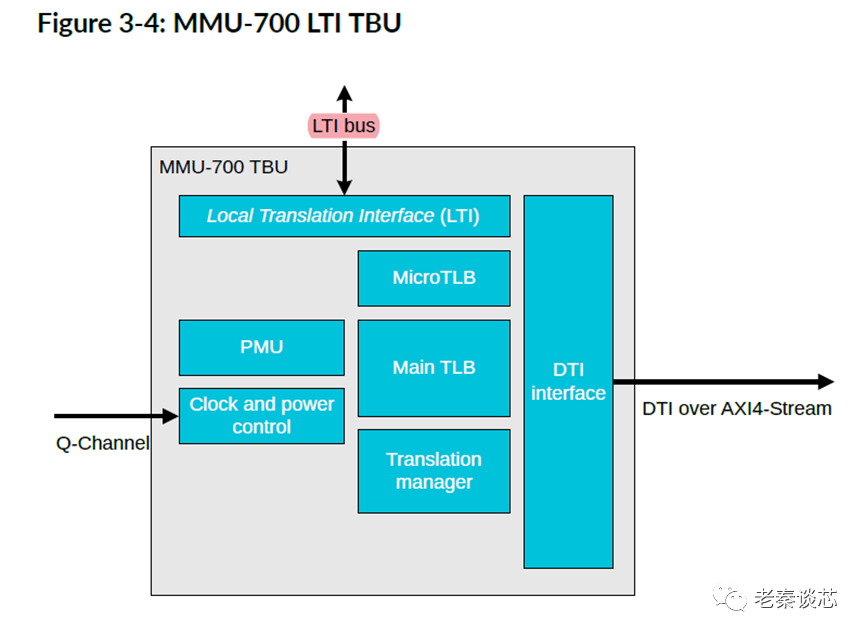

先看接口部分,TBU与IO控制器的接口可以是ACE-lite或者LTI(Local Translate Interface)中的一种,在配置MMU-700的时候可选择,这两种TBU的内部结构也稍有不同。按照这两种不同的接口,TBU也可以被称为ACE-Lite TBU和LTI TBU,看文档的时候如果看到,就知道这个TBU是哪种接口了。

TBU的接口包括以下这些:

- ACE-Lite TBS(Translation Slave),接收IO控制器的内存访问请求 - ACE-Lite TBM(Translation Master),发送内存访问请求到系统总线 - LTI,ARM有文档定义这个接口

- LPI_PD,这是一个Q-channel,如果与这个TBU相连接的IO控制器掉电了,那么这个TBU也可以掉电。之前讲Q-channel和PPU的时候提过,Q-channel只是做低功耗控制握手协议,真正控制电源开关的部分不在Q-channel或PPU里

- LPI_CG,也是一个Q-channel,用于动态时钟关断。外部的时钟控制器监测到TBU处于non-active时,可以动态关断TBU的时钟

- DTI interface,双向的AXI-Stream总线。TBU通过这个接口,使用DTI-TBU协议,向TCU请求地址转换

- 中断,如果看过中断控制器GIC的文章,这个没啥好说的了

TBU内部的模块包括:

- Master and slave接口模块,上面已经讲过了

- Micro TLB,提供从输入地址到输出地址的端到端转换

- Main TLB,缓存TLB条目

- Translation manager,管理控制地址转换请求

- PMU,记录性能相关的事件数量

- Clock and power control,控制TBU的电源和时钟

- DTI接口模块

- Transaction tracker,管理超发(outstanding)的读/写事务

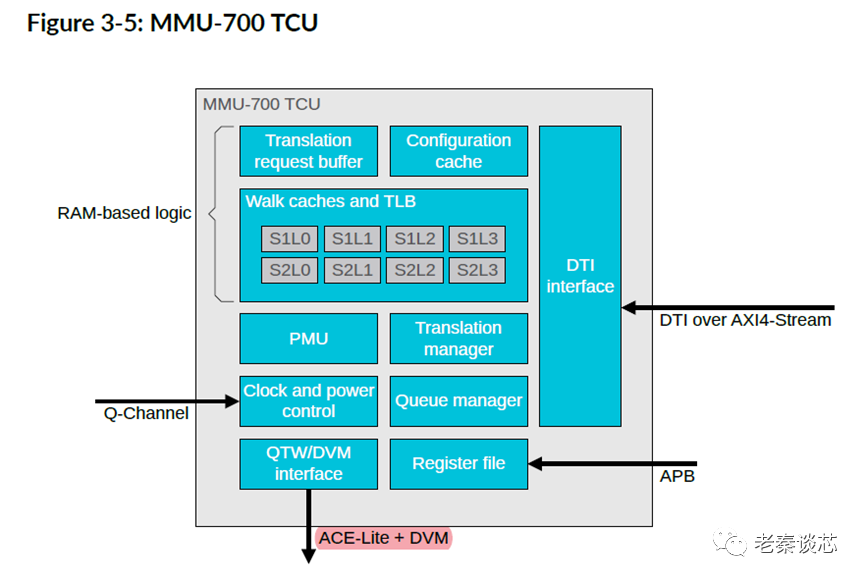

TCU

TCU的接口如下:

- QTW/DVM,这是一个ACE‑Lite+DVM的主接口

- APB4从接口,用于访问和配置TCU的内部寄存器

- LPI_PD,电源管理的Q-channel

- LPI_CG,动态时钟管理的Q-channel

- DTI interface

- MSI interface,也是AXI-strem,可以直接将消息信号中断(MSI)连接到通用中断控制器(GIC),避免系统中的复杂依赖关系

- System coherency interface

TCU内部的模块包括:

- Walk cache,可配置bank和way的组相联缓存,记录translation table walks(不知道怎么翻译了)的结果

- Configuration cache,4路组相联的缓存,用于存储配置信息

- Translation manager,管理正在进行中的地址转换请求

- Translation request buffer,当Translation manager填满时,这个buffer存储来自TBU的地址转换请求,可防止请求过多导致DTI接口被阻塞

- PMU,记录性能相关的事件数量

- Clock and power control,电源和时钟管理

- Queue manager,管理SMMU的队列

- QTW/DVM interface

- Register file,SMMU的内部寄存器

- DTI interface,与DTI相连接

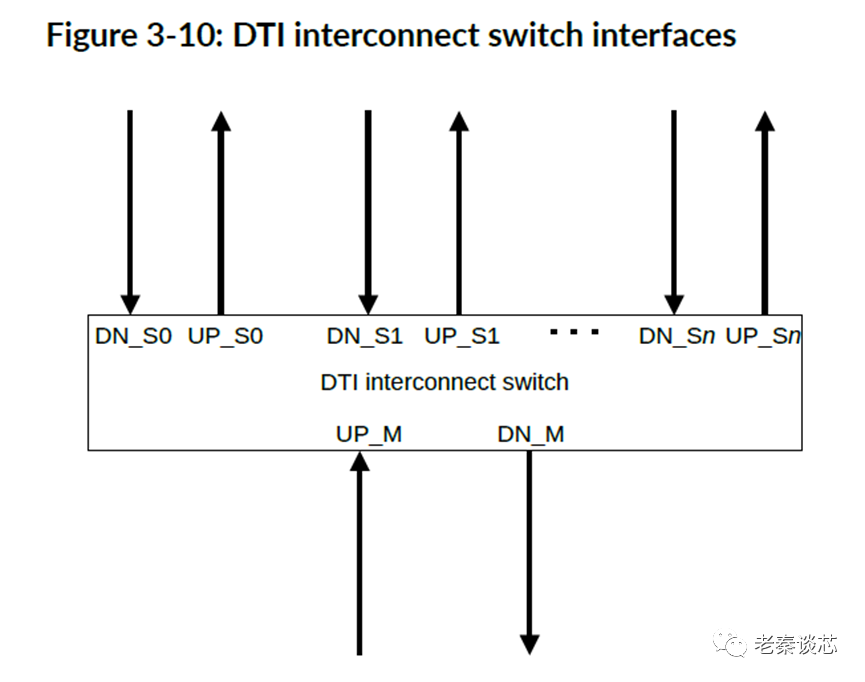

DTI

DTI相对简单一些,就是起到连接TBU和TCU的作用。因为AXI-stream本身是单方向传输的,所以要支持双向传输就需要两个AXI-stream。这在介绍GIC的时候提到过。

关于在DTI上传输的具体协议,ARM也有规定,感兴趣可以去查看DTI协议手册。这一点也和GIC比较像,不知道大家还记得GIC stream不?

为啥提了很多次GIC呢?这是因为GIC与SMMU有一定关系。SMMU主要是为了IO控制器访存时的地址转换,PCIe是系统中主要的IO(CPU中的PCIe一般都是root complex),且PCIe支持消息中断(MSI),基本原理就是设备写主机的一个特殊寄存器既可以产生中断。为了支持消息中断,GIC里面提供了一个组件,叫ITS。所以,一般在集成PCIe子系统的时候,PCIe控制器,SMMU和ITS都是必须的。

今天先到这里吧。

原文链接:老秦谈芯

作者:老秦谈芯

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。