凡事总须研究,才会明白。

-- 鲁迅

上篇我们介绍了SMMU的基本结构和用法,本篇讲一下SMMU的高级功能。在ARM64体系结构中,SMMU几乎可以放在总线互联中的任意设备MASTER前边,同样适用于PCIE ROOT complex(RC),且与RC一起实现PCIE的一些高级功能。PCIE规范中定义了 Address Translation services (ATS)。

如图,ATC 是address translation cache,其功能与TLB类似,用来缓存IOVA与PA转换的page table,上图中,PCIE device可在设计时自带此种缓存,这样在EP发起一次transaction时,可通过缓存查找相应的table entry,而不用将工作全部抛给translation agent(TA),从而提升了系统整体性能。上图中的TA的功能在ARM64体系结构中由SMMU承担,此外SMMU还要显式的负责同步TLB和与它相连的分布ATC中的数据一致性。

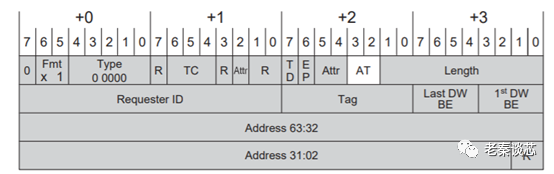

为了兼容ATS协议,TLP包包头中增加AT域来表示包内地址域是已经转换地址或未转换地址,一个带有ATC的EP或者function在产生TLP包时在ATC中查找转换地址并发出,此时不需要SMMU再次对地址进行转换,反之,如无法查到该地址,则需要SMMU进行转换后再寻址。当AT域编码为01b时,function可发出translation request包,来获取转换地址。

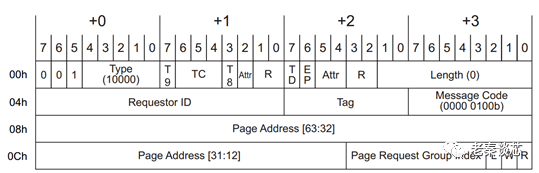

在ATS规范中,Page Request Interface Extension是一个相对独立的功能,通过Page Request Interface(PRI)可以使内存在做DMA的时候不用强制PIN在内存中,所谓PIN在内存中是指,将DMA要访问的内存数据页在使用过程中一直保持在内存中,不能换出到后备存储器,也不能迁移到其他物理页。有了PRI该问题得到了解决,在设备做DMA的过程中不需要保证物理页常驻内存,只需要遇到不在内存的时候通过增加PRI的过程换入所需的页即可。Page Request InterfaceExtension可以帮助function发出pagerequest包,包格式图如下:

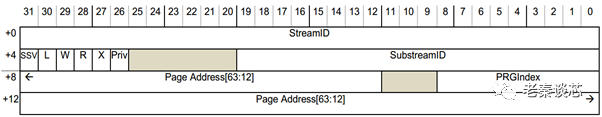

硬件上SMMU配合PCIE PRI增加PRI queue,用来接收pcie的page request包对应的请求数据,SMMU硬件将数据写入PRI queue中。

如图为PRI queue中的数据格式,StreamID对应PCIE包的requestorID,substreamID对应PCIE包的PASID,page address为function请求的页地址。以上数据会随着PCIE的PRI请求不断写入PRI queue,由CPU去逐一处理。

以上看似零散的功能在下边的应用例子中,我们能看到他们的合理性。

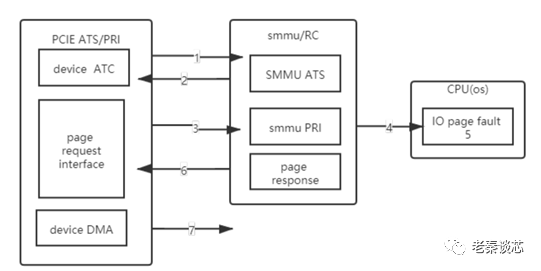

如图所示,动态过程如下:

- PCIE Device首先通过本地ATC查找某页地址的转换,未成功则通过ATS发起针对页地址的translation request

- SMMU收到RC的地址转换请求,查找本地TLB,如果没有,硬件进行page table walk,若页表不存在或者页不在内存中,则需要返回translationfault给PCIE device.

- PCIE PRI 发起page request给RC,携带streamID,substreamID,地址等信息

- SMMU获得该信息后组成数据格式包放入PRI queue ,并产生中断通知CPU(OS)

- OS 内存管理子系统将缺页补上,即处理IO Page fault handling

- SMMU(RC)通过response告知device,发送page response,页处理完成,该内存页已经准备好,可进行DMA操作

- PCIE Device发起DMA操作

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/QdBdRvYT-HyaSYfqFpU5gA

作者微信公众号

相关文章推荐

欢迎大家点赞留言,更多Arm技术文章动态请关注极术社区Arm技术专栏。