数字硬件建模SystemVerilog(四)-综合

综合编译器将实现细节添加到抽象RTL模型,合成编译器:

- 将RTL功能转换为等效功能的通用逻辑门。

- 将通用门映射到特定的ASIC或FPGA目标。

- 执行逻辑优化以满足时钟速度要求。

- 执行逻辑优化以满足面积和功率要求,

- 执行逻辑优化以满足建立和保持时间。

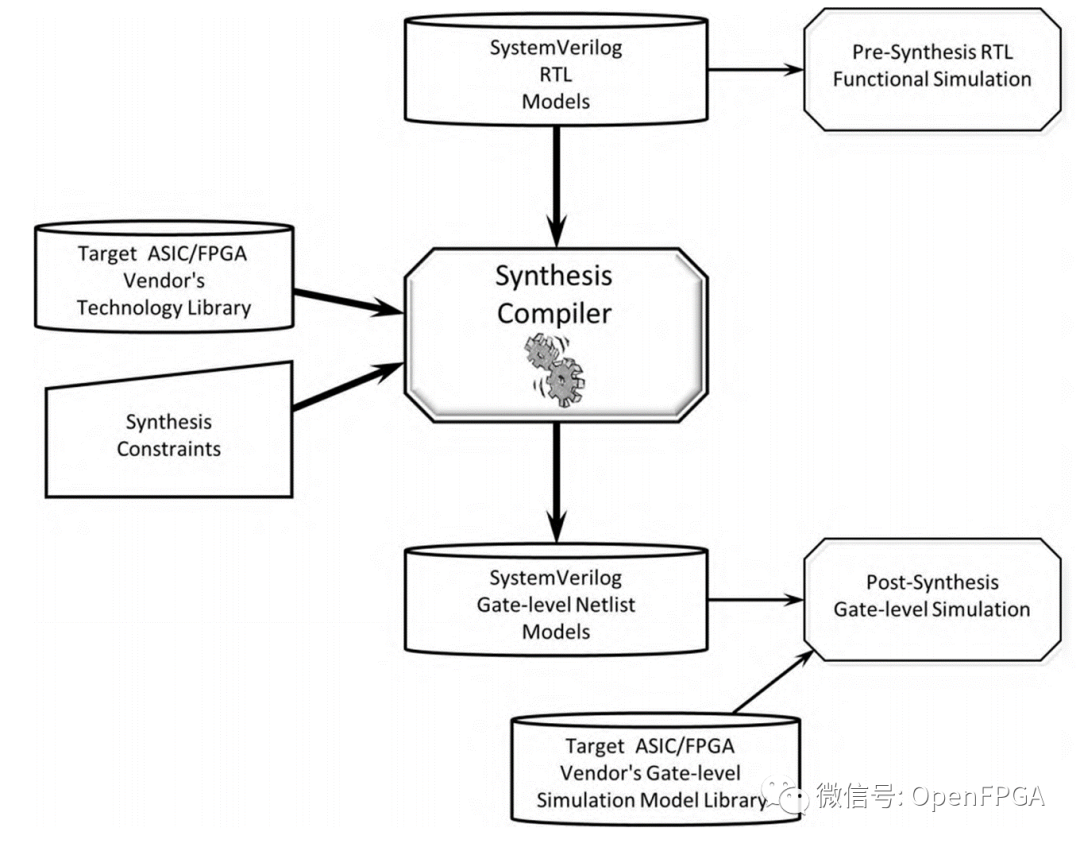

图1-10说明了使用SystemVerilog进行数字综合的一般流程,

图1-10:SystemVerilog综合工具流程

综合编译器需要三种主要类型的输入信息:

- 系统Verilog RTL模型-这些模型由设计工程师编写,代表需要在ASIC或FPGA中实现的功能行为

- 目标ASIC或FPGA的工艺库-该库由ASIC或FPGA供应商提供,包含可用于实现所需功能的标准单元(用于ASIC)或门阵列块(用于FPGA)的定义

- 综合约束定义-这些约束由设计工程师定义,并提供RTL代码中不可用的综合编译器信息,例如需要在ASIC或FPGA中实现的所需时钟速度、面积和功率目标。

出于前端设计和验证目的,综合的主要输出是门级网表。网络列表是组件和将这些组件连接在一起的导线(称为网络)的列表。网络列表中引用的组件将是用于实现所需功能的ASIC标准单元或FPGA门阵列块。此网络列表可以有多种格式,包括EDIF、VHDL、Verilog2001或SystemVerilog。本系列文章仅使用SystemVerilog输出。

为了仿真SystemVerilog网络列表,需要每个组件的仿真模型。目标ASIC或FPGA供应商将提供用SystemVerilog编写的仿真库。通常,这些库只使用SystemVerilog的Verilog-2001子集。这些组件在门级建模,具有详细的传播延迟。这些模型与设计工程师编写的抽象RTL模型不同。

SV综合编译器

有几个SystemVerilog综合编译器支持SystemVerilog语言。Cadence、Mentor Graphics和Synopsys等电子设计自动化(EDA)公司销售的商用综合编译器。一些FPGA供应商,如Xilinx和Intel(前身为Altera)提供了专用于该供应商技术的专用综合编译器。

SystemVerilog是一种两用语言。一个目的是对数字硬件的行为进行建模。第二个目的是编写验证程序来测试硬件模型。这两个目的有非常不同的语言要求。许多通用编程结构对于这两个目的都很有用,例如,if-else决策或for循环。其他语言特性只能用于验证,例如约束随机测试(random test)生成。这些验证结构并不表示硬件功能,综合编译器也不支持这些验证结构。

IEEE尚未确定SystemVerilog的正式可综合子集。标准的这一缺陷导致了每个综合编译器对可综合SystemVerilog语言子集的支持存在重大偏差。此外,由特定综合编译器标识的子集可以(几乎肯定会)将综合产品的一个版本更改为该产品的下一个版本。

综合编译Synthesis Compilation

综合编译器的目标与仿真编译器不同。这两种类型的编译器都需要检查SystemVerilog RTL源代码的语法正确性,但这就是相似性的终点。仿真是一个动态过程,涉及仿真时间、事件调度、应用刺激和验证输出。综合是一个静态转换和优化过程,不涉及任何这些仿真目标。综合编译器需要确保代码满足必要的语言限制,以便将RTL功能转换为ASIC和FPGA实现中支持的逻辑门类型。这些限制包括检查RTL代码是否具有明确定义的时钟周期活动、单驱动程序逻辑等,综合编译器只需要编译RTL模型。综合不需要编译带有激励生成和输出验证的测试台代码。

单文件和多文件编译

大型设计被划分为许多子块。通常,每个子块将存储在单独的文件中,为了仿真分区设计,仿真要求所有这些子块都被编译并连接在一起。另一方面,综合通常可以分别编译和处理每个子块。综合优化和技术映射是计算密集型过程。将太多的子块合成在一起可能会导致结果质量(QOR)不理想。

在综合设计的子块时,有两个重要的考虑因素。首先,来自定义包的子块中使用的任何定义都要求该包与子块一起编译,并以适当的方式按照顺序编译,如果多个子块使用同一个包,则需要使用与其他子块分开编译的每个子块重新编译包,第二个考虑因素是,在每个单独的编译中都不会看到任何全局声明,包括“定义编译器指令”。

约束条件

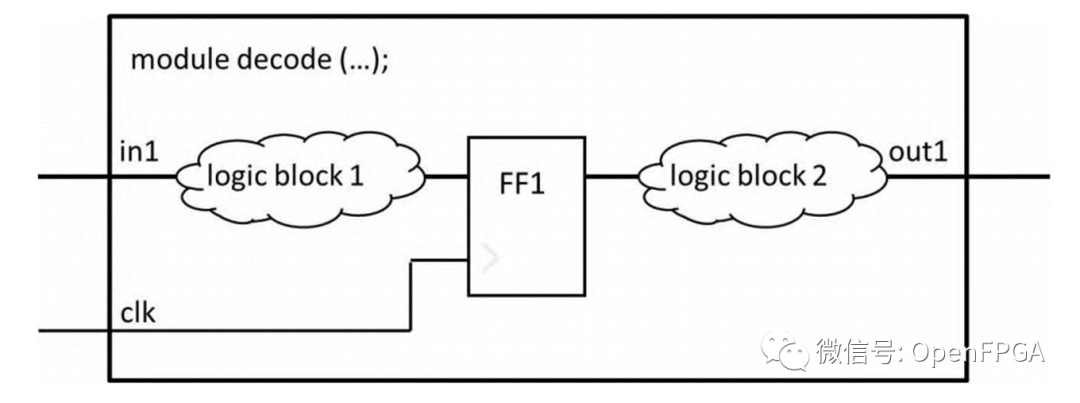

图1-10显示了综合的三个主要输入之一是约束。约束用于定义综合所需的信息,但这些信息既不在RTL模型中,也不在ASIC/FPGA供应商的技术库中。图1-11说明了一个简单的电路,其中综合所需的一些信息必须由设计工程师指定。

图1-11:需要综合约束的简单电路图

将此功能数据流综合成逻辑门的过程包括:

- 将综合的触发器FF1映射到目标ASIC或FPGA中的适当触发器。

- 将logic_block_1中描述的功能映射到目标ASIC或FPGA的标准单元或逻辑块。

- 优化logic_block_1的布局布线,以满足FF1建立时间和保持时间要求 - 将logic_block_2中描述的功能映射到目标ASIC或FPGA的标准单元或逻辑块。

- 优化logic_block_2的布局布线,以满足建立时间和保持时间要求。

为了在目标ASIC或FPGA中实现图1-11所示的简单电路,综合编译器必须知道:

- 用于实现logic_block_1和logic_block_2的标准单元或逻辑块的传播延迟、面积和功率要求。

- FF1建立时间和保持时间。

- clk的周期或频率,如100Mhz。

- in1相对于CLK边沿的到达时间。

- in1外部电源的驱动能力

- 相对于clk边沿的out1的到达时间。

- out1的输出驱动要求。

此信息不在RTL模型中。此列表中前两项的规范,传播延迟和建立/保持时间,将来自ASIC或FPGA供应商提供的技术库,其余细节必须由综合设计的设计工程师指定。这些规范被称为综合约束,更大、更复杂的设计将需要更多的综合约束,后续的RTL编码示例将在适当的情况下讨论适用的综合约束。还提供了简化必须指定的约束的指南。

指定综合约束的方式因不同的合成编译器而异。推荐读者阅读《综合和时序分析的约束设计Constmining Designs for Synthesis and Timing Analysis》文档了解此信息。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。