介绍

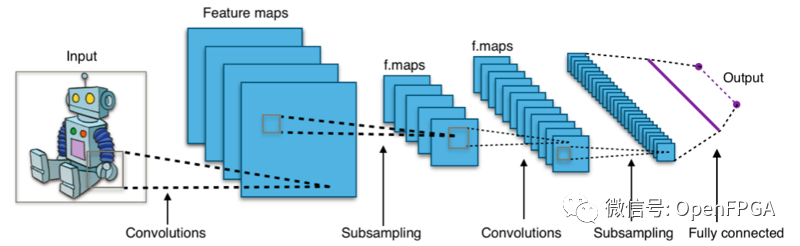

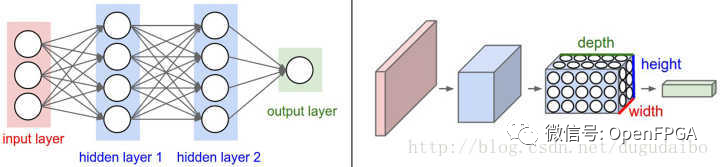

在深度学习中,卷积神经网络(CNN或ConvNet)是一类人工神经网络(ANN),最常用于分析视觉图像。

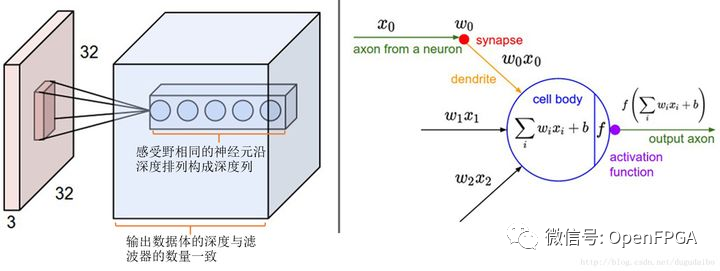

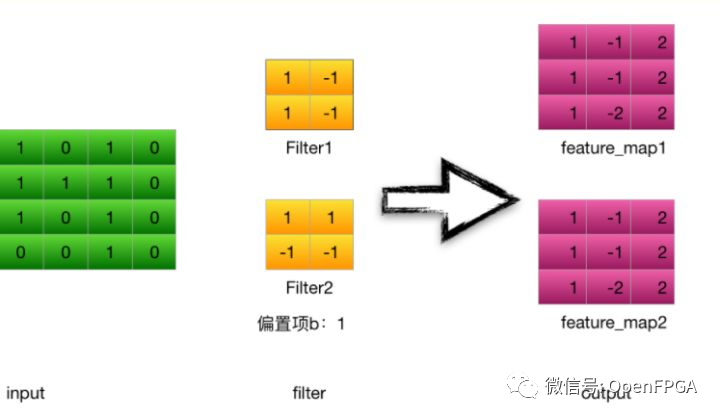

CNN 也称为移位不变或空间不变人工神经网络(Shift Invariant or Space Invariant Artificial Neural Networks ,SIANN ),它基于卷积核或滤波器的共享权重架构,沿输入特征滑动并提供称为特征映射的平移等变响应。它们在图像和视频识别、推荐系统、图像分类、图像分割、医学图像分析、自然语言处理、脑机接口和金融时间序列中都有应用。

CNN 是多层感知器的正则化版本。多层感知器通常表示全连接网络,即一层中的每个神经元都连接到下一层中的所有神经元。这些网络的“完全连通性”使它们容易过度拟合数据。正则化或防止过拟合的典型方法包括:在训练期间惩罚参数(例如权重衰减)或修剪连接性(跳过连接、丢失等) CNN 采用不同的正则化方法:它们利用数据中的分层模式并使用在过滤器中压印的更小更简单的图案来组装复杂度越来越高的图案。因此,在连接性和复杂性的规模上,CNN 处于较低的极端。

与其他图像分类算法相比,CNN 使用的预处理相对较少。这意味着网络通过自动学习来学习优化过滤器(或内核),而在传统算法中,这些过滤器是手工设计的。这种独立于先验知识和特征提取的人为干预是一个主要优势。

cnn_hardware_acclerator_for_fpga

https://github.com/sumanth-kalluri/cnn_hardware_acclerator_for_fpga

这是完全参数化的 Verilog 实现CNN,用于加速 FPGA 上的卷积神经网络推理

软件工具:

设计 - Xilinx Vivado 2017

验证 - Python 3.6 和 Xilinx ISE 14.7 命令行工具

convolution_network_on_FPGA

https://github.com/hunterlew/convolution_network_on_FPGA

描述

该项目使用 ISE 14.7 和 vertix-7 FPGA 构建。它使用某些加速策略执行 7 层网络前向计算。首先,使用MatConvNet在 MSTAR 数据集上训练一个 SAR 目标分类网络,并使用 early-stop。然后,使用 Matlab 将权重和输入转换为 FPGA 可以加载的 COE 文件。接下来,设计原生 verilog 编写的模型来完成前向计算。系统使用 16 位定点数据来保持精度。结果证明,它每张图像的花费不到 1ms,优于其他计算平台。

加速

第一个转换需要对 FPGA 的资源和速度之间权衡,考虑到第一个转换中输入和权重的大小,如果层较大,那么该层就应该使用移位寄存器结构进行加速。另一个转化,层仅需要使用管道结构。请注意,有 18 个文件以 m_conv_1 命名,表示第一个 conv 中有 18 个移位寄存器。

对于带宽的限制,第二个转换层,使用通道分组并行化方案。使用 v7-415t 和 v7-485t FPGA 进行比较,它们根据不同的资源量使用不同的组号(4 vs 1)。可能会注意到文件 CNN_top.v 中的方案,其中包含控制通道分组和合并的信号“ram_ready”。

CNN-FPGA

https://github.com/QShen3/CNN-FPGA

有以下几个模块:

Conv2d

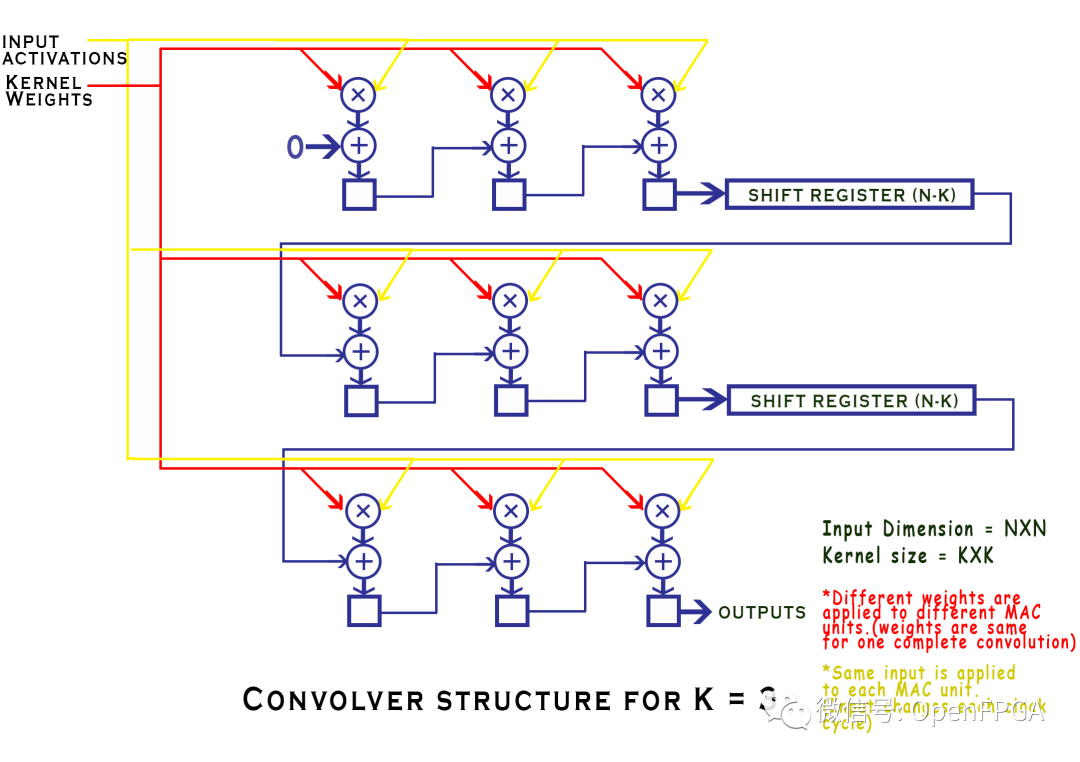

说明:

卷积模块,可以进行二维卷积。支持多个卷积核,不同步长,是否启用边缘0填充等

可配置参数:

PADDINGENABLE 边缘是否使用0填充,1代表是,0代表否 0

输入输出:

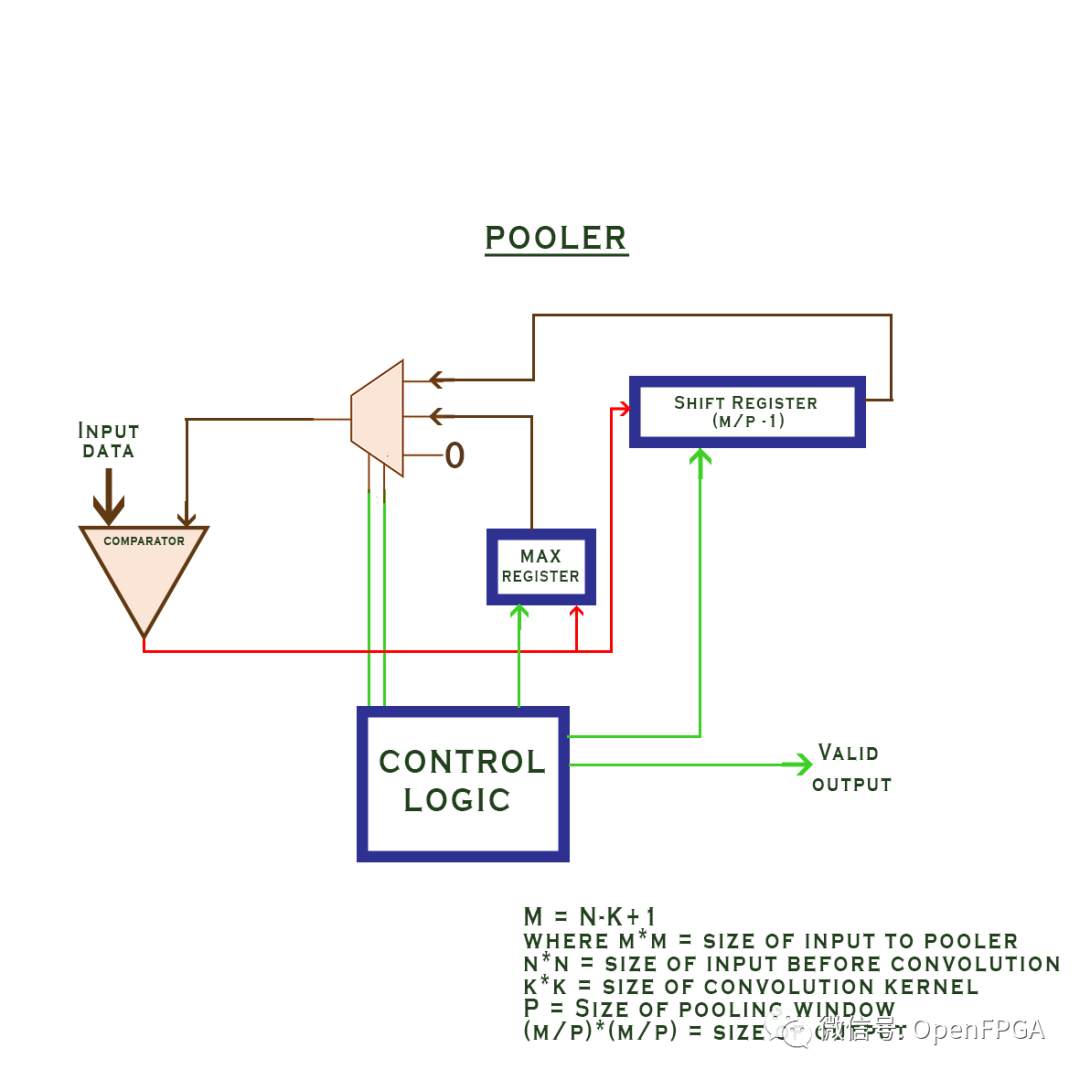

Max_pool

说明:

最大池化模块,可以对输入进行最大池化运算。

可配置参数:

输入输出:

FPGA-CNN

https://github.com/dem123456789/FPGA-CNN

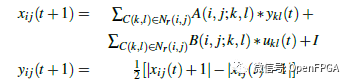

FPGA 实现的CNN:

CNN.v是顶层设计,初始化A,B,I。模板为16x16层模块sixteenbysixteen.v

SixteenbySixteen.java生成Verilog代码

clacc

https://github.com/taoyilee/clacc

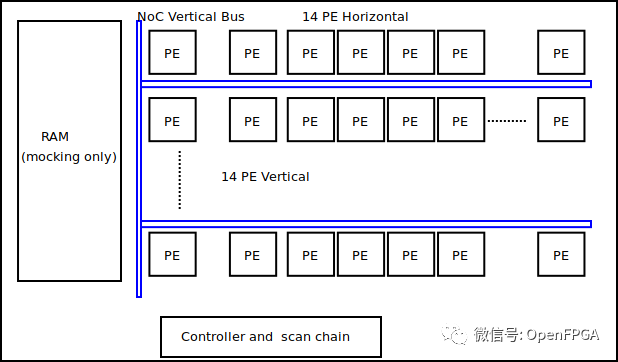

原为清华大学深度学习硬件加速器课程项目,由林允龙教授主讲。该课程相当于斯坦福大学的CS231n(http://cs231n.stanford.edu/)。

深度学习加速器(卷积神经网络)

这是在 Verilog 中实现类似 MIT Eyeriss 的深度学习加速器

注:clacc代表卷积层加速器

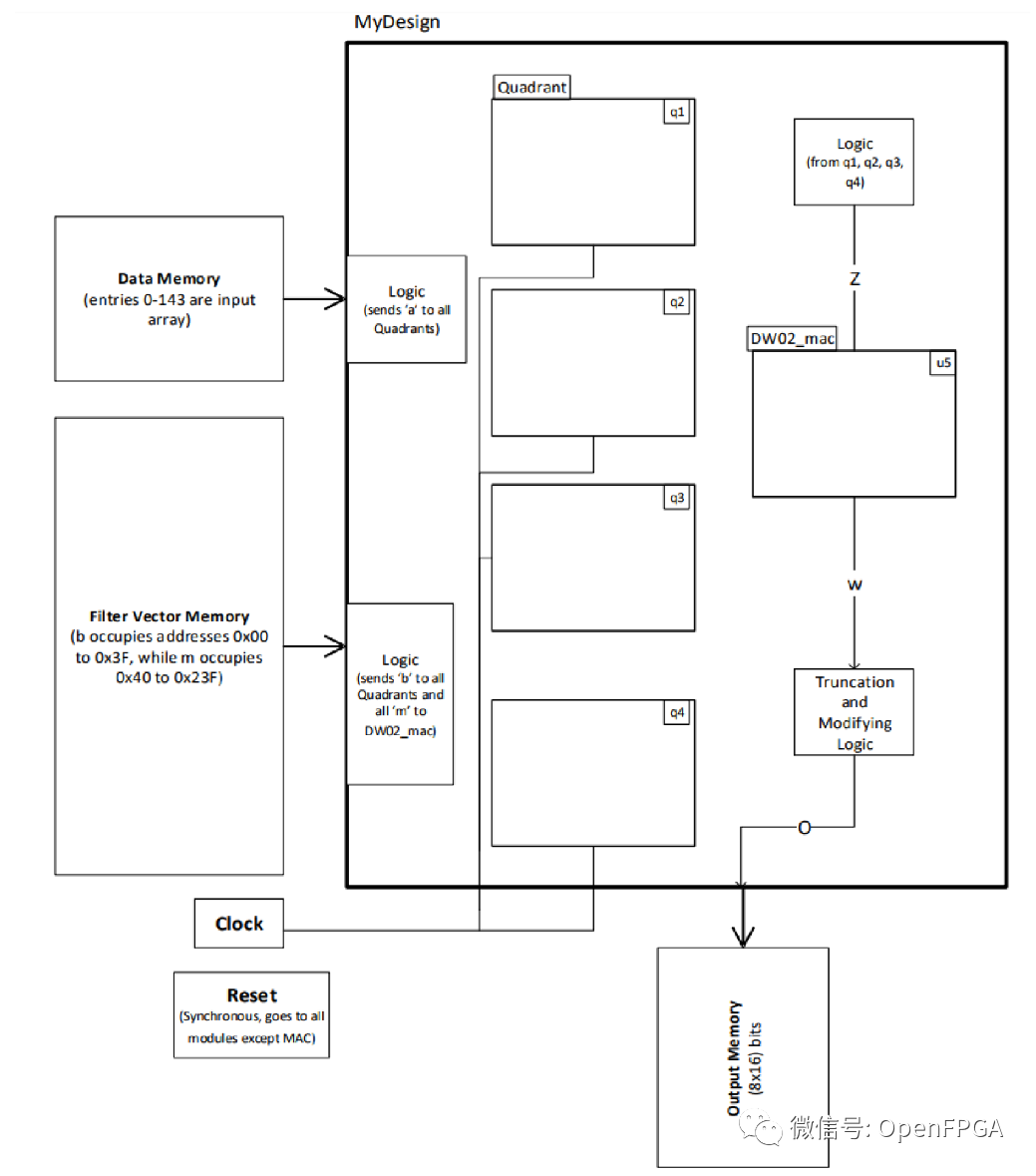

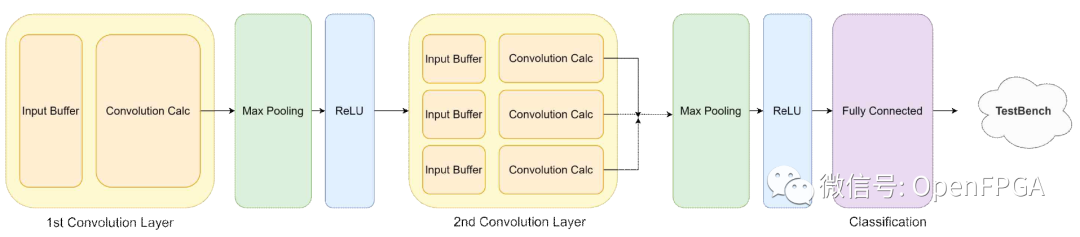

RTL-Implementation-of-Two-Layer-CNN

https://github.com/Haleski47/RTL-Implementation-of-Two-Layer-CNN

https://github.com/Di5h3z/ECE-564-Convolutional-Neural-Network-Accelerator

具有详细设计的两层 CNN

详细的设计文档:

https://github.com/Haleski47/RTL-Implementation-of-Two-Layer-CNN/blob/master/report/Apar Bansal ECE564 Project.pdf

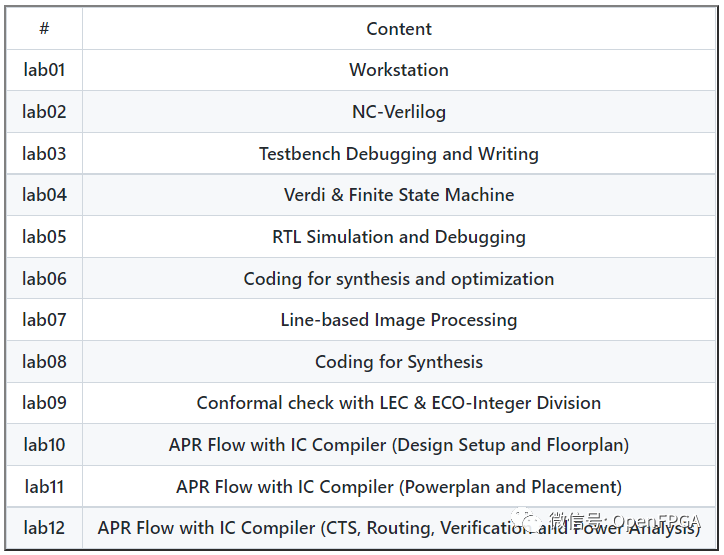

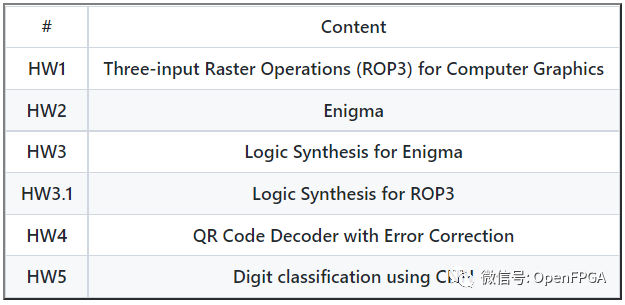

NTHU-ICLAB

https://github.com/LeoTheBestCoder/NTHU-ICLAB

这是清华大学IC LAB提供的一个非常详细的设计项目,逐步实现一个CNN,并附带测试项目。

下面是每一步的功能,并且每一步都有详细的设计文档。

最终实现:使用 CNN 进行数字分类

ES203-COA-CNN

https://github.com/akcgjc007/ES203-COA-CNN

具体的实现过程:

代码介绍:

https://www.youtube.com/watch?v=3J2X-j0z2M8

结果:

MNIST_CNN_HDL

通过硬件加速提升 CNN-mnist 的性能

文件夹“design_files”包括硬件中的所有设计文件

文件夹“verification_files”是设计文件的验证环境

文件夹“weights”包括 mnist 和输入图像的权重

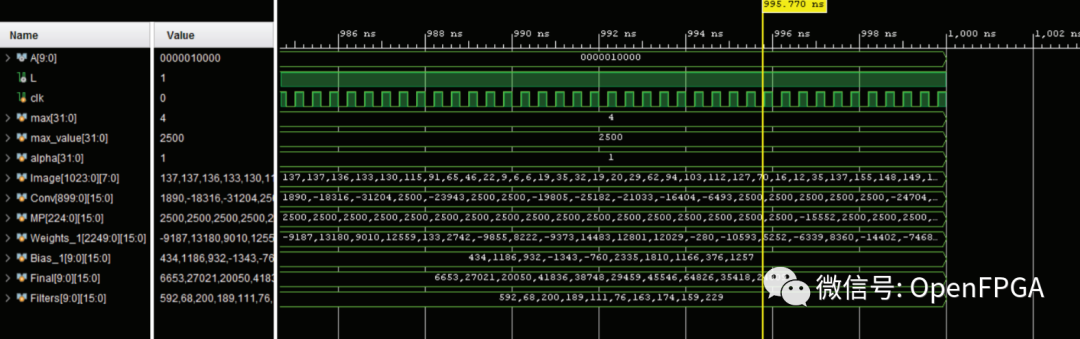

CNN-Implementation-in-Verilog

https://github.com/boaaaang/CNN-Implementation-in-Verilog

使用 Python & Verilog 实现卷积神经网络

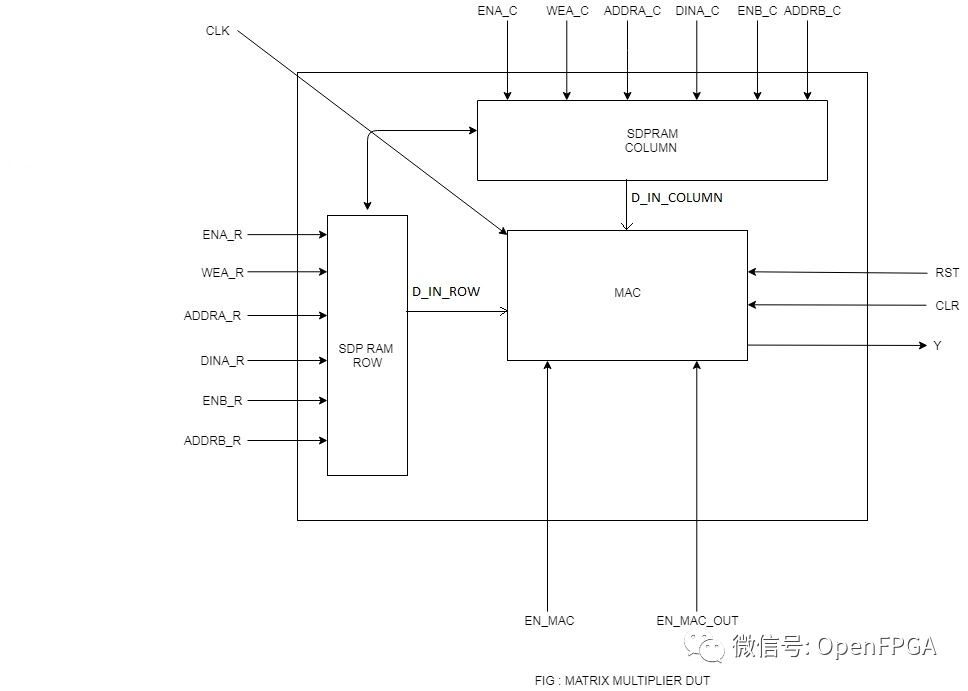

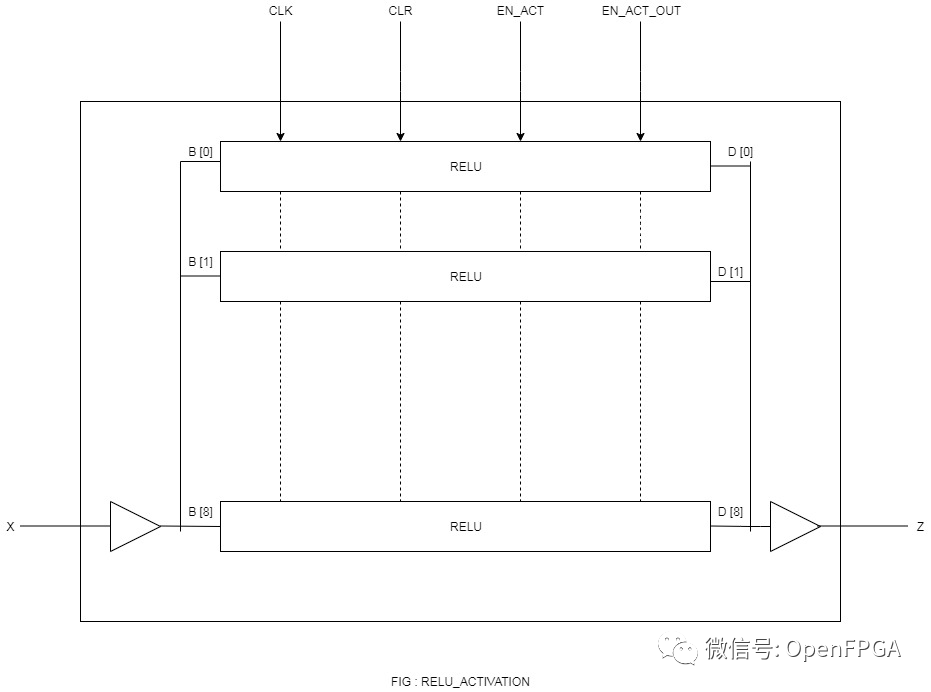

实现框图:

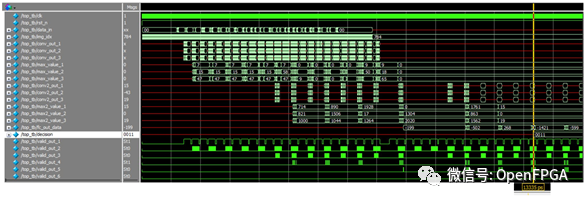

仿真波形

CNN_Core

https://github.com/0x5b25/CNN_Core

- 使用 Altera Avalon-MM 总线

- 使用 quartus prime ide 在 Stratix IV 上编译和测试。

- 更多介绍请参考instructions.txt

CNN-Accelerator-VLSI

https://github.com/lirui-shanghaitech/CNN-Accelerator-VLSI

详细要求在./resource/Project_2.0.pdf中有详细介绍。

下面列出一些主要要求:

- 所有输入特征图和权重的位长为 8 位,输出为 25 位数据。

- 输入特征图带宽为8x8位,权重带宽也是8x8位(最大同时读取8个输入特征图和8个权重)

- 输出带宽为 2x25 位(最多同时将 2 个输出写入主存)

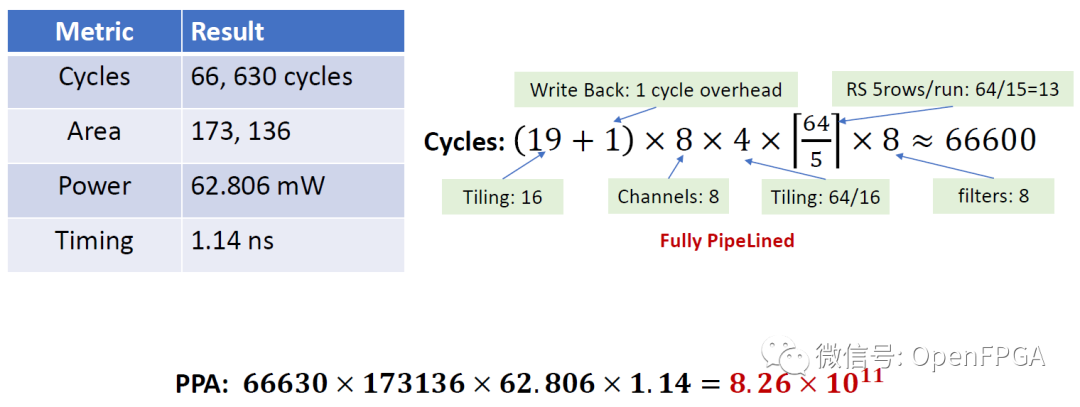

结果如下:

注意:这个项目有一部分所需的文件没有公开,但是,可以将此设计合成到 FPGA。

CNN-FPGA

https://github.com/omarelhedaby/CNN-FPGA

在ZYNQ FPGA上实现CNN,使用MNIST数据库对手写数字进行分类

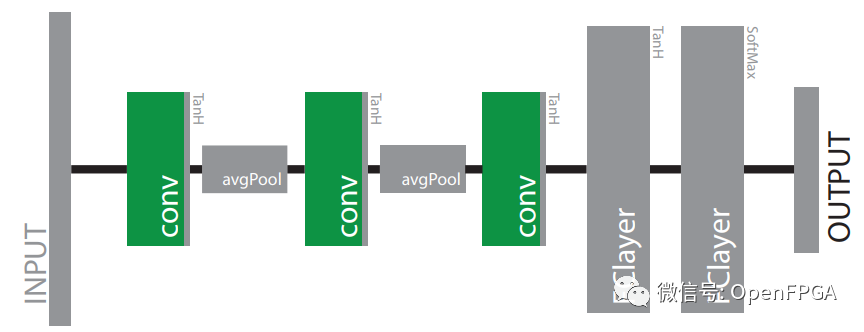

网络 Conv2D->Tanh Activation->AvgPool->Conv2D->Tanh Activation->AvgPool->Conv2D->Tanh Activation->全连接层->Relu->全连接层->Softmax

该项目很完整,虽然Readme写的不是很完整,但是有个详细的设计、仿真及验证完档。

https://github.com/omarelhedaby/CNN-FPGA/blob/master/Hardware Documentation.pdf

Image-Classification-using-CNN-on-FPGA

https://github.com/padhi499/Image-Classification-using-CNN-on-FPGA

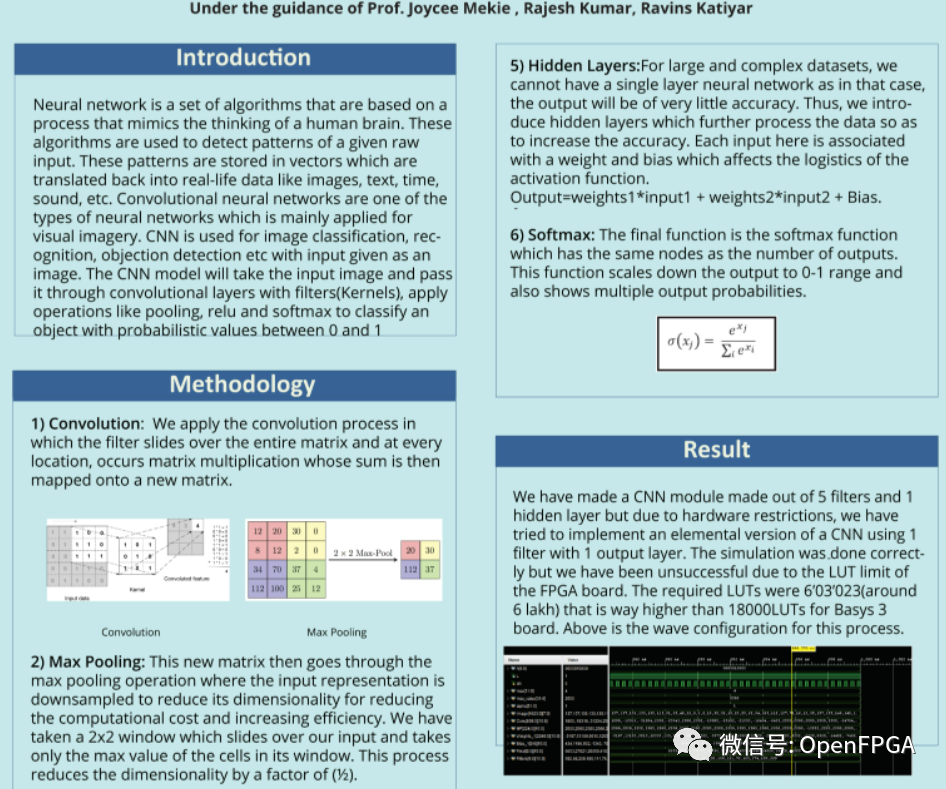

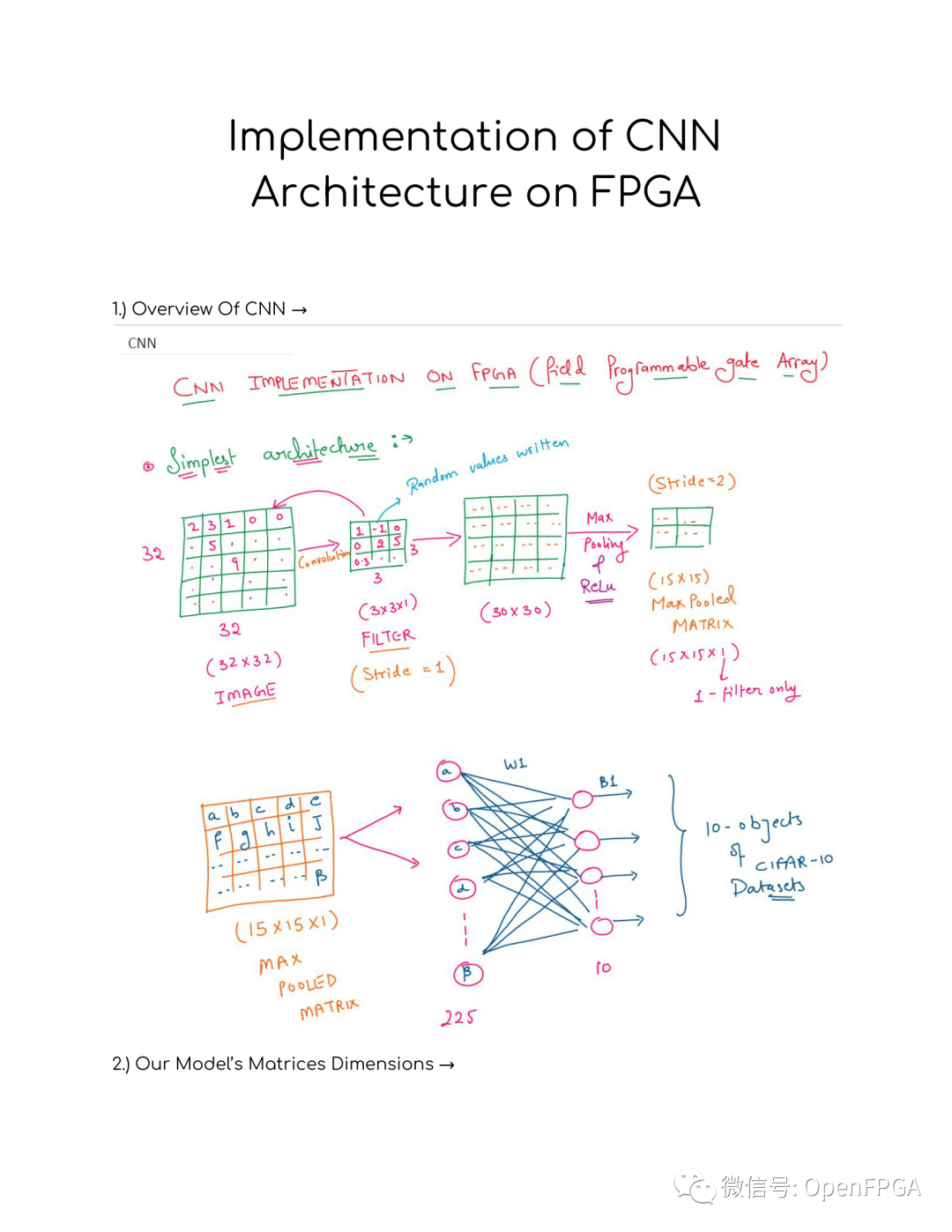

简介

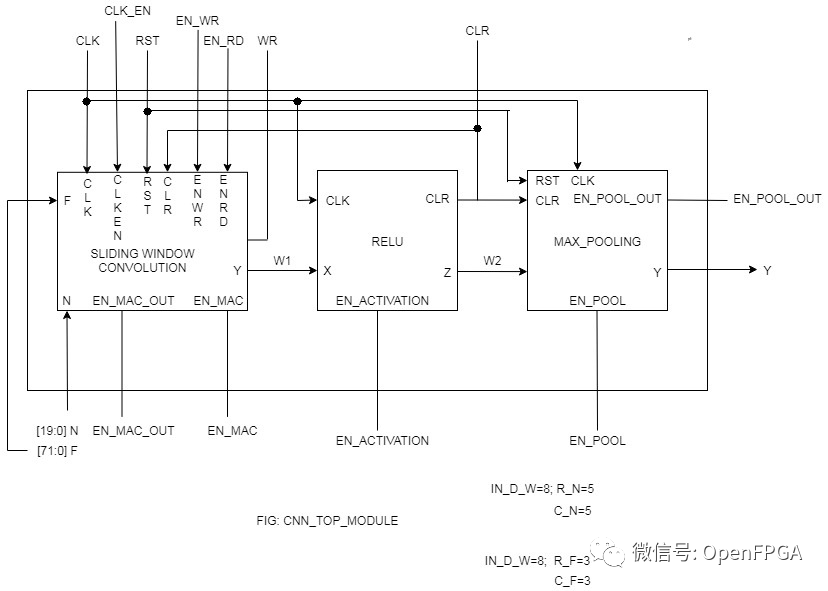

在 FPGA 上使用 CNN 进行图像分类

项目是关于在 FPGA 上设计一个经过训练的神经 n/w(CIFAR-10 数据集),以使用深度学习概念(CNN-卷积神经网络)对图像 I/P 进行分类。

有 6 层(滑动窗口卷积、ReLU 激活、最大池化、扁平化、完全连接和 Softmax 激活)决定了我们的 I/P 图像的类别。内核/过滤器用于从图像 I/P 进行特征检测。图像 I/P 可以是灰度/彩色的。

使用的工具

- Vivado v17.4

- Matlab vR2018.a

DigitalRecognition

https://github.com/suisuisi/FPGAandCNN

《基于FPGA的数字识别-实时视频处理的定点卷积神经网络实现》

posture_recognition_CNN

https://github.com/cxdzyq1110/posture_recognition_CNN

简介

基于CNN的姿态识别

帮助机器通过摄像头了解我们人类在做什么是很重要的。一旦实现,机器就可以对人类的各种姿势做出不同的反应。但是这个过程也非常困难,因为通常这个过程实现不仅速度跟不上并且耗电,同时也需要非常大的内存空间。

这里我们专注于实时姿势识别,并尝试让机器“知道”我们做出什么姿势。姿态识别系统由DE10-Nano SoC FPGA Kit、摄像头和HDMI监视器组成。SoC FPGA 从摄像头捕捉视频流,通过 CNN 模型识别人体姿态,最后通过 HDMI 接口显示原始视频和分类结果(站立、行走、挥手等)。

我们上传我们的项目,包括 Matlab、Python 和 Quartus。

软件版本:

- Matlab r2017b

- Python 3.6.3

- Anaconda 5.1.0

- TensorFlow-gpu 1.3.0

- Quartus 14.0

同时在该仓库中含有作者的论文,论文中包含详细的设计。

NPU_on_FPGA

https://github.com/cxdzyq1110/NPU_on_FPGA

目的 在FPGA上面实现一个NPU计算单元。能够执行矩阵运算(ADD / ADDi / ADDs / MULT / MULTi / DOT等)、图像处理运算(CONV / POOL等)、非线性映射(RELU / TANH / SIGM等)。

- 优点 考虑到灵活性较强,易于修改网络结构,适用于实现小型CNN/RNN网络。

- 缺陷 由于指令串行执行、缺少Cache导致外存读写频繁,运算性能较低。

该项目也是上面项目的同一作者,详细的设计,完整的工程,值得去操作一下。

neural-engine

https://github.com/hollance/neural-engine

大多数新的 iPhone 和 iPad 都有神经引擎,这是一种特殊的处理器,可以让机器学习模型变得非常快,但对于这种处理器的实际工作原理,公众知之甚少。

Apple 神经引擎(或 ANE)是NPU的一种,代表神经处理单元。它就像 GPU,但 NPU 不是加速图形,而是加速卷积和矩阵乘法等神经网络操作。

ANE 并不是唯一的 NPU——除了 Apple 之外,许多公司都在开发自己的 AI 加速器芯片。除了神经引擎,最著名的 NPU 是谷歌的 TPU(或 Tensor Processing Unit)。

这个项目并不是一个实现CNN的项目,但是是一个关于Apple 神经引擎(或 ANE)介绍及相关文档的集合的项目。

总结

今天介绍了N个CNN的项目,前面的项目比较“单薄”,只适合学习CNN设计,从NTHU-ICLAB(包含)之后的项目更适合实践,因为这些项目都有详细的设计文档及板卡验证过程。

结合之前的TPU及今天的相关项目,大家应该对神经网络应该不会再恐惧了,下一篇文章我们将介绍一些DNN项目,将这个系列完善一下。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。