ISP即Image Signal Processor,是一种图像处理架构,不是我们用的下载器。

ISP其实算是图像处理的一个特例,一般应用于前端设备(相对于SENSOR),从结果上看就是将RAW数据转换成压缩后的RGB(一般)数据,供后续CPU使用(识别、压缩等)。

市面上很少有直接介绍ISP的书籍或者资料,今天我们主要是聊一聊ISP算法的架构,这样大家就能明白为什么很少有专用的书籍对这方面进行介绍了。

ISP算法介绍

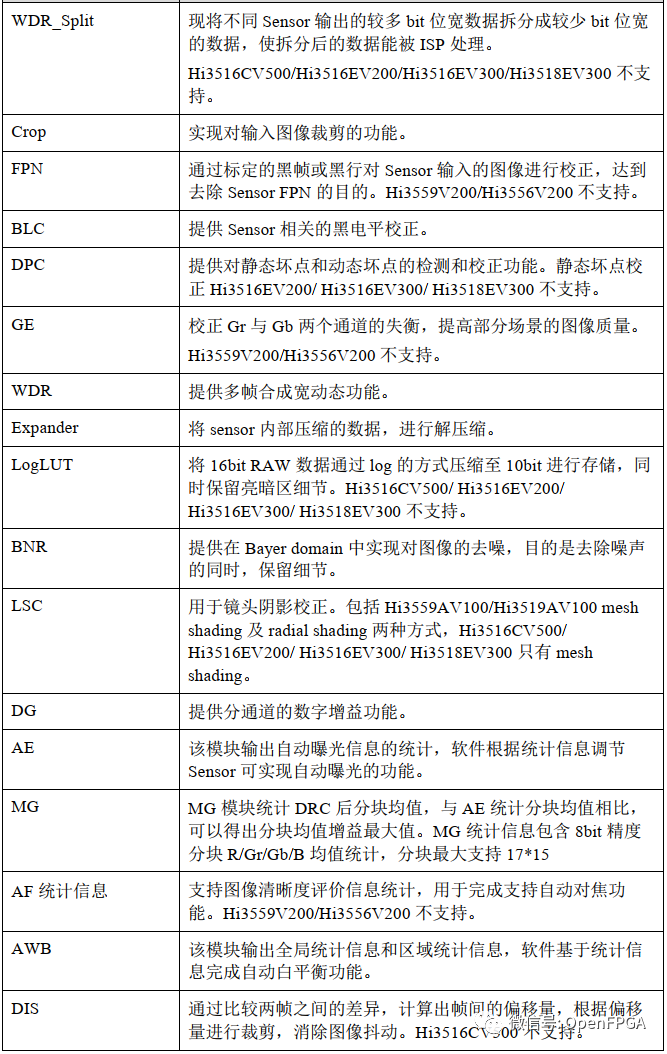

ISP是一类算法统称,这一类算法通常包含下列算法:

海思架构

海思IC是国内很成熟的芯片了,其针对前端的芯片也是在业内广受好评,我们先看看海思内部的ISP架构(Hi3559A为例,其他芯片有功能增减)。

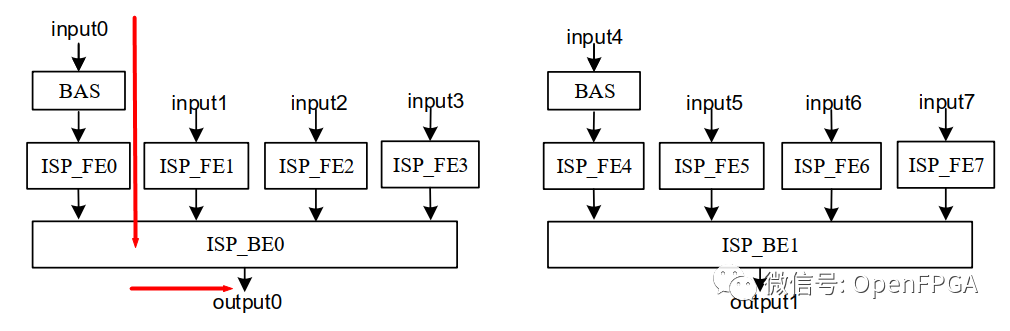

Hi3559A(下称3559A)ISP的整体结构如下:

ISP 整体结构图(Hi3559AV100)

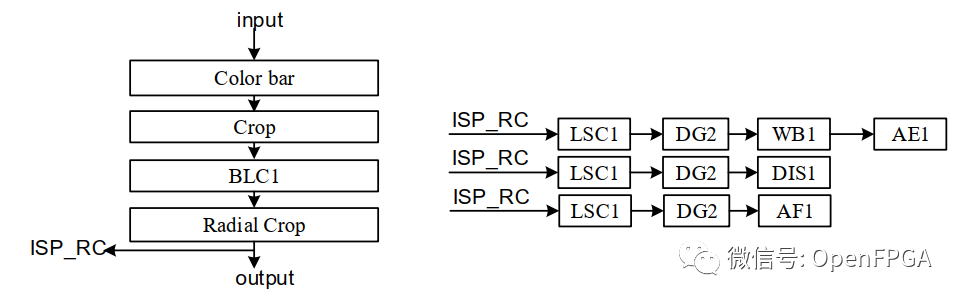

因为3559A是个多摄像头输入的SoC,所以有多路ISP集合,我们只关心最左边红线线路。继续拆分,下图是ISP FE架构(上图中的ISP_FE0):

ISP_FE 结构图(Hi3559AV100)

下图是ISP BE结构图:

ISP_BE 结构图(Hi3559AV100)

- 图中 CSC1,CSC2,CSC3 功能和 CSC 一致。

- 图中 OTEF1 功能和 OETF 一致。

- 图中 DG1,DG2 功能和 DG 一致。

- 图中 CCM1, CCM2, CCM3, CCM4 功能和 CCM 一致。

- 图中 TM1 功能和 TM 一致。

- 图中 CD1,CDS2 功能和 CDS 一致。

- 图中 AF1 功能和 AF 一致。

- 图中 AE1 功能和 AE 一致。

- 图中 DIS1 功能和 DIS 一致。

- 图中 LSC1 功能和 LSC 一致。

- 图中 WB1 功能和 WB 一致。

- 图中 SHARPEN1 功能和 SHARPEN 一致。

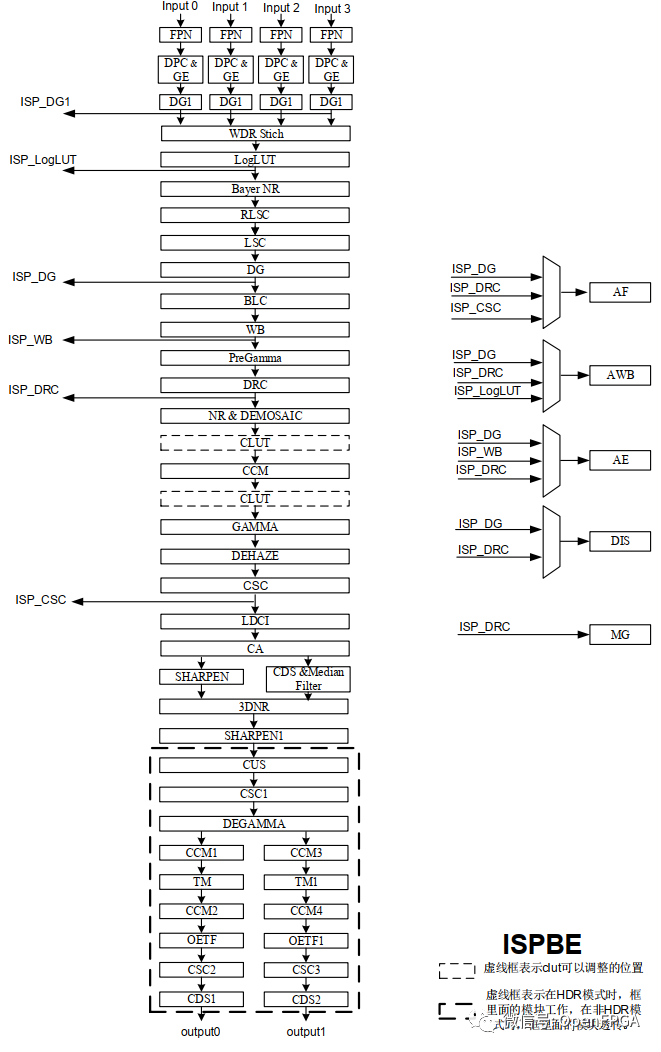

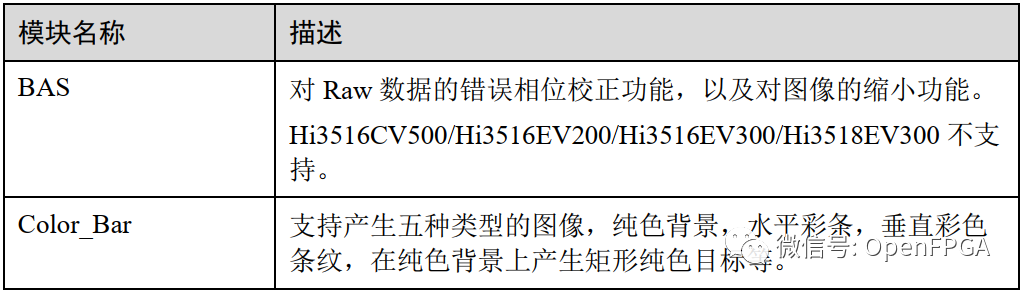

上面都是一些专用术语的缩写,所以接下来简单介绍一下这些缩写:

ISP 术语简介(Hi3559AV100)

上图中是一些术语简介,因为一些特殊原因只能截图,请忽略一些特殊的字符。源文档会在文末提供(只用于学习,切勿商用)。

3559A是一个通用ISP,所以功能很全,如果用FPGA去实现这些,估计没有几个能做出来,ISP的特殊点就是针对不同的镜头、环境、Sensor等不同去调整需要实现的算法。

上面的介绍只是一个开头,只是想让大家知道ISP主要包含哪些算法以及一些专用术语(建议保存),下面才开始我们的介绍,用FPGA实现ISP的通用架构分析。

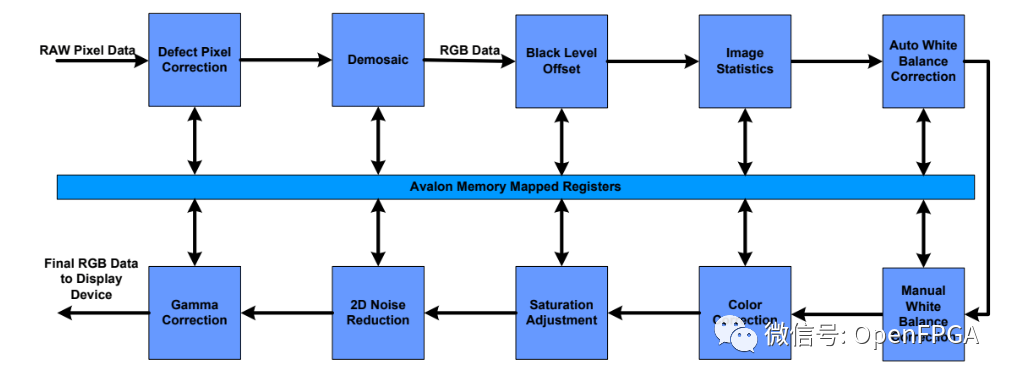

利用AXI总线实现ISP通用架构

在Xilinx FPGA中AXI总线应用的比较多,尤其针对多模块互联的情况,下面给出一个Xilinx FPGA使用的较通用的ISP架构:

Xilinx FPGA ISP 整体结构示意图

所有的算法串行运行,利用AXI-lite总线进行管理,这样可以大大增加系统的灵活性(后续调参方便),至于内部算法需要针对自己应用选配,按照目前的架构可以很方便的进行增加或者减少算法种类。

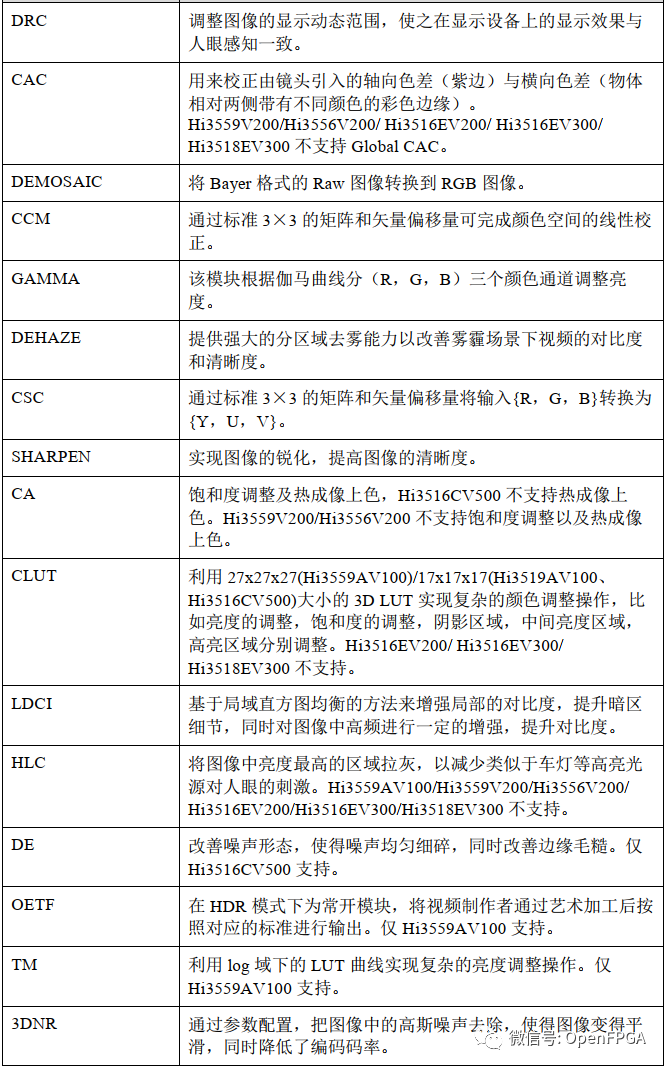

利用Avalon总线实现ISP通用架构

Intel/Altera FPGA ISP 整体结构示意图

利用Avalon总线和上一节的AXI总线效果一样,功能一样。

其中3A算法的实现也有多种方式实现,可以直接FPGA内部硬件实现,也可以在外面放置单片机实现,最通用的可能就是内部MicroBlaze/Nios去管理也大大减少了开发难度。

总结

因为ISP算法的特殊性,很少有专用书籍去介绍这一类知识,但是今天带领大家了解一下通用架构后大家应该就可以根据自己的需求去找自己系统里需要的算法知识就可以了。同时上面针对Xilinx或者Intel厂家FPGA的ISP架构,只是一个通用算法架构示意图,每个公司都有自己的架构,也有全HDL实现的方案,只不过不适合我们本篇文章去解析。最后还是说明一下,ISP中所有的算法都是图像算法,大家需要先学习图像算法,同时切记一定要使用一些高级语言先验证自己的算法再去转换成HDL,而不是直接上来就是我先实现个“ISP”。

下面针对这方面的知识,推荐一些资料:

3559A相关资料:

链接:https://pan.baidu.com/s/1xDQHnhGcGG4F5u7tKi_P0Q?pwd=open 提取码:open

sersor及isp介绍(数码相机中的图像传感器和信号处理):

链接:https://pan.baidu.com/s/17AAfO9SUyDrSRj2YH3FXXQ?pwd=open 提取码:open

数字图像处理:

链接:https://pan.baidu.com/s/1vcc7M2wKYU80AjNApUupPw?pwd=open 提取码:open

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。