介绍

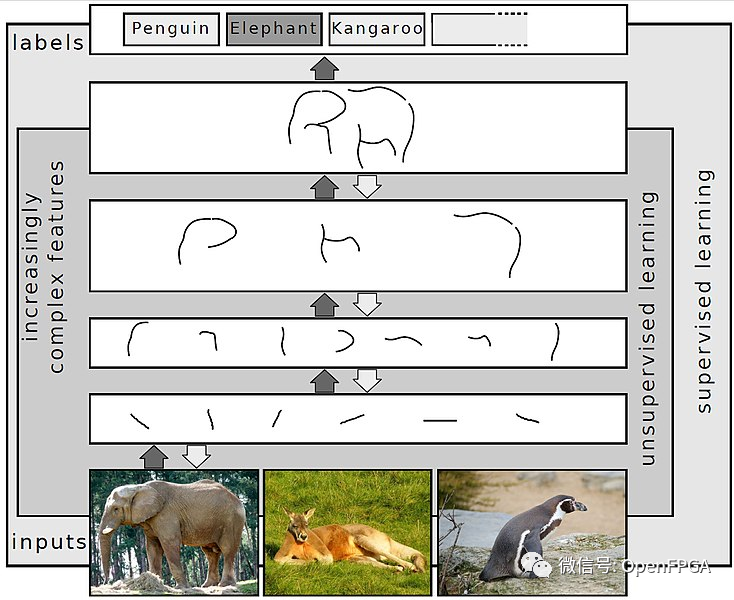

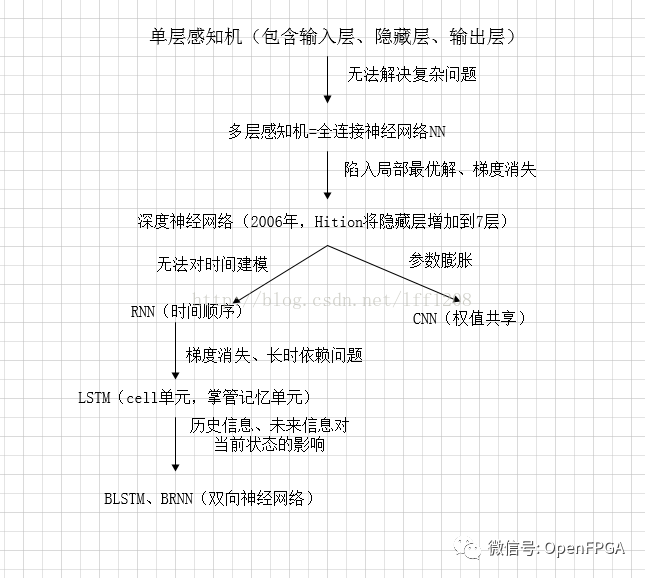

深度神经网络 (DNN) 是一种人工神经网络(ANN),在输入层和输出层之间具有多层。有不同类型的神经网络,但它们基本由相同的组件组成:神经元、突触、权重、偏差和函数。这些组件的功能类似于人类大脑,可以像任何其他 ML 算法一样进行训练。

例如,经过训练以识别狗品种的 DNN 将遍历给定的图像并计算图像中的狗是某个品种的概率。用户可以查看结果并选择网络应该显示哪些概率(超过某个阈值等)并返回建议的标签。每个数学操作都被认为是一个层,复杂的 DNN 有很多层,因此被称为“深度”网络。

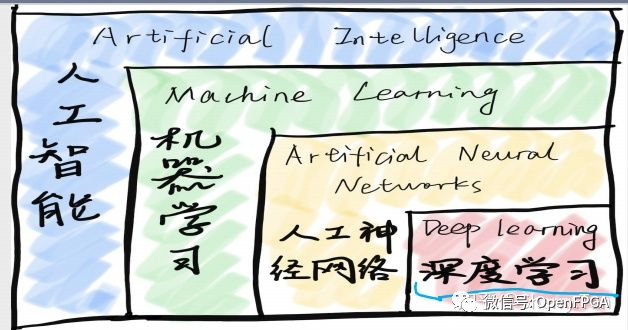

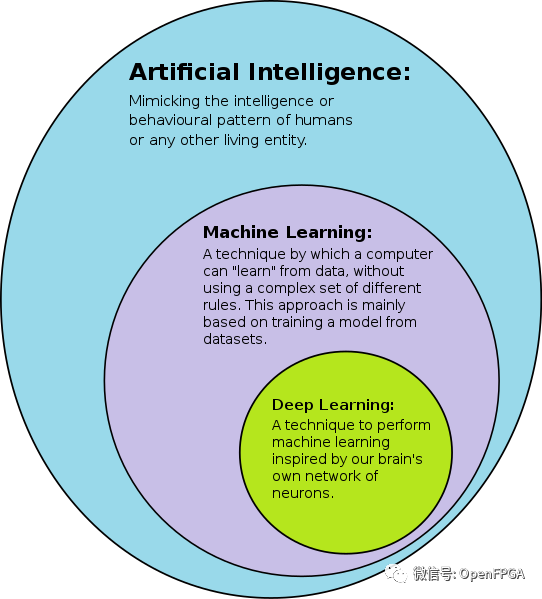

关于DNN、ANN、CNN区别,请看下图:

https://blog.csdn.net/lff1208/article/details/77717149

IBM_AccDNN

https://github.com/IBM/AccDNN

AccDNN(深度神经网络加速器核心编译器)又名;DNNBuilder

项目介绍

在这个项目中,我们提出了一种新颖的解决方案,可以自动将经过 Caffe 训练的深度神经网络转换为 FPGA RTL 级别的实现,无需任何编程工作,并为用户的识别任务提供统一的 API。

因此,没有任何 FPGA 编程经验的开发人员可以将他们的 FPGA 加速深度学习服务部署在数据中心或边缘设备中,仅提供他们经过训练的 Caffe 模型。该作品发表在 ICCAD'18 上,并获得了前端最佳论文奖。了解更多设计细节。请参考我们的论文(https://docs.wixstatic.com/ugd/c50250_77e06b7f02b44eacb76c05e8fbe01e08.pdf)。

转换过程

转换包括三个阶段:

- 首先对 Caffe 网络文件进行解析,得到网络结构。我们估计每一层的工作量以确定在 FPFA 资源约束下的并行度。

该网络中定义的每一层通过在库中实例化相应的神经层来生成一个定制的 Verilog 模块。顶层模块也是根据net文件中定义的层顺序将这些自定义实例连接在一起生成的,并且在这个阶段也生成了权重所需的片上内存。

- 综合生成的源文件、布线和布局,生成可执行的 FPGA 位文件。

AccDNN 缺点

- 仅支持 Caffe 框架训练的模型。

- 仅支持卷积层、最大池化层、全连接层和批量归一化层。

- Caffe .prototxt 中定义的网络中卷积层和全连接层的总数应少于 15 层

DNN-Hardware-Accelerator

介绍

在本实验中,将以嵌入式 Nios II 系统为核心构建深度神经网络加速器。在本项目中还将学习如何与片外 SDRAM 连接,以及如何使用 PLL 生成具有特定属性的时钟。

由于整个系统比我们之前构建的系统更复杂,因此在将设计的所有部分连接在一起之前,编写大量的测试单元并仔细调试将变得尤为重要。

深度神经网络

我们将使用一种称为多层感知器 (MLP) 的神经网络对 MNIST 手写数字数据集进行分类。也就是说,我们的 MLP 将以 28×28 像素的灰度图像作为输入,并确定该图像对应的数字 (0..9)。

MLP 由几个线性层组成,它们首先将前一层的输出乘以权重矩阵,并为每个输出添加一个恒定的“偏差”值,然后应用非线性激活函数来获得当前层的输出(称为激活)。我们的 MLP 将有一个 784 像素的输入(28×28 像素的图像)、两个 1000 个神经元的隐藏层和一个 10 个神经元的输出层;具有最高值的输出神经元将告诉我们网络认为它看到了哪个数字。对于激活函数,我们将使用整流线性单元 (ReLU),它将所有负数映射到 0,将所有正数映射到自身。

在推理过程中,每一层计算a' = ReLU( W · a + b ),其中W是权重矩阵,a是前一层的激活向量,b是偏置向量,a'是当前层的激活向量。

不要被神经网络等花哨的术语吓倒——你实际上是在构建一个加速器来进行矩阵向量乘法。这里的大部分挑战来自与片外 SDRAM 存储器的交互以及正确处理诸如waitrequest和readdatavalid 之类的信号。

不需要知道这些网络是如何训练的,因为我们已经为您训练了网络并预先格式化了图像(请参阅data文件夹的内容和测试输入列表)。但是,如果好奇,可以查看scripts/train.py我们是如何训练 MLP 的。

关于该项目的一些补充说明请查看下面的PDF:

https://github.com/ryaanluke/DNN-Hardware-Accelerator/blob/main/Deep%20Neural%20Networks%20on%20FPGA.pdf

DNN-accelerator-on-zynq

https://github.com/joycenerd/DNN-accelerator-on-zynq

https://github.com/karanam1997/Dnnweaver-Zed-board-/tree/master/DNNWeaver_original

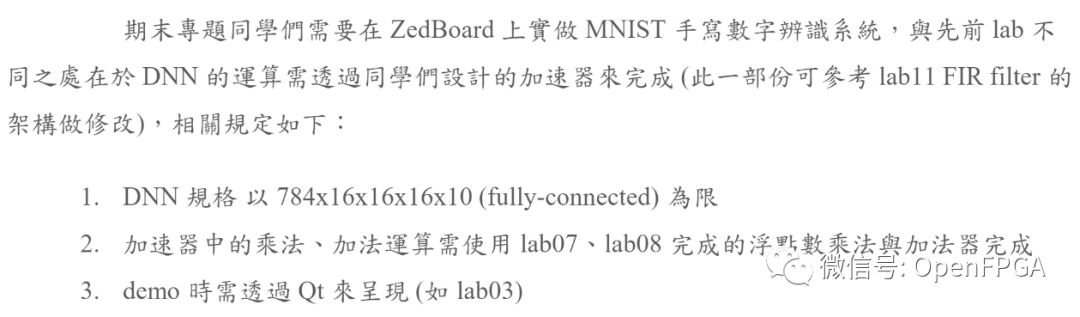

设计要求:

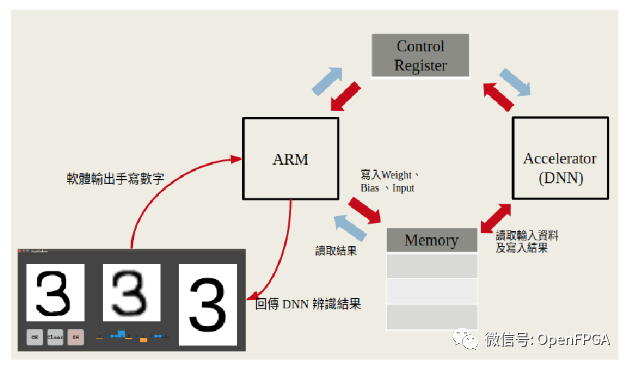

整个系统框图如下:

相关的设计文档:

https://github.com/joycenerd/DNN-accelerator-on-zynq/blob/master/2019DD_lab12Finalv4.pdf

Handwritting-number-distinguishing-with-DNN-by-Nexys-4-DDR-in-Verilog-HDL

https://github.com/MaxMorning/Handwritting-number-distinguishing-with-DNN-by-Nexys-4-DDR-in-Verilog-HDL

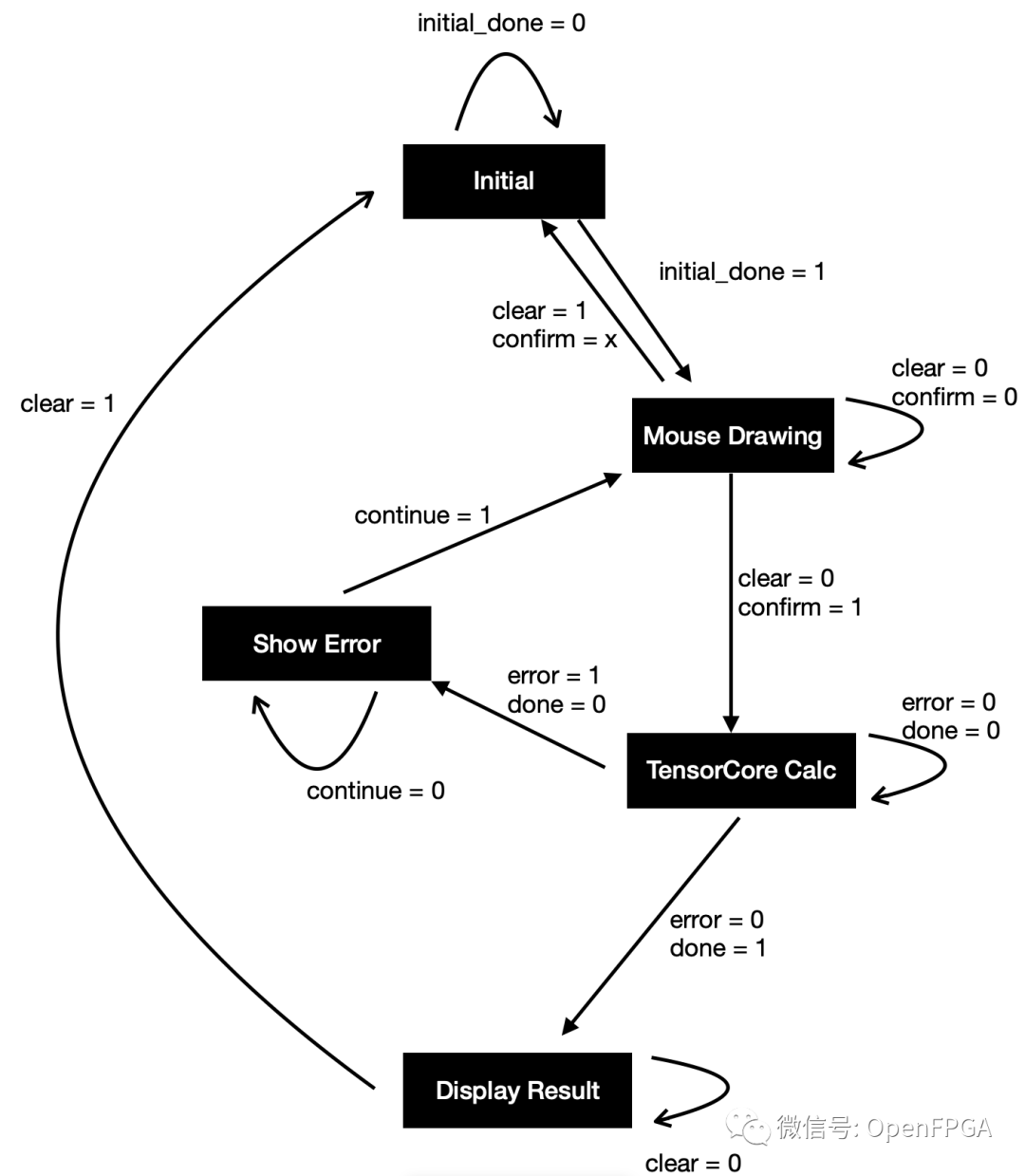

用 Verilog HDL 实现 DNN 区分手写数字,在Nexys 4 DDR 上运行。

总结

今天介绍了3个DNN的项目,主要是DNN复杂度较TPU或者CNN高了几个台阶,所以用它来直接对FPGA进行移植难度很大,还是只建议对第一个IBM项目进行研究,其他在ZYNQ上进行数字识别适合实现,其他都不怎么推荐。

关于DNN或者CNN也介绍了几十个项目了,这些只适合学习研究,并不适合拿来商用,所以后台喷我的小伙伴要求也不要太高,这些开源的项目能直接商用的少之又少,大部分项目只适合学习。还有一些项目是学生做的,所以你们也不必喷:说是拿一些学生做的项目能干什么,我这里只想说,这些项目至少能给您一些参考,什么事情总比从零开始好,或者让你们了解一些同龄人在学校里在干什么,最后,这些项目您又看不上您开源几个出来~

最后再说一下,关于神经网络加速的项目,真正想商用的话,还是老实地跟着官方走,官方提供完整的工具链和架构,不仅节省时间,流程上也是规范了很多。官方的项目介绍:

官方提供的各种案例也是基本覆盖了常规应用。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。