在不久前分享的《2021 OCP Global Summit会议资料下载分享》中,我就曾整理出一个Chiplet分类目录,今天的资料更多点。

本文分享的资料,来自“HiPChips Chiplet Workshop @ ISCA Conference”技术会议,其中“HiPChips” 和 “ISCA”分别是High Performance Chiplet and Interconnect Architectures(高性能Chiplet小芯片及互连架构)、International Symposium on Computer Architecture(计算机体系结构国际研讨会)的缩写。

pdf演讲稿打包下载

https://pan.baidu.com/s/1U7Xc3OHRaFSEk42oEx5nGQ?pwd=nwoj

提取码:nwoj

资料来源 https://www.opencompute.org/summit/ocp-at-the-isca-conference/slides(这次只有一段课程的视频下载,没有yutobe那些了)

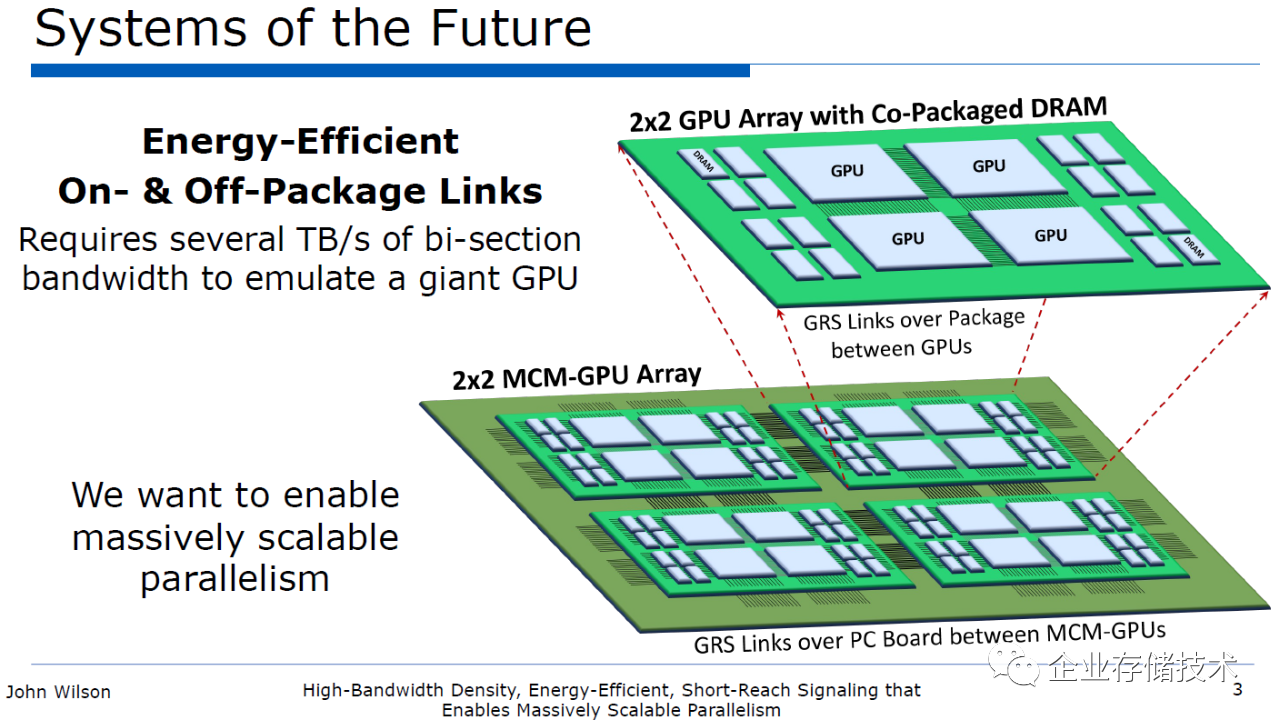

Intel和AMD看上去没讲啥新东西,反而是NVIDIA分享的《High-Bandwidth Density, Energy-Efficient, Short-Reach Signaling that Enables Massively Scalable Parallelism》,里面有些未来的东西,我从中只截选了下面几张图。

1个2x2的GPU阵列,应该就是NVIDIA未来的Chiplet,在GPUDie之间可达数TB/s的带宽。把4颗这样的MCM-GPU封装芯片放在一块电路板上,就是未来的DGX模块吧?总共包含有16个GPU Die。

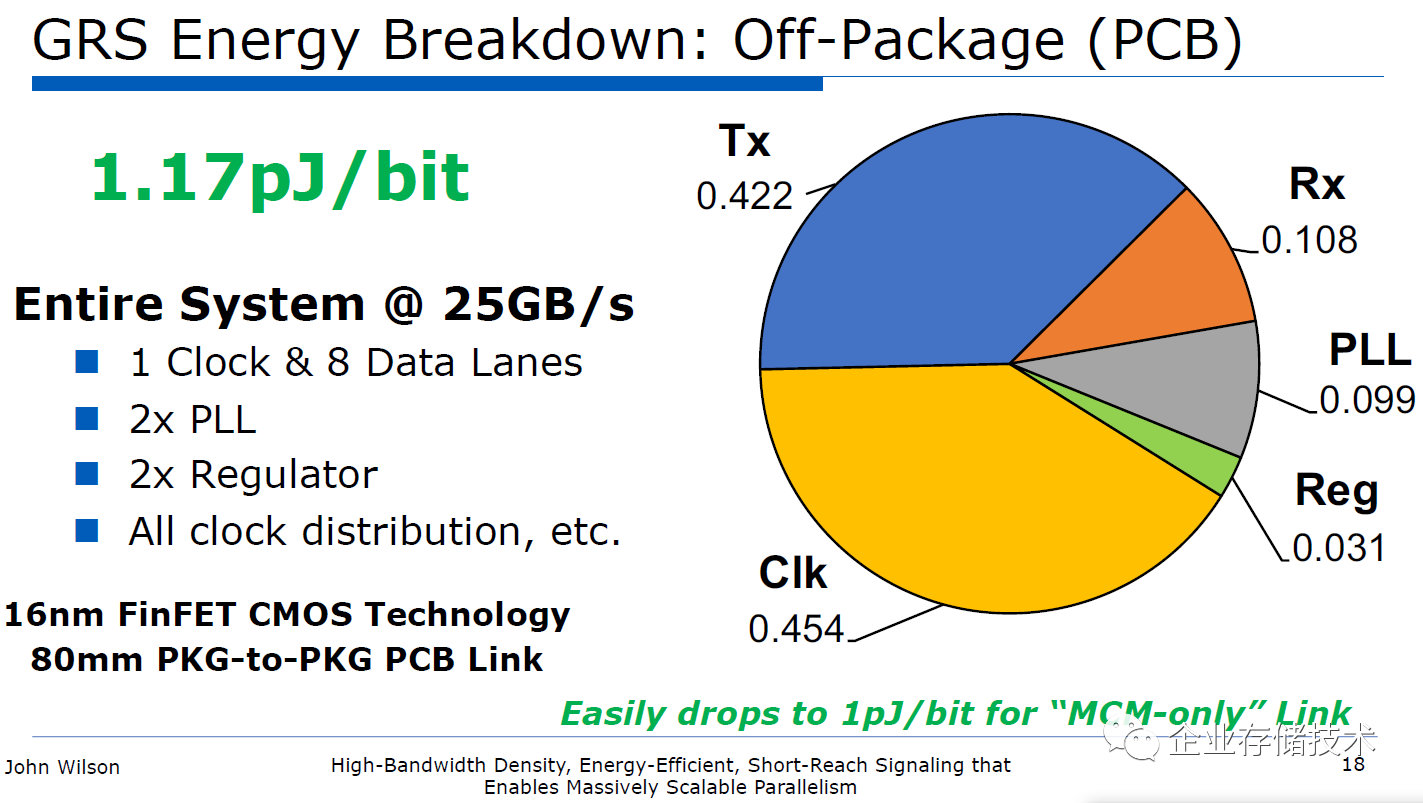

无论是在GPU Packgae封装上,还是走在PCB板上的GPU封装间互连,应该用的都是GRS Links。那为什么下图中写着:由8条Data lane组成的 Off-Package带宽,只有25GB/s呢?

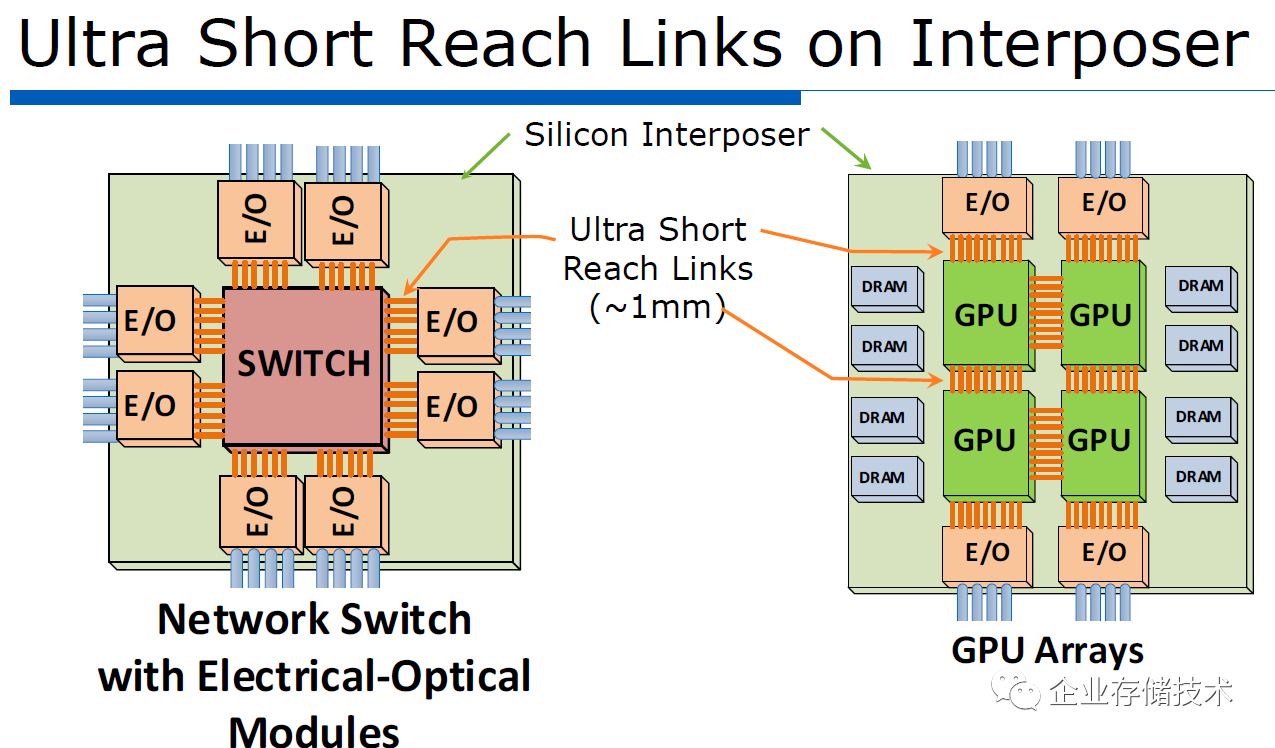

大家留意到了吗?这个Die间距只有大约1mm,超短线能降低片上互连热损耗,应该可以提高带宽吧。

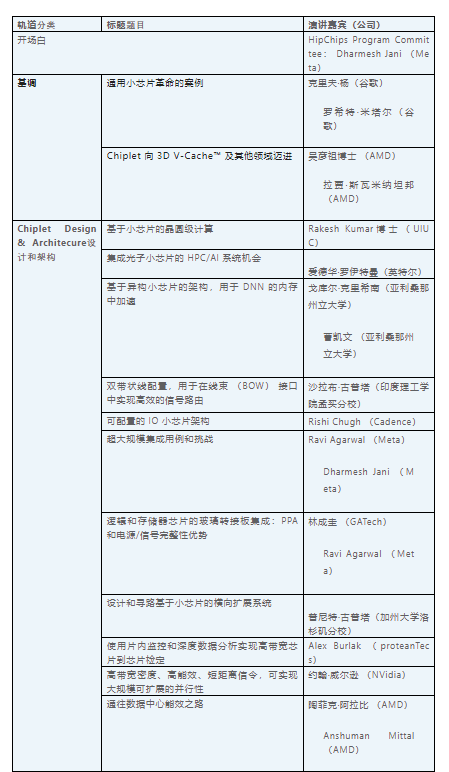

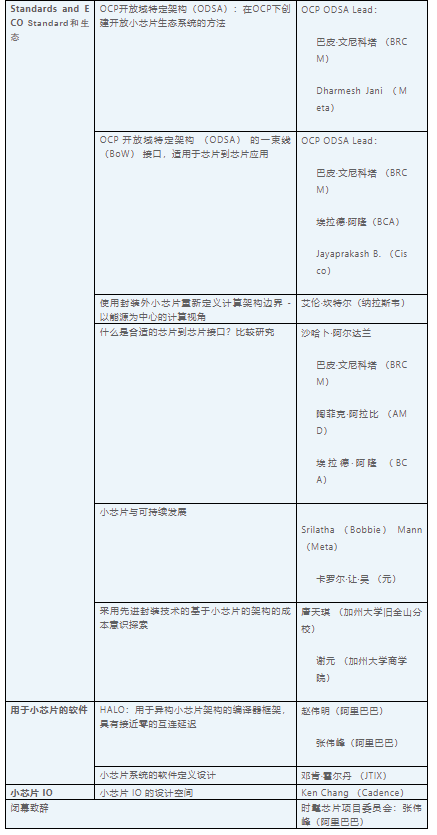

以下是我简单整理的演讲题目(官网是按时间顺序而不是按分类),可以看出主要的2大类话题:Chiplet Design & Architecure、Standards and ECO;软件和I/O这块相对还少一些。由于文档总数不多,我在pdf下载里反而没分目录。

希望对大家有帮助。

作者:唐僧 huangliang

原文:企业存储技术

推荐阅读

欢迎关注企业存储技术极术专栏, 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。