5. 物理层

5.1 介绍

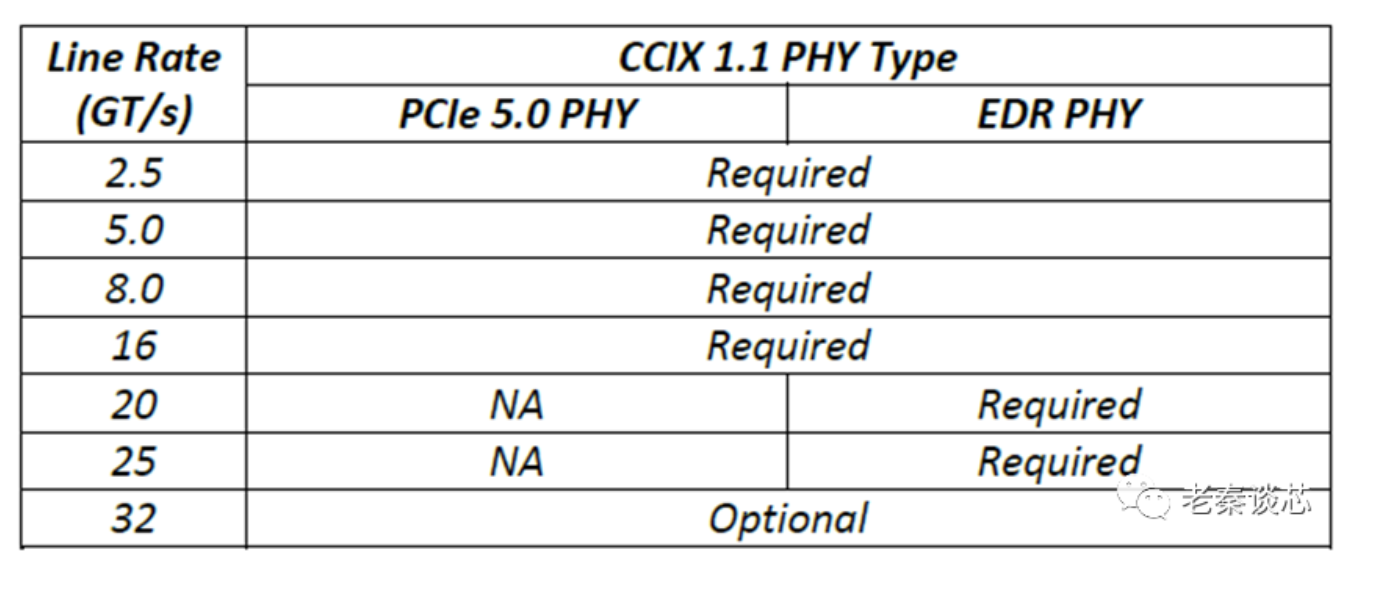

CCIX 1.1设备必须支持两种物理层中的一种:PCIe 5.0 PHY,或者是CCIX EDR PHY。

5.2 EDR25-SR电气规范

EDR25-SR电气规范适用于EDRPHY中ESM数据速率为20GT/s和25GT/s的短距离(Short Reach,SR)应用。

5.3 EDR25-LR电气规范

EDR25-LR电气规范适用于EDR PHY中ESM数据速率为20GT/s和25GT/s的长距离(Long Reach,LR)应用。

5.4 EDR32电气规范

EDR32电气规范适用于2.5 GT/s,5 GT/s,8 GT/s,16GT/s和32 GT/s。

6.协议层和传输层DVSEC(Designated Vendor-Specific Extended Capability)

6.1 概述

指定供应商特定扩展功能(DesignatedVendor-Specific Extended Capability,DVSEC)这个概念是PCIe协议里面的概念。

PCIe的供应商特定扩展功能是一种可选的扩展功能,允许由任何PCIe功能(Function)或RCRB(Root Complex Register Block)实现。这允许PCIe组件供应商使用扩展功能机制公开特定于供应商的寄存器。VSEC结构可以告诉供应商特定的软件,哪些软件具有特定的组件支持,包括软件发布后开发的组件。

每个PCIe设备在系统总线上都有自己的标识符,这个标识符就是BDF(Bus,Device,Function),PCIe的配置软件应当有能力识别整个PCIE总线系统的拓扑逻辑,以及其中的每一条总线(Bus),每一个设备(Device)和每一项功能(Function)。在BDF中,Bus Number占用8位,Device Number占用5位,FunctionNumber占用3位。PCIe总线最多支持256个子总线,每个子总线最多支持32个设备,每个设备最多支持8个功能。

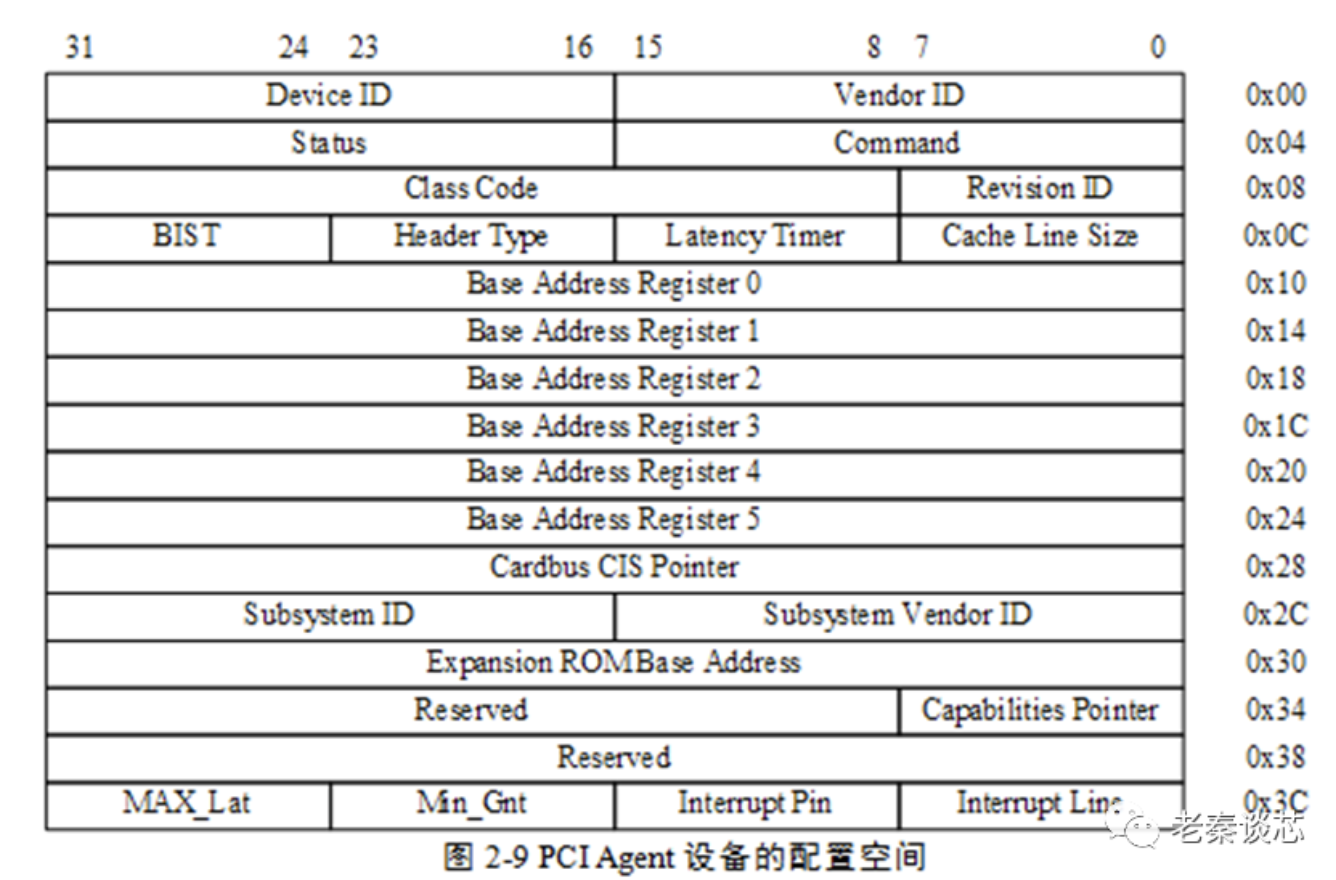

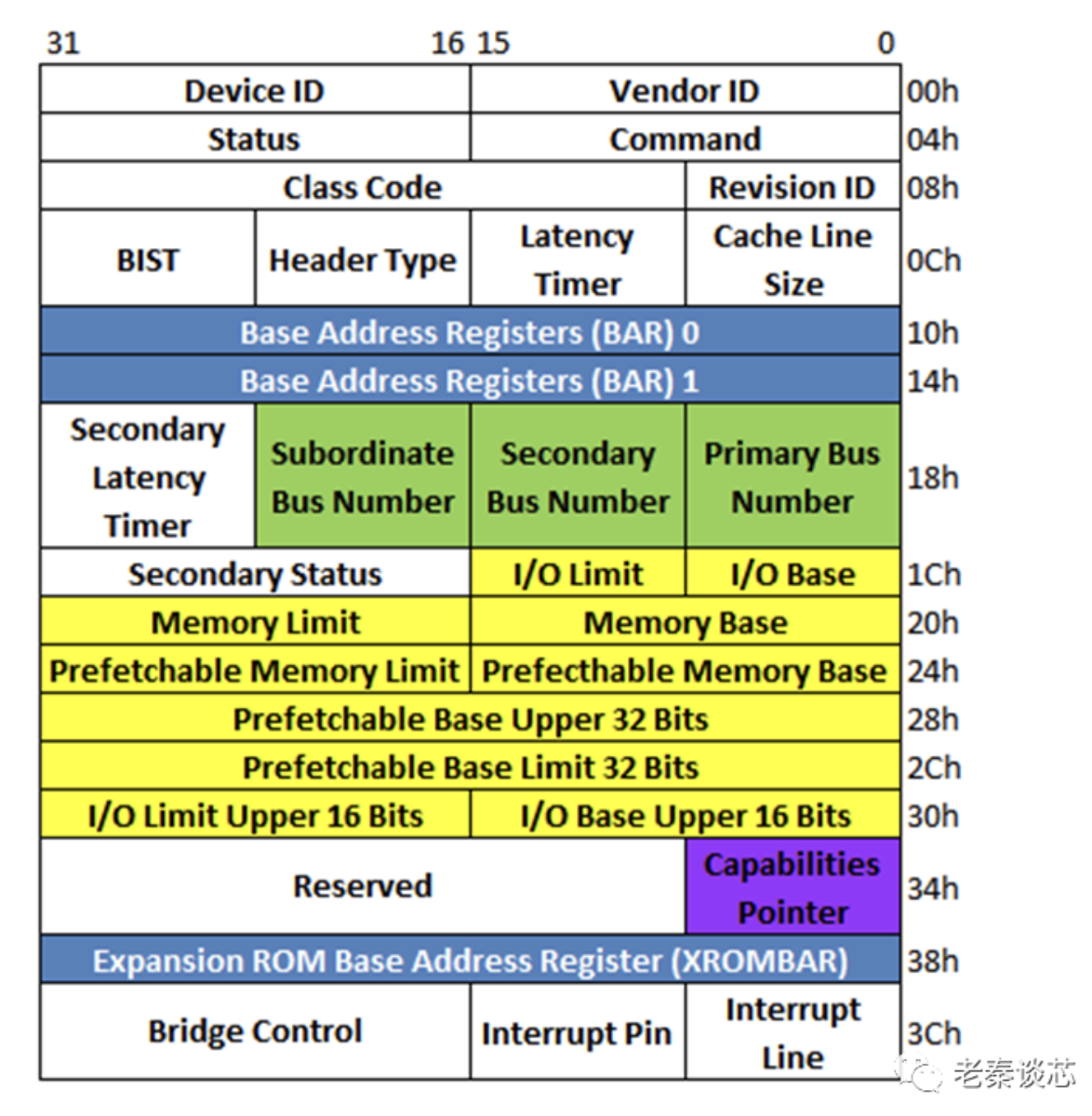

PCIe设备使用的基本配置空间共由64个字节组成,其地址范围为0x00~0x3F,这64个字节是所有PCIe设备必须支持的。此外,PCIe设备还扩展了0x40~0xFF这段配置空间,在这段空间主要存放一些与MSI或者MSI-X中断机制和电源管理相关的Capability结构。其中所有能够提交中断请求的PCIe设备,必须支持MSI或者MSI-XCapability结构。

PCIe设备还支持0x100~0xFFF这段扩展配置空间。PCIe设备使用的扩展配置空间最大为4KB,在PCIe总线的扩展配置空间中,存放PCIe设备所独有的一些Capability结构。

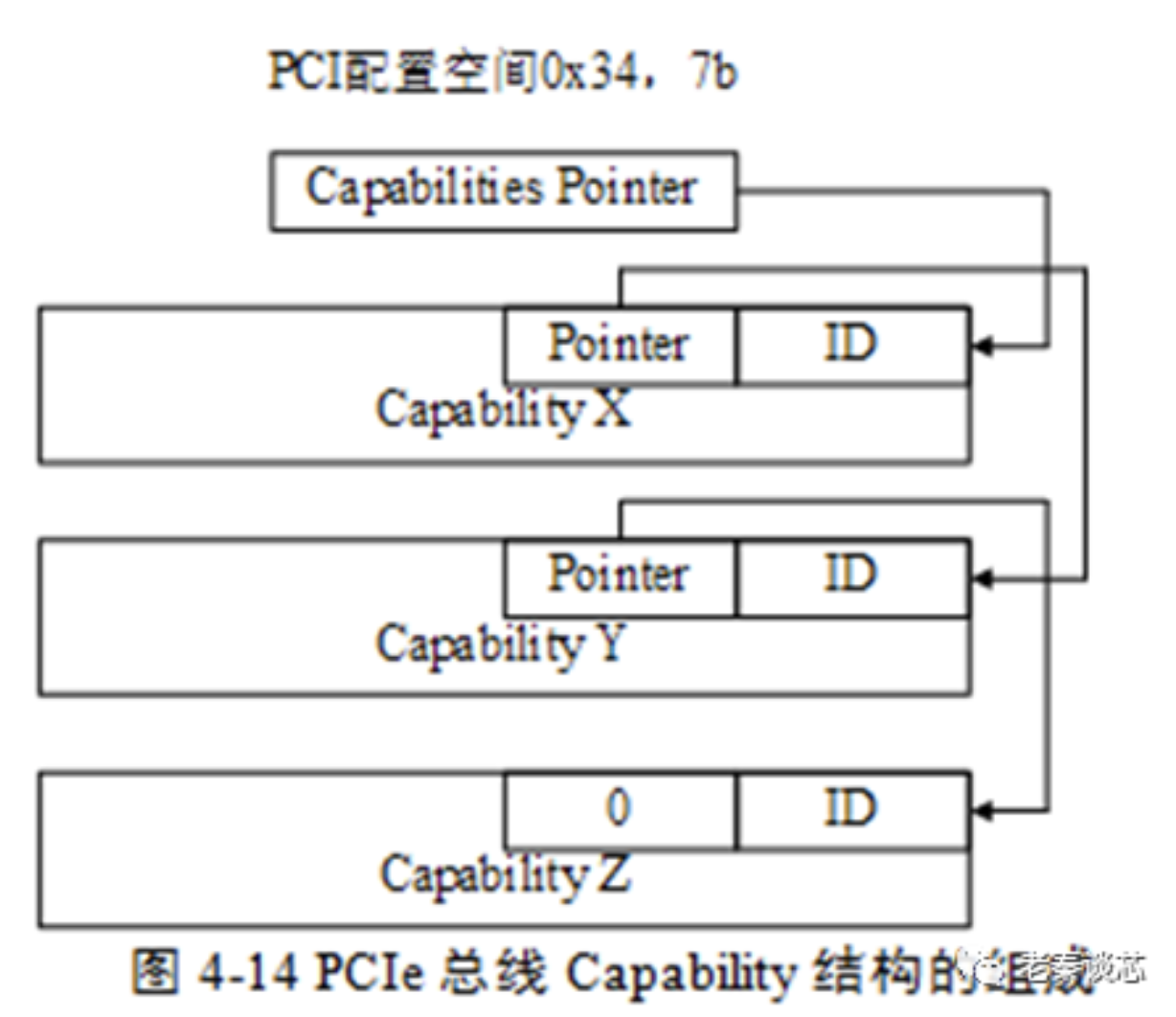

PCIe总线规范要求其设备必须支持Capabilities结构。在PCIe总线的基本配置空间中,包含一个Capabilities Pointer寄存器,上图的0x34,该寄存器存放Capabilities结构链表的头指针。在一个PCIe设备中,可能含有多个Capability结构,这些寄存器组成一个链表,其结构如下图所示。

其中每一个Capability结构都有唯一的ID号,每一个Capability寄存器都有一个指针,这个指针指向下一个Capability结构,从而组成一个单向链表结构,这个链表的最后一个Capability结构的指针为0。

一个PCIe设备可以包含多个Capability结构,包括与电源管理相关、与PCIe总线相关的结构、与中断请求相关的Capability结构、PCIe Capability结构和PCIe扩展的Capability结构。

PCIe每个Function都存在4K的配置空间,4K空间中前256 Byte(0x00 ~ 0xff)是与PCI兼容的寄存器。256 Byte的前64 Byte(0x00 ~0x3f)就是PCIHeader,可以分为Type0和Type1两种类型。配置空间中,除了PCIHeader,还存在很多描述PCIe相关能力的寄存器,这些寄存器在0x40 ~0xff中实现,这一段空间称为PCIe能力寄存器空间,此处可以由用户实施很多的PCIe能力,常见的有PM能力寄存器、MSI能力寄存器、PCIeCapability Structure(PCIe设备必须有)。

能力寄存器在PCIe Capability Register Space中以链表的形式分布。有一些PCIe扩展能力寄存器定义在配置空间的0x100 ~ 0xfff 段,即在PCIe Extend Configuration Space里。这里定义的各种扩展能力也是以链表的形式分布,只不过第一个扩展能力寄存器就在0x100位置。每一个扩展能力寄存器的第一排寄存器格式类似。

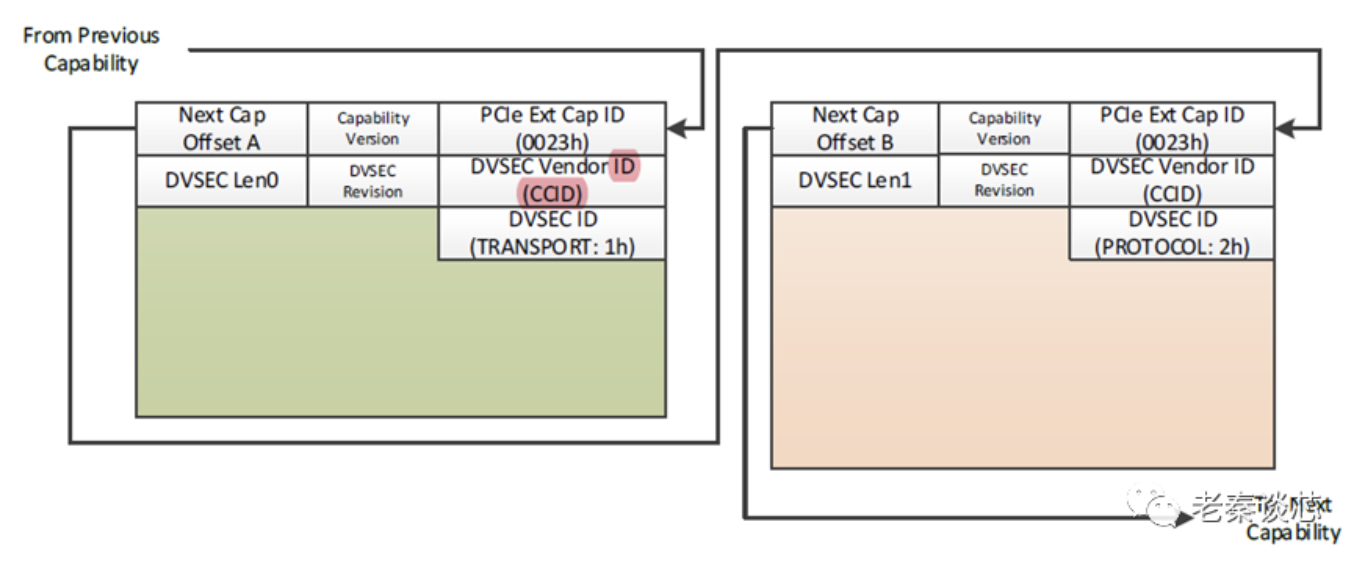

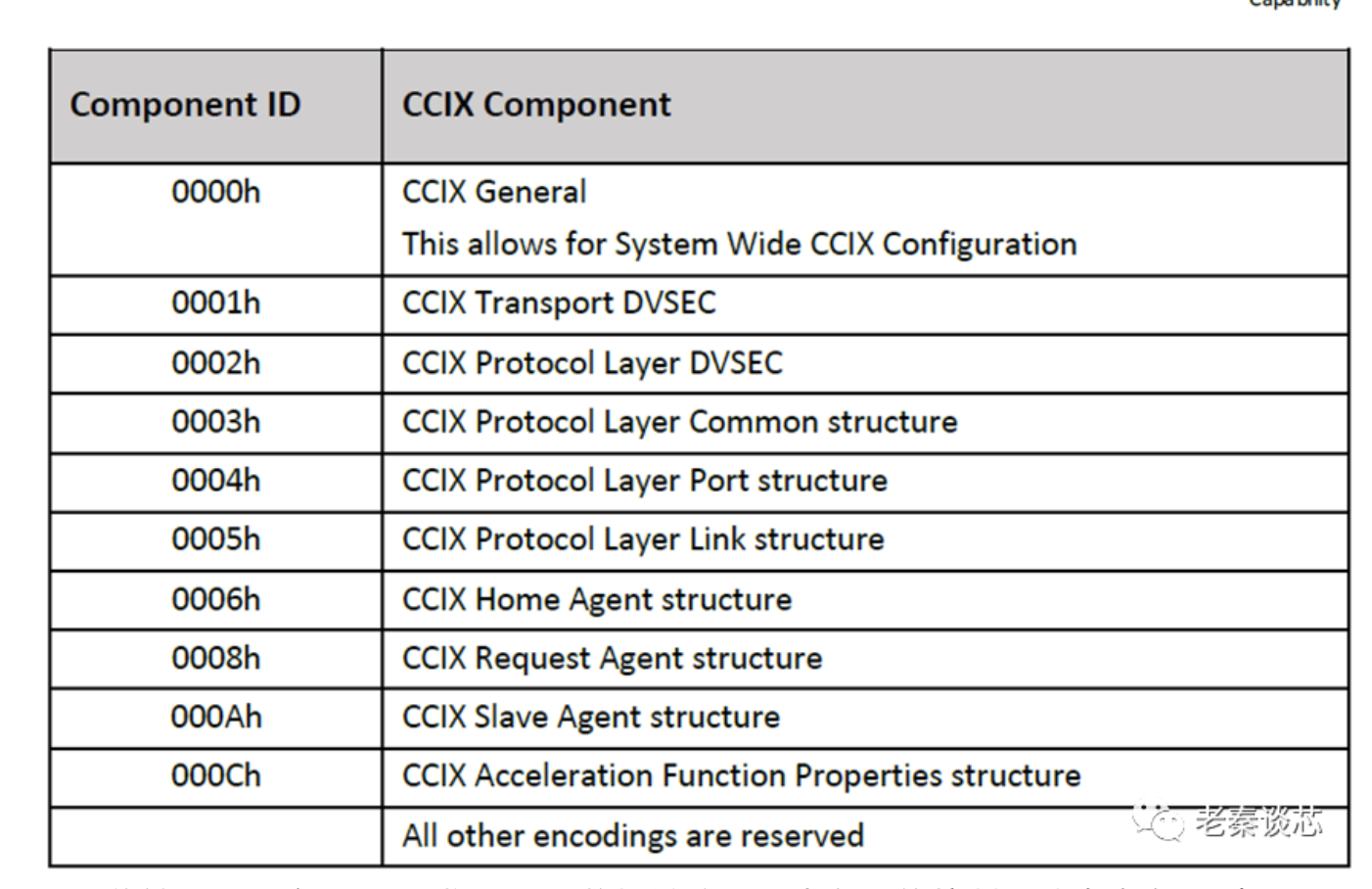

在CCIX中,对于DVSEC链表的没有特定顺序的要求。功能版本(capabilities version)必须为1h,与PCI Express基本规范中的定义一致。DVSEC版本必须为1h(对于此版本的CCIX规范)。DVSEC供应商ID必须是CCID。DVSEC ID编码必须符合下面表中的定义。

传输DVSEC包含CCIX物理层、数据链路层和事务层的控制和状态寄存器(Control and Status Register,CSR)。协议DVSEC包含CCIX协议层的CSR。

这一章里面定义了大量的寄存器,用以扩展CCIX的功能。由于寄存器实在太多了,本文中就不一一列举了。这一章也是整个CCIX协议里面篇幅最大的章节。做IP实现的需要仔细研读这一章。

老秦谈芯

老秦谈芯

推荐阅读

CPU设计之Cache -- MSHR

浅谈中断验证(一)

CCIX(七)

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。