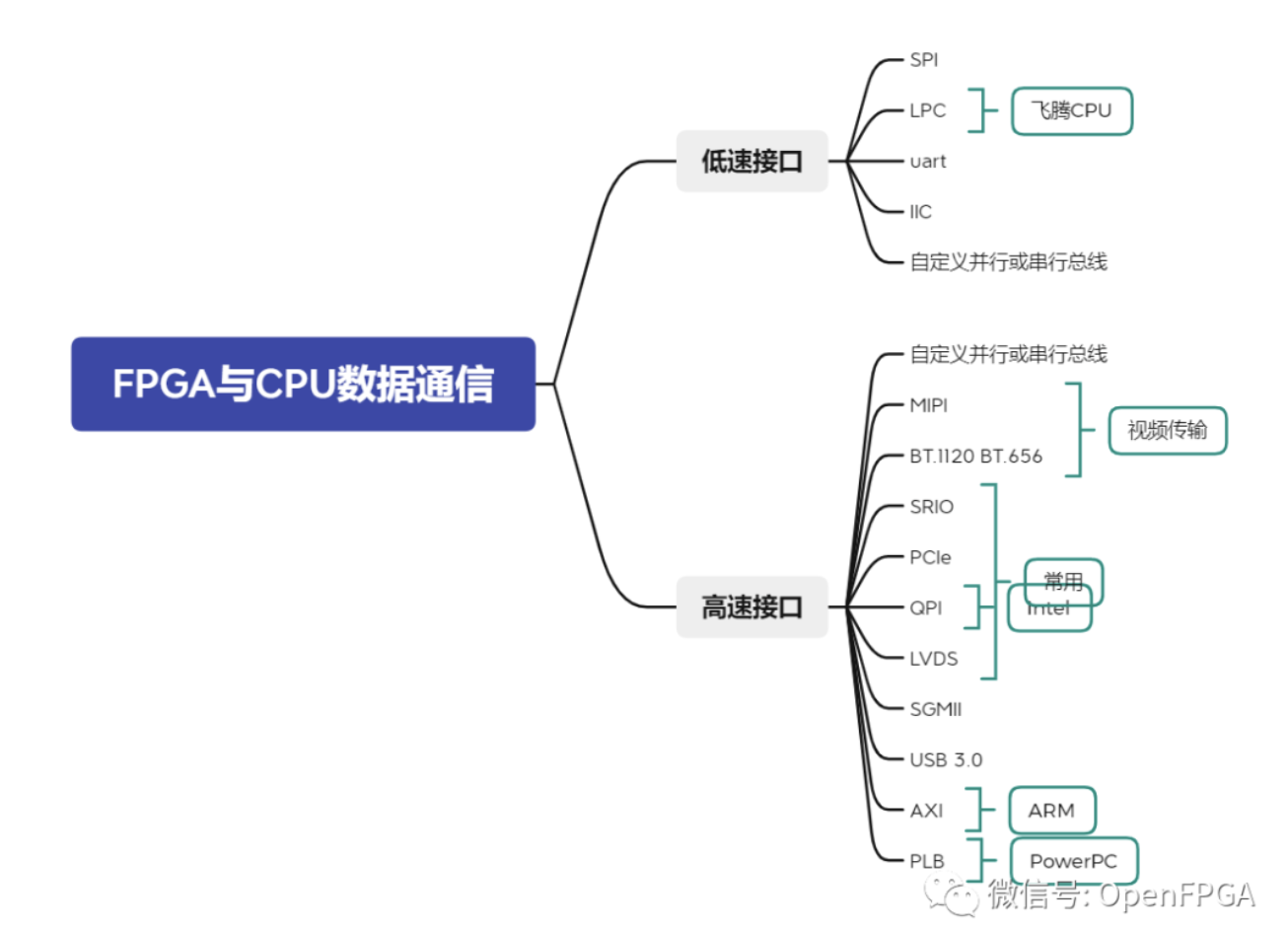

在进行FPGA设计时候,除了一些算法\验证等应用,其他情况下都需要FPGA和控制器进行数据交互(通信)。

通用一点说,所有CPU的数字通信接口都可以和FPGA进行通信,在这里我们将相关接口简单分类,这里的接口主要指板间通信,像422、485之类的就不展开描述(协议层都是uart)。

低速接口

低速接口时单片机常用的接口,在和FPGA对接时候主要进行小数据量的通信。

低速接口的优点就是简单,易于实现;缺点也是显而易见,就是通信带宽不高,无法进行大数据量通信。

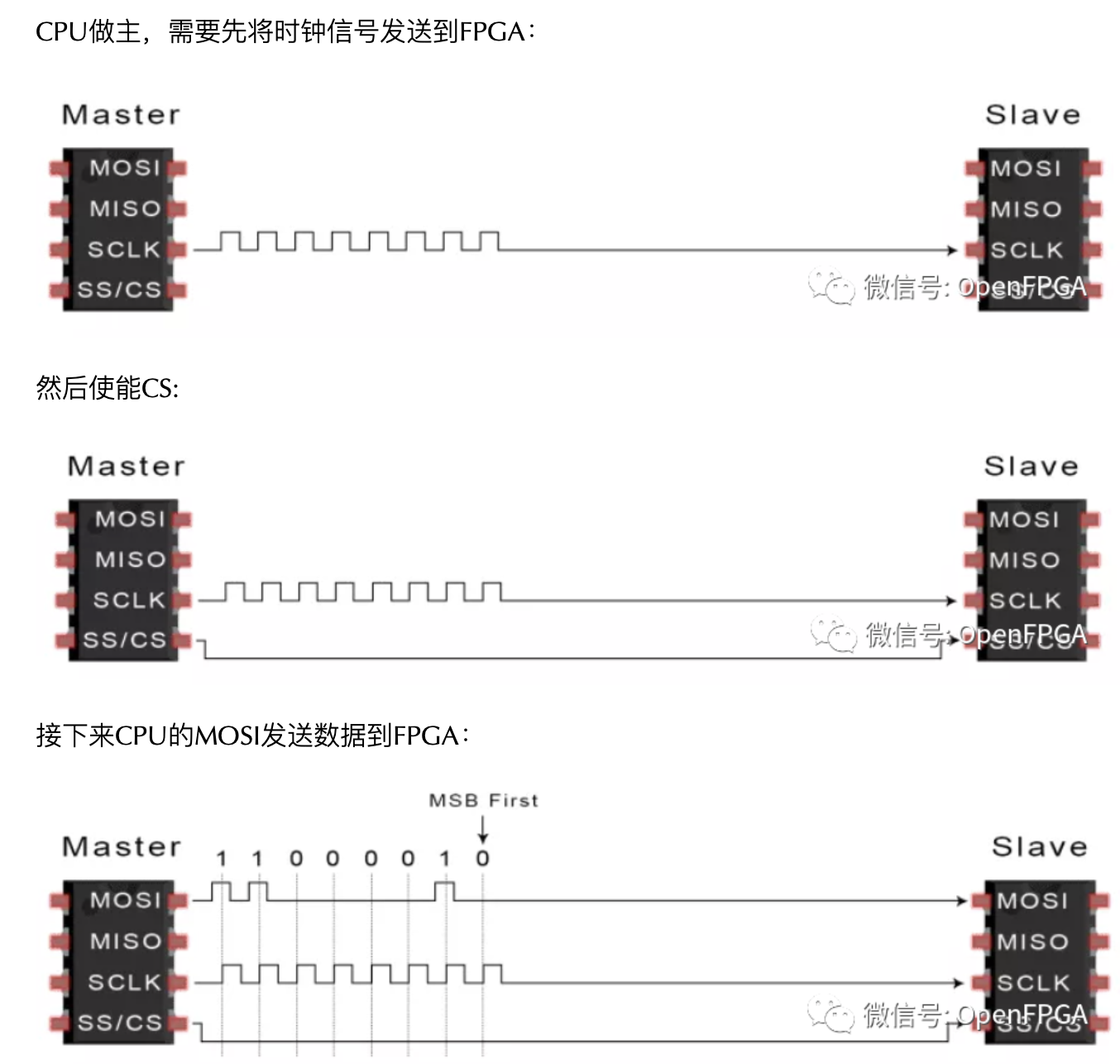

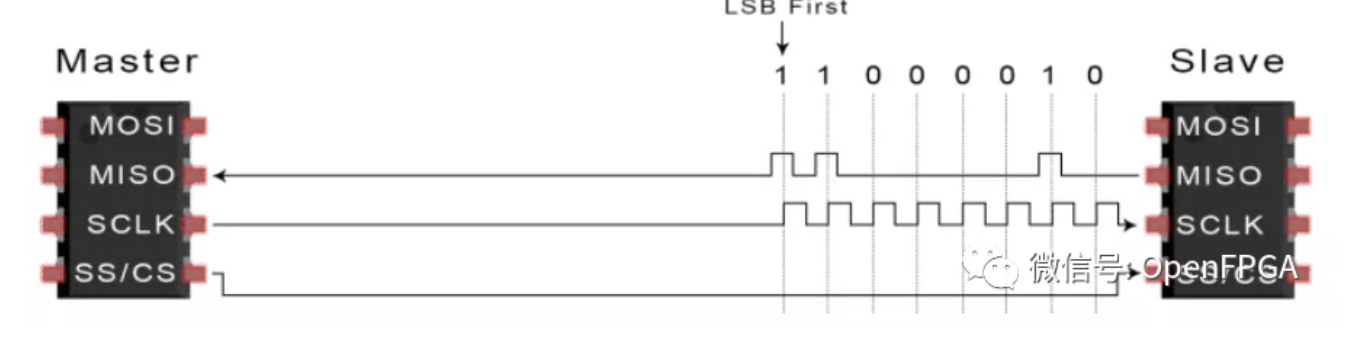

这里就简单说下SPI和UART,其中SPI是一种同步通信协议,UART是异步通信协议,区别就是有没有共享时钟信号。

这两个协议的使用可以参考下面的通信方式:假设FPGA和CPU之间进行通信,FPGA需要将XADC采集的电压电流传输给CPU做健康管理,这里由两点需要注意:一是传输不需要实时;二是数据量不大,所以选择低速接口较合适,选择SPI和UART时候传输的区别如下:

SPI接口:

FPGA的MISO需要反馈数据时候,同步的将数据反馈给CPU,如果MOSI不发送数据,则MISO也不能主动发送数据。

UART接口

对于UART就比较好理解了,CPU和FPGA协定好波特率,FPGA想要发送数据时候就将数据发给CPU即可(CPU需要利用中断触发接受数据)。

LPC

最后简单说下LPC(Low Pin Count),LPC常见的是在X86体系里常见的接口,主要用在南桥和EC之间通信(想想当年设计的笔记本还是挺虐的~),EC控制的矩阵键盘等通过LPC发送给南桥。

目前我应用的比较多的是和FT CPU之间进行通信,这方面用的比较少就不过多介绍了。

低速接口实现

关于这几个协议的实现,可以看下下面的文章,其中UART中详细介绍了RS232和UART区别。

接下来就是高速接口

高速接口

FPGA中通过Serdes可以实现大部分高速接口。常见的就是PCIe和SRIO,在ZYNQ中还有AXI非常常用。

对于PowerPC则可以使用PLB;Intel最新的FPGA则QPI也是比较常用的。

对于传输视频:MIPI、BT.656、BT.1120这些接口也是非常常见的。

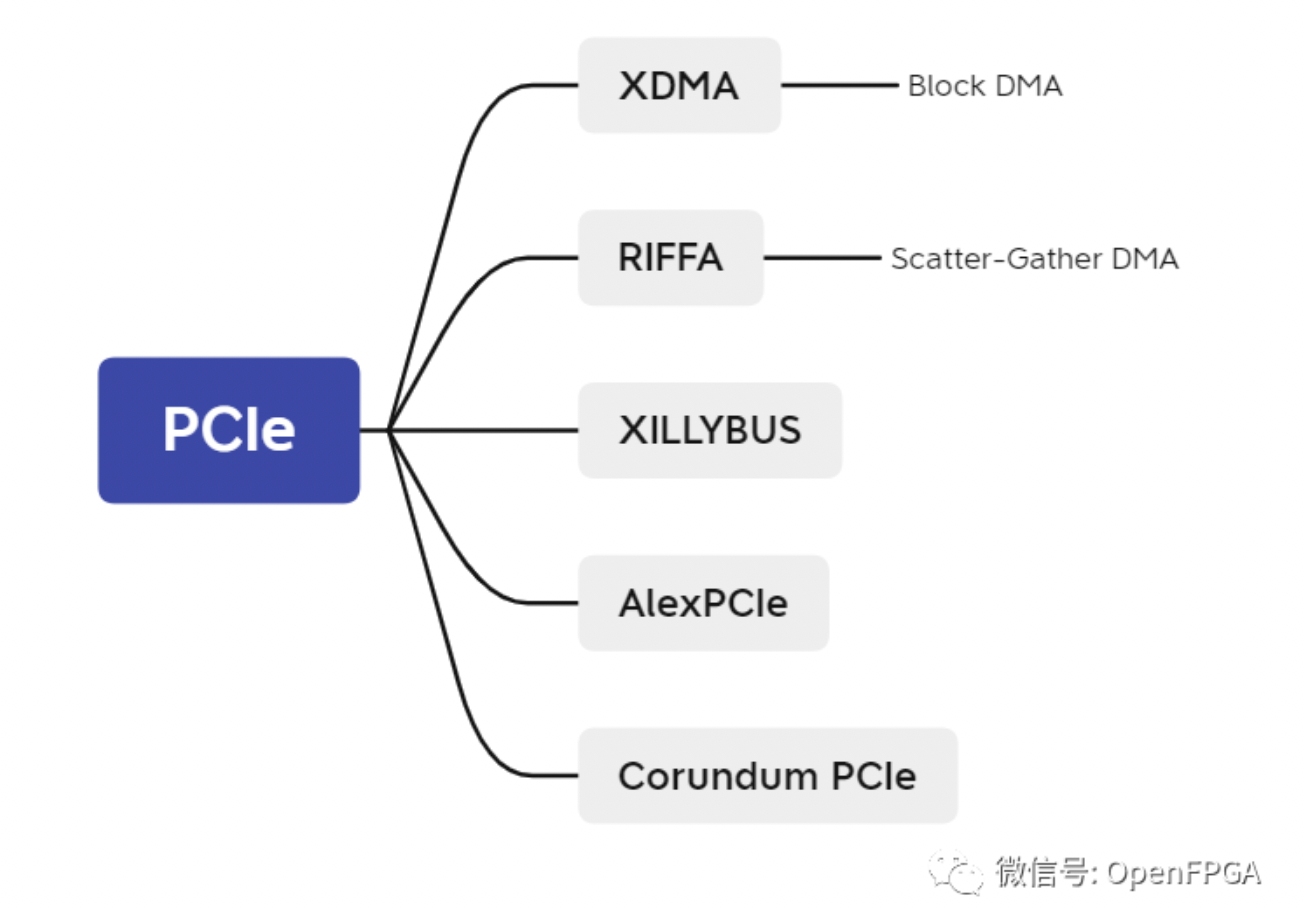

高速接口我们只介绍PCIe,这也是非常常见的数据通信接口,在加速卡、数据中心,都是核心。

PCIe的难点在于整体架构和CPU端的驱动,目前用于PCIe架构常用的就是DMA,至于原因,就不分析了,反正就是优势非常明显。

大家对于PCIe还处于“恐慌”的状态,但是大家不必担心,下面给大家介绍几个常用的架构:

上面的基于PCIe的项目,都是非常成熟的架构,也是目前能在FPGA流行PCIe接口的主要原因,其中这些架构都在很多工程中得到应用。

RIFFA和Alex的可以查看下面文章介绍:

优秀的 Verilog/FPGA开源项目介绍(一)-PCIe通信

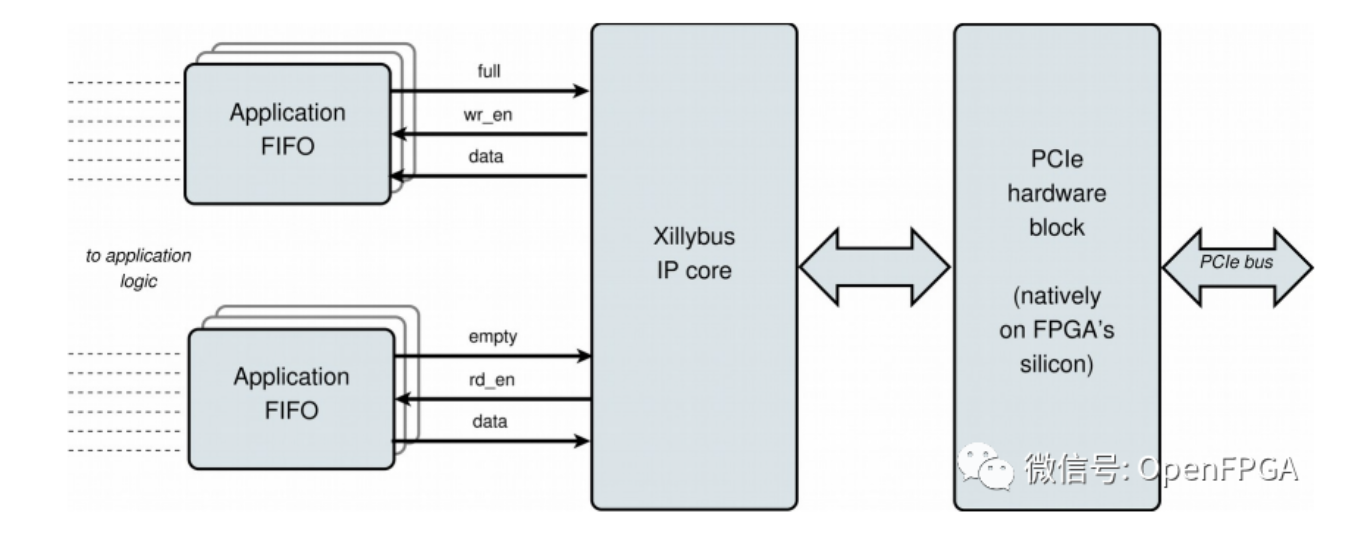

下面是XILLYBUS的架构:

官方网址:

http://xillybus.com/

Corundum可以查看下面文章:业界第一个真正意义上开源100 Gbps NIC Corundum介绍

总结

上面的介绍只有一部分常用接口,还有其他很多不常用的总线,像FSB总线、HT总线、DMI总线等,也是可以实现CPU和FPGA之间通信。

今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

- AD936x+ZYNQ搭建收音机(一)

- MII2RGMII IP核使用设计举例

- 优秀的 Verilog/FPGA开源项目介绍(三十一)- OFDM

- HDBaseT是什么协议?与SDI和HDMI比较有哪些区别?

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。