本例程将 PS 的 ETH1 通过 EMIO 方式引出, 通过 EMIO 引出的 ETH 为 GMII 接口, 将其与 GMII toRGMII IP 核连接后转换成 RGMII 接口,然后与外部子卡中的 88E1512 芯片连接。在 PS 端通过 SDK 自带的 lwip echo server 例程通过子卡,以 RJ45 电口与 PC 机实现 TCP 网络通信。

8.5.9.1应用背景

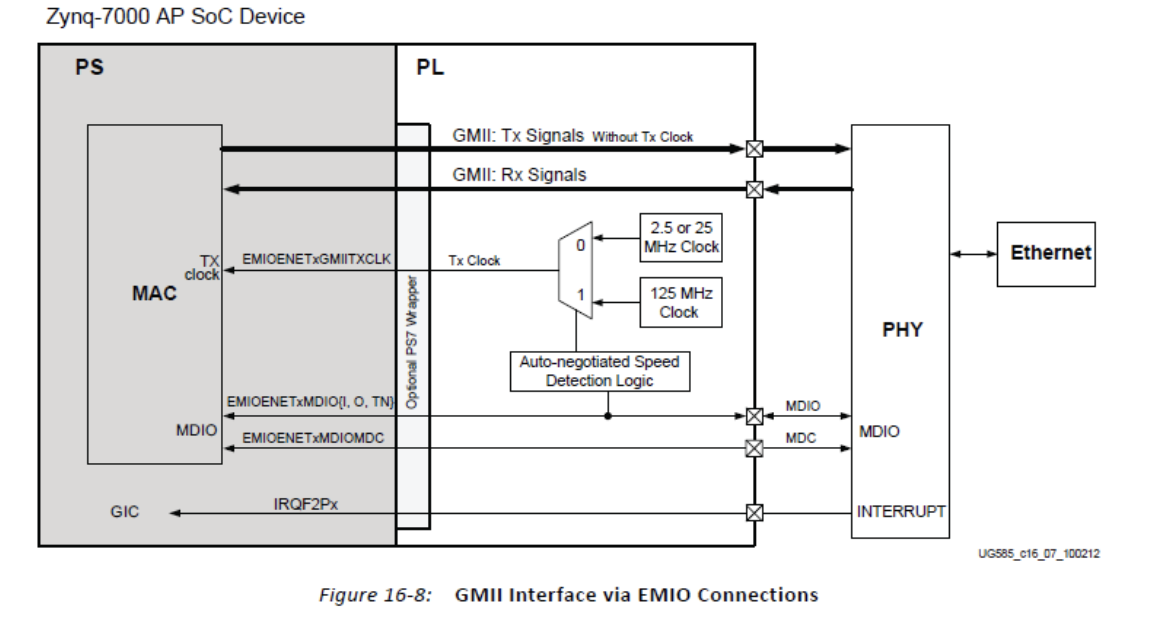

在使用ZYNQ系列芯片时,使用PS端的ETH 通过 EMIO 引出后为标准的 GMII 接口, 如下图所示。

图8‑188PS端的ETH 通过 EMIO 引出

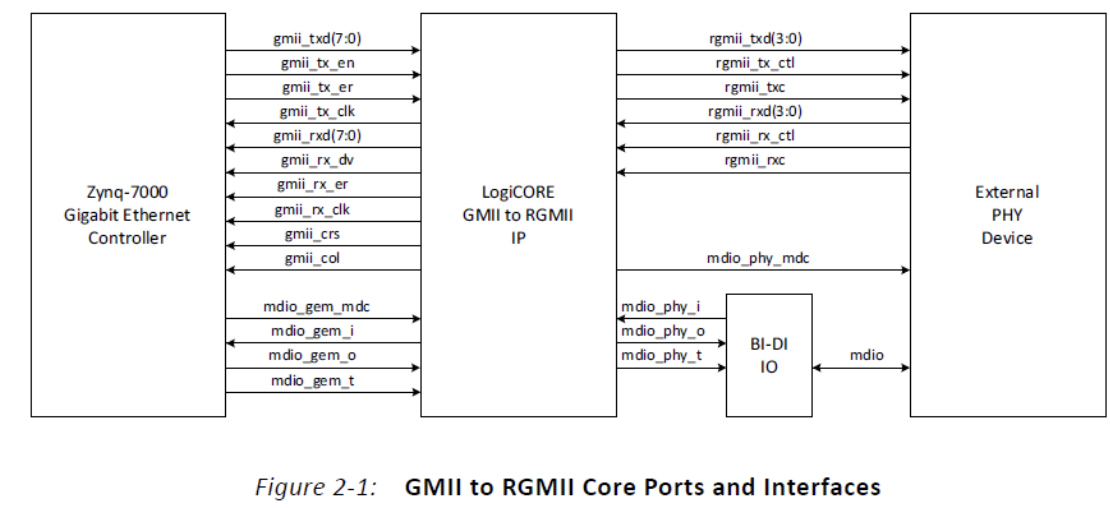

或者某些IP在使用时出来的接口就是标准的GMII接口,而目前常用的千兆PHY都是使用RGMIi接口,所以为了使用外部PHY,需要通过 IP 核 GMII to RGMII 将 GMII 接口转换为 RGMII 接口,才能与 PHY 芯片连接。连接原理如下图所示。

图8‑189GMII to RGMII连接原理

8.5.9.2外部PHY时序

这部分参考《8.5.1RGMII PHY接口设计、8.5.2PHY_MDIO 接口设计》。

8.5.9.3 GMII_to_RGMII原理

这个IP的详细解释可以参考官方数据手册,这里简单介绍一下实现原理。

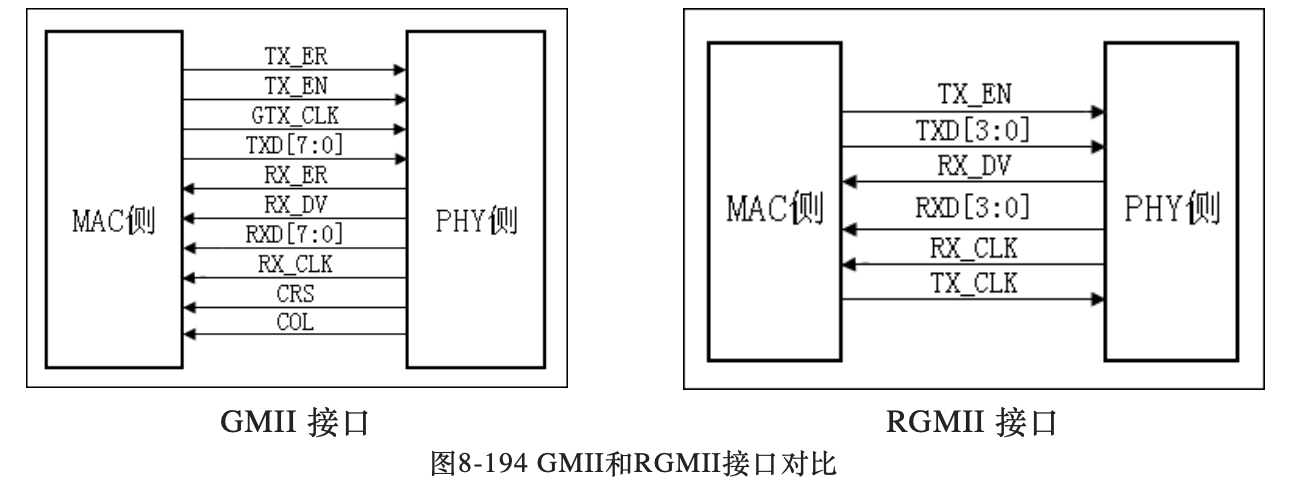

图8‑194GMII和RGMII接口对比

|

RGMII 接口是 GMII 接口的简化版, 在时钟的上升沿及下降沿都采样数据, 上升沿发送TXD[3:0]/RXD[3:0],下降沿发送 TXD[7:4]/RXD[7:4], TX\_EN 传送 TX\_EN(上升沿)和 TX\_ER(下降沿)两种信息, RX\_DV 传送 RX\_DV(上升沿)和 RX\_ER(下降沿)两种信息。

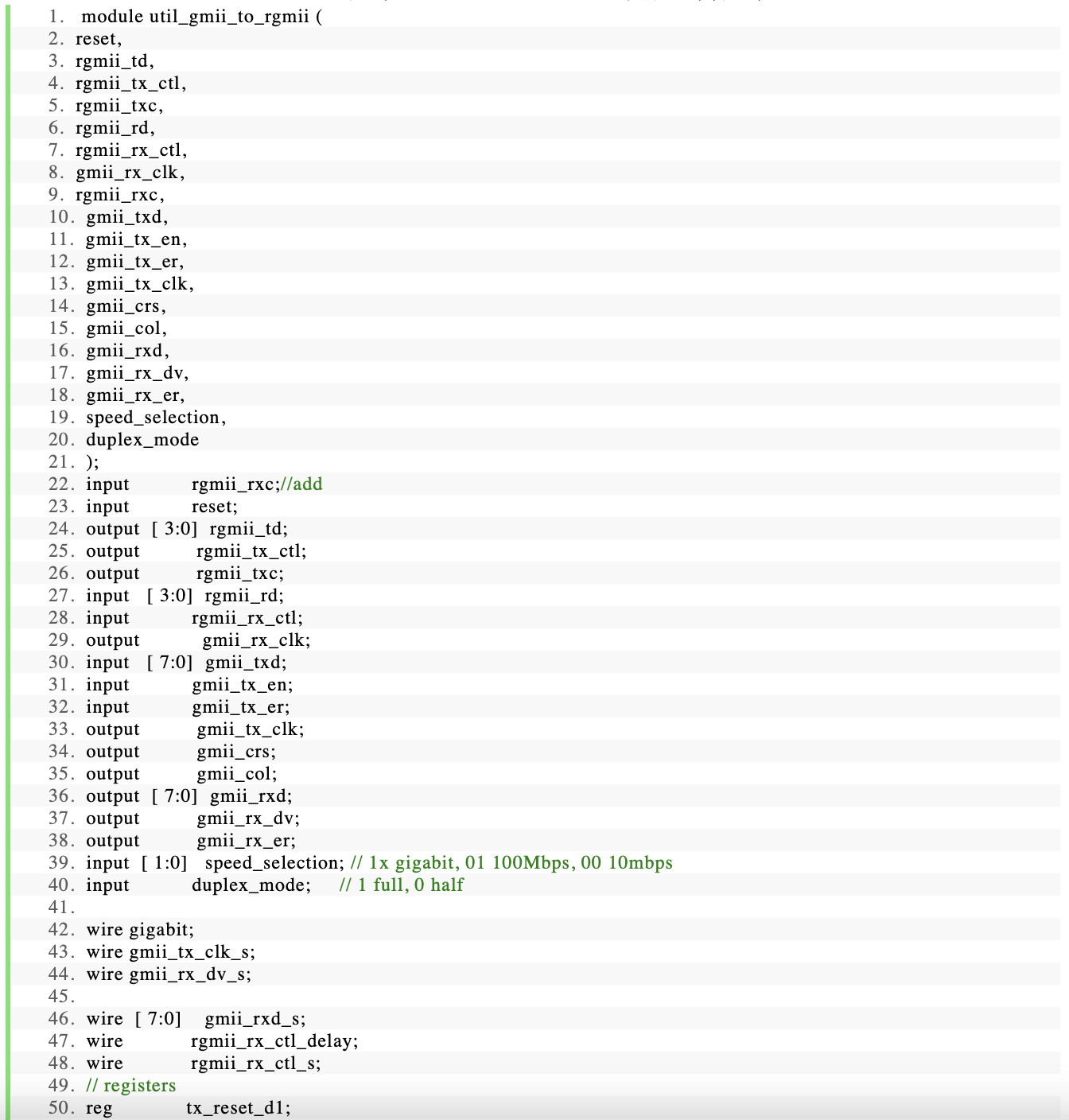

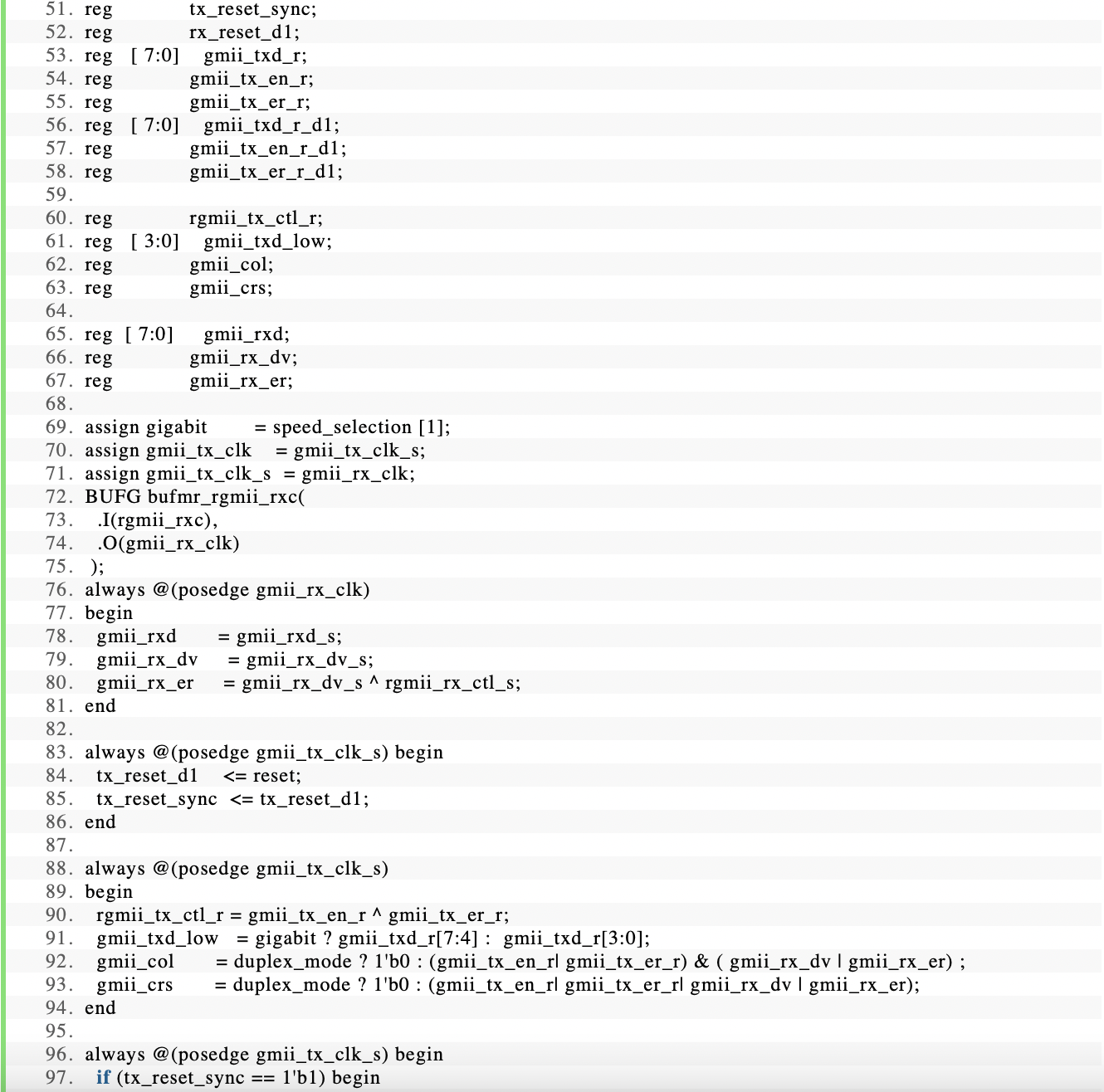

代码8‑13GMIItoRGMIIIP实现示例代码

上述只是示例代码(来源AlteraIPCore)实现,主要是利用原语实现双边沿接收和发送。

8.5.9.4PL设计

按照图8‑189可以很简单的进行PL部分设计,主要就涉及到两个IP,分别是PS的IP核和GMII_to_RGMIIIP。

完成后的Block如下:

图8‑190GMII_to_RGMII IP应用Block

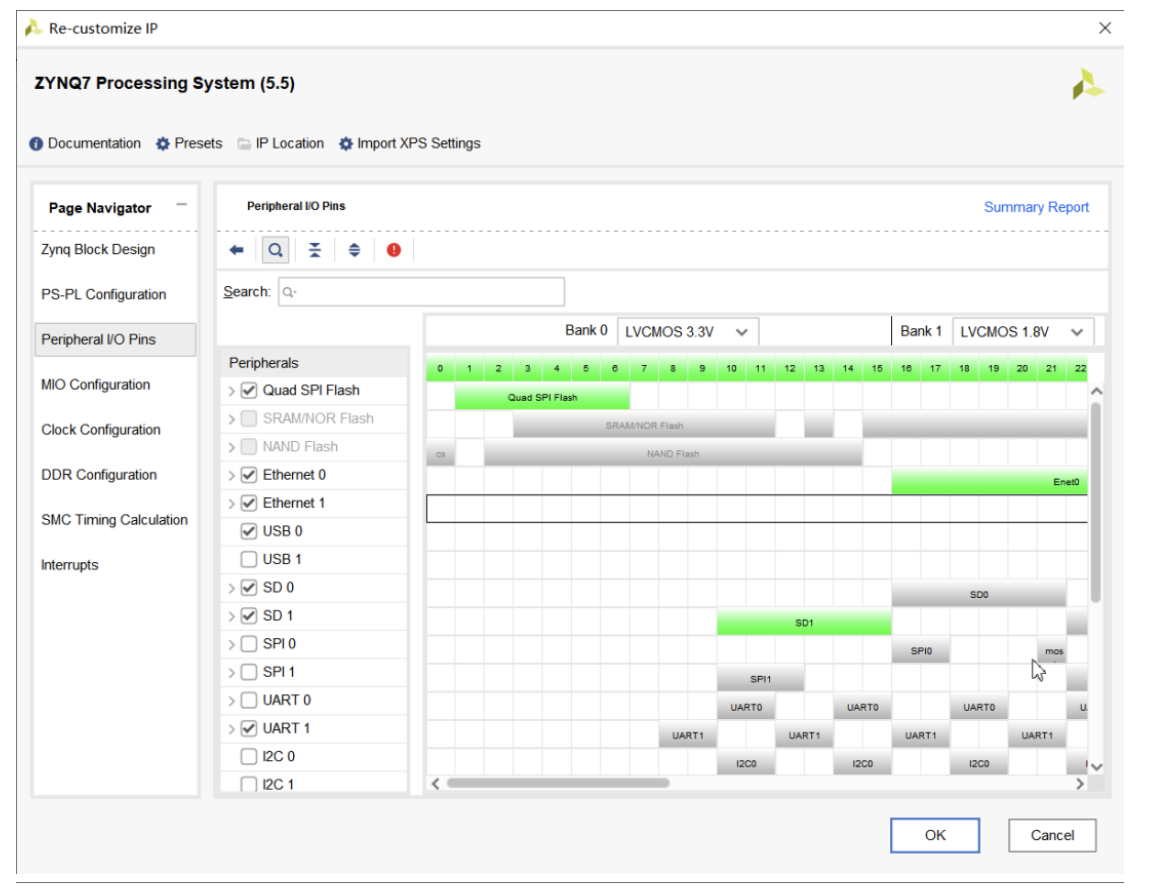

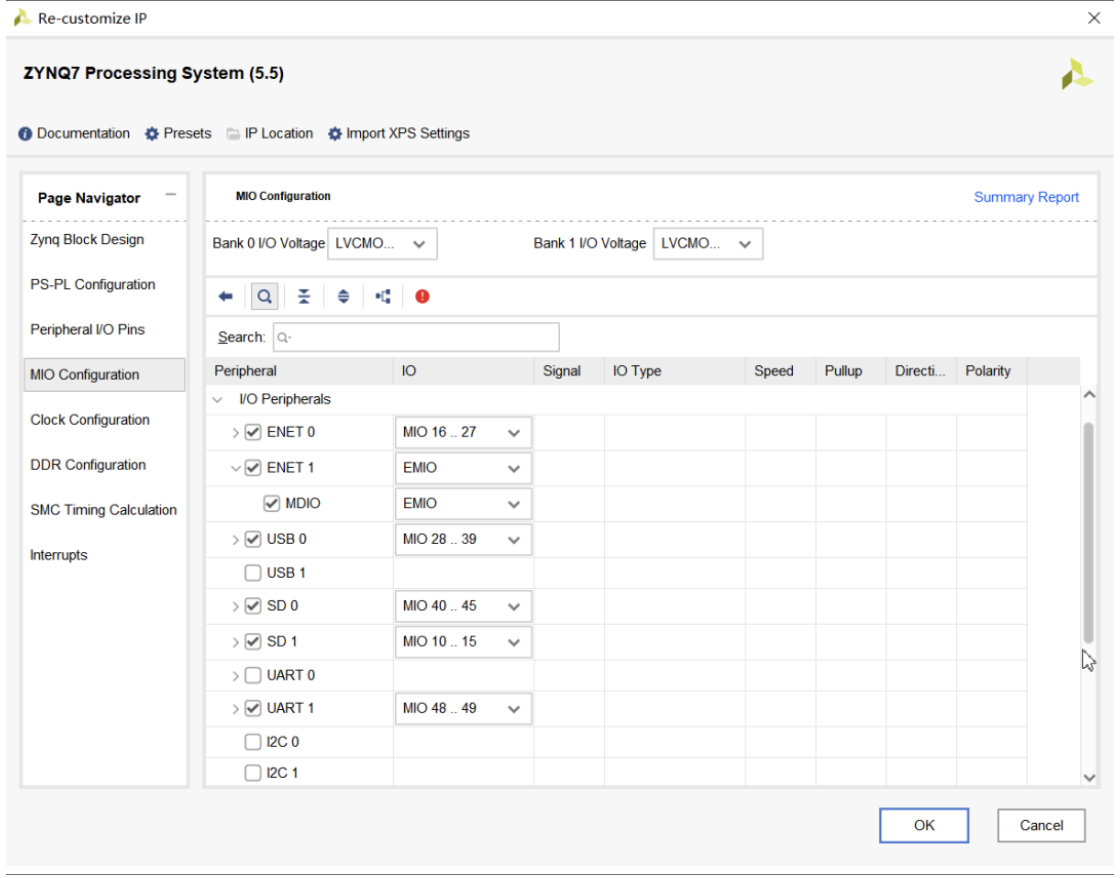

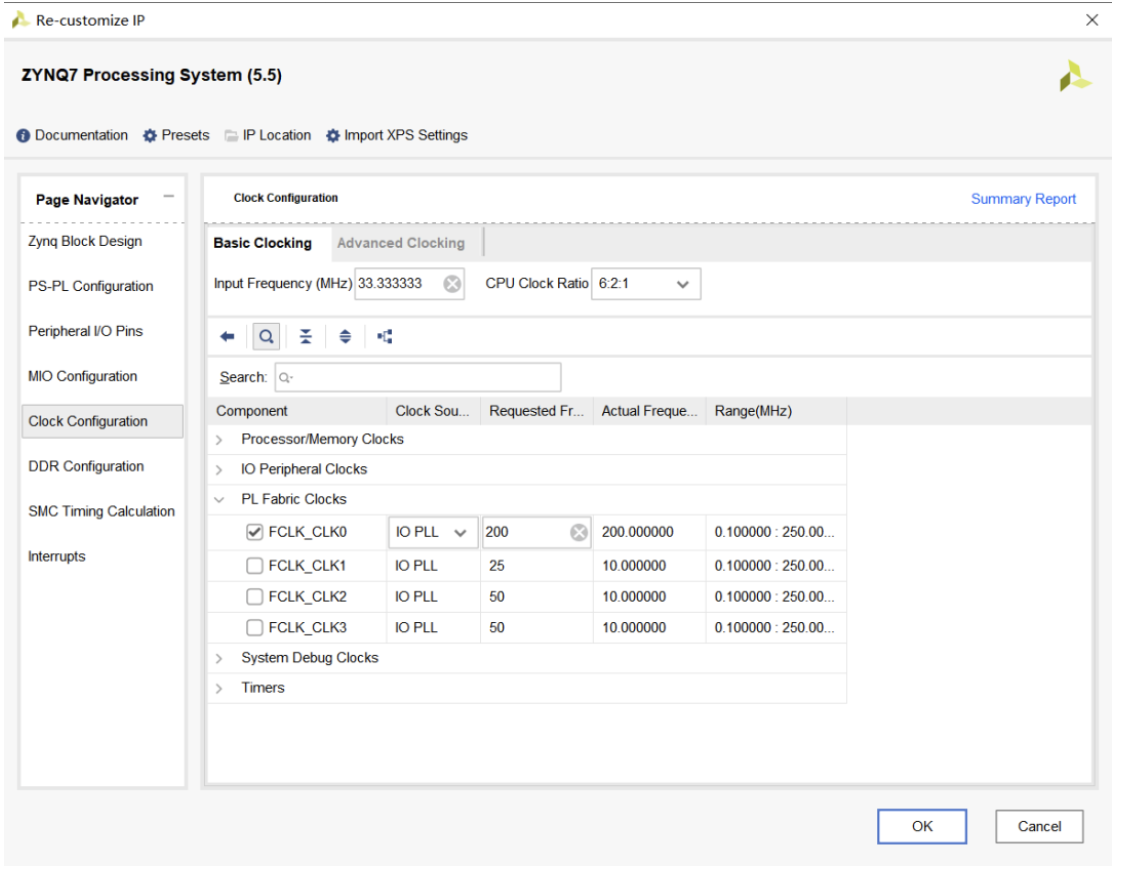

1、ZYNQ PS 设置

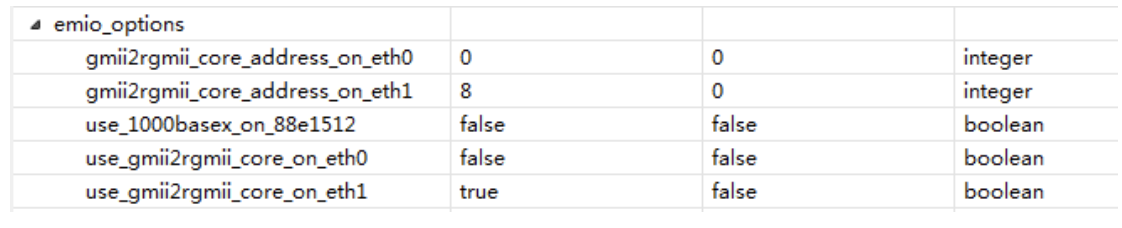

将 ETH1 及其MDIO 通过 EMIO 引出,将 FCLK_CLK0 设置为 200M,作为 GMII to RGMII IP 核内部IDELAYCTRL 的参考时钟, FCLK_RESET0_N 通过 Utility Vector Logic 生成的非门后作为 GMII to RGMIIIP 核的复位信号。如下图所示:

图8‑191PS设置

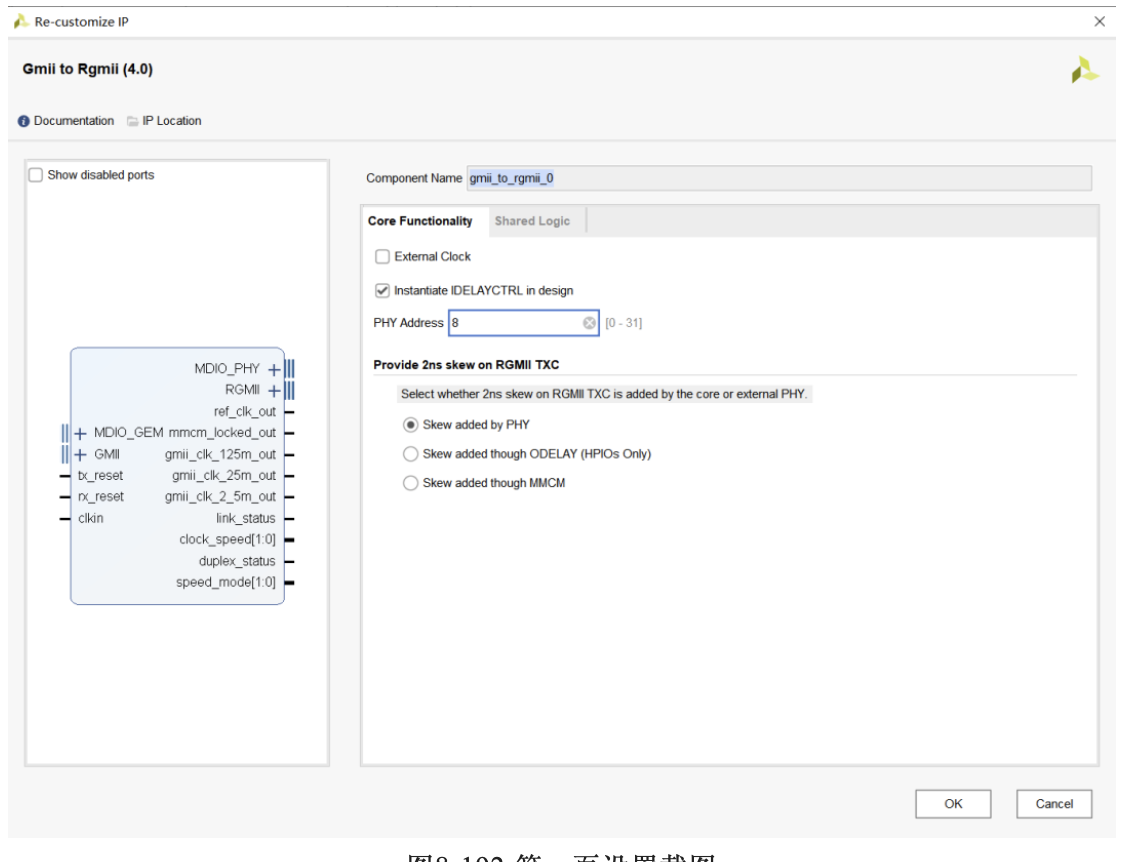

2、gmii—_to_rgmiiIP设置

第一页设置

图8‑192第一页设置截图

将 IP 核的 PHY address 设置为 6(该值可任意设置,但不能与外部的 PHY address 相同,否则将产生冲突使 IP 核工作异常)。

IP 核中 RGMII 接口的接收数据信号和控制信号需要通过 IDELAYE2 来调整信号输入延时,使其时序满足建立和保持时间约束。因此需要在 IP 核包含与IDELAYE2 相关的 IDELAYCTRL,用来校准 IDELAYE2 每个延时 tap 的延时值。本次设计的外部PHY 88E1512 发送信号延时由芯片内部提供,因此,选择 2ns 的延时 skew 由 PHY 增加。

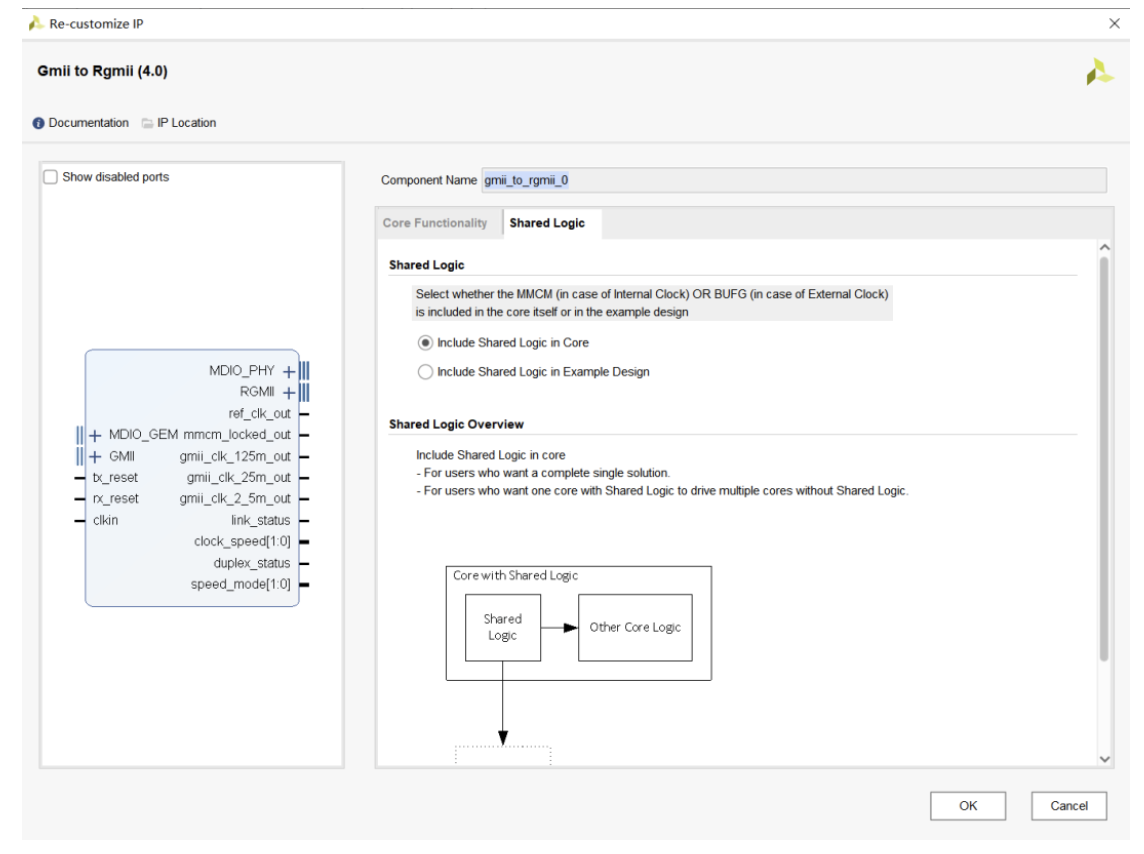

图8‑193第二页设置截图

选择 shared logic 包含在 IP 核内部。这部分介绍详见8.5.1RGMII PHY接口设计。

8.5.9.5时序约束

本例程中,时序约束主要是针对 RGMII 接口进行 input delay 和 output delay 的约束,以及IDELAYE2 延时 tap 数的设置,使 RGMII 接口的满足建立和保持时间的要求,从而达到时序收敛。

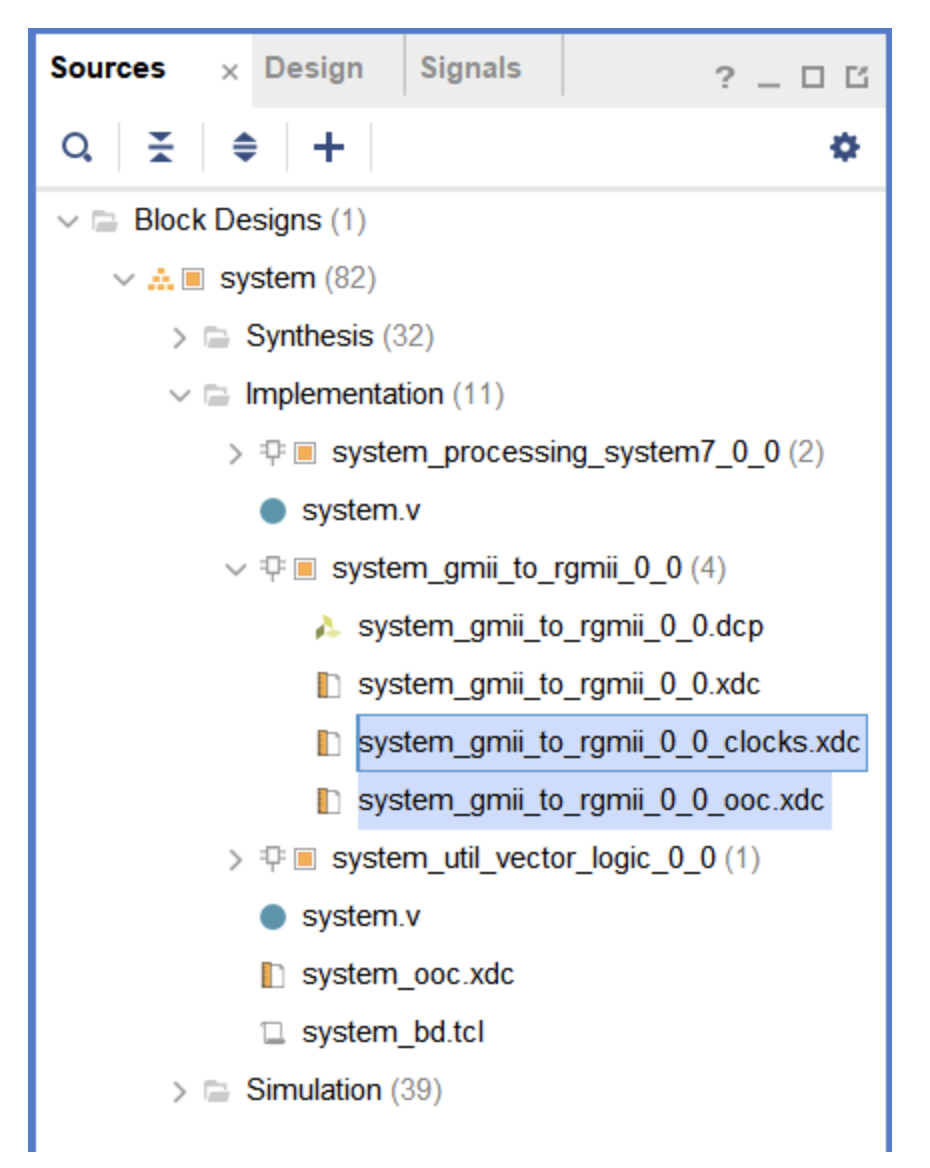

对 于 input delay 和 output delay 的 约 束 , GMII to RGMII IP 核 所 自 带 的system_gmii_to_rgmii_0_0_clocks.xdc 文件中已经包含了默认设置。对于 IDELAYE2 延时 tap 数的设置,在 system_gmii_to_rgmii_0_0.xdc 中包含了默认模板。这两个 xdc 文件位置如下图所示。

图8‑195XDC默认模板

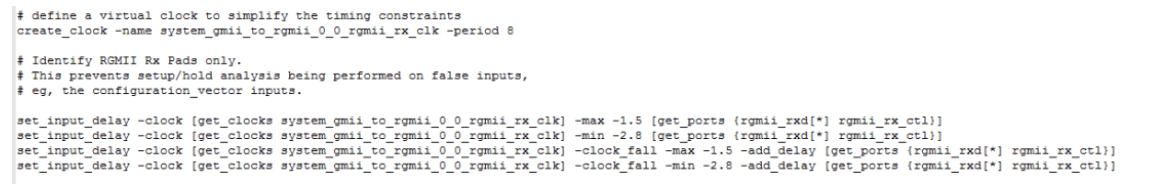

1、input delay 约束

system_gmii_to_rgmii_0_0_clocks.xdc 文件中, 关于 input delay 的约束如下所示。约束范围为:-1.5~-15.8ns。

按照上图中的 setup time 和 hold time, input delay 的-min 应该为-(4-1.2) =-15.8ns, -max应该为-1.2ns。显然, IP 核自带 input delay 的约束范围为-1.5ns~-15.8ns,比我们计算的结果-1.2ns~-15.8ns 略为宽松,用于 setup time 计算所需的-max 时间小了 0.3ns,为了保证时序严格收敛,需要将 system_gmii_to_rgmii_0_0_clocks.xdc 文件中 set_input_delay -max 的-1.5 全部改为-1.2。需要注意的是, 这些 xdc 文件由 IP 核自动生成,每次重新配置 IP 后, vivado 都会重新生成IP 的 output product, 因此会将被修改的 xdc 文件覆盖还原,需要手动重新再次修改 xdc 文件才行。

2、IDELAYE2 延时设置

在 GMII to RGMII 的 IP 核内部为 rgmii_rx_ctl 和 rgmii_rxd[3:0]端口都连接了 IDELAYE2 模块,用来为这些信号进入 PL 内部前引入额外的延时。IDELAYE2 延时值的大小与 xdc 中的 input delay 约束是否能收敛密切相关。一般情况下,当 input delay 约束的 setup time 出现违例,应该将 IDELAYE2的 tap 数减小,降低延时值;当 input delay 约束的 hold time 出现违例,应该将 IDELAYE2 的 tap数增大,增加延时值。

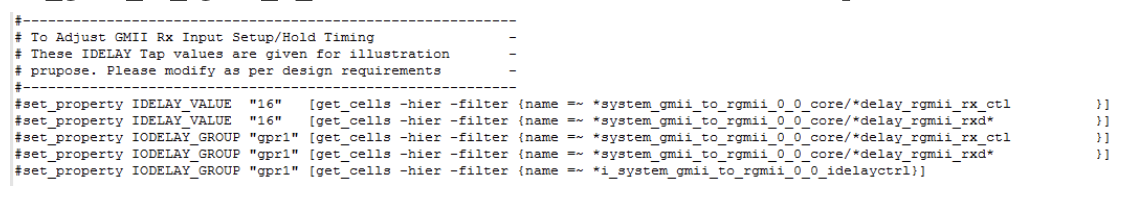

system_gmii_to_rgmii_0_0.xdc 中包含了设置 IDELAYE2 的 tap 数的模板,如下图所示。

该段约束默认是被注释的,默认的延时 tap 数为 16,我们可以将这段约束复制到工程自己新建的 xdc 文件中,编译工程后根据时序报告查看 input delay 是否时序收敛,若存在时序违例,则需要根据实际情况调整 tap 的值。

3、IO 口

IO口没什么特殊的,参看源文件即可。

8.5.9.6PS 程序设计

1、LWIP 库修改

参考上一篇文章《基于TCP/IP协议的电口通信》。

2、创建工程

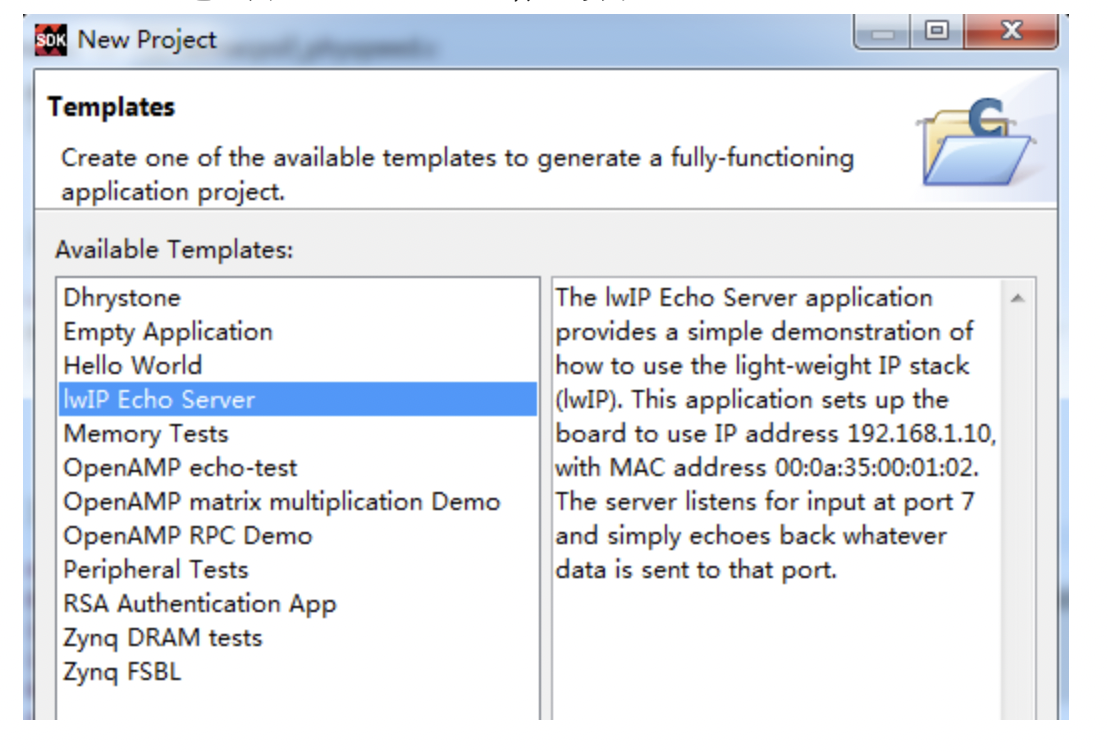

本例程使用了 SDK 自带的 lwip echo server 例程来验证子卡电口和光口的功能,因此在创建工程时选择LwIP Echo Server模板,如下图所示。该例程基于LWIP库在ARM中建立一个TCP Echo Server,IP 地址为 192.168.1.10, 端口号为 7

8.5.9.7程序测试

lwip 库设置

lwip 的设置如下图所示。

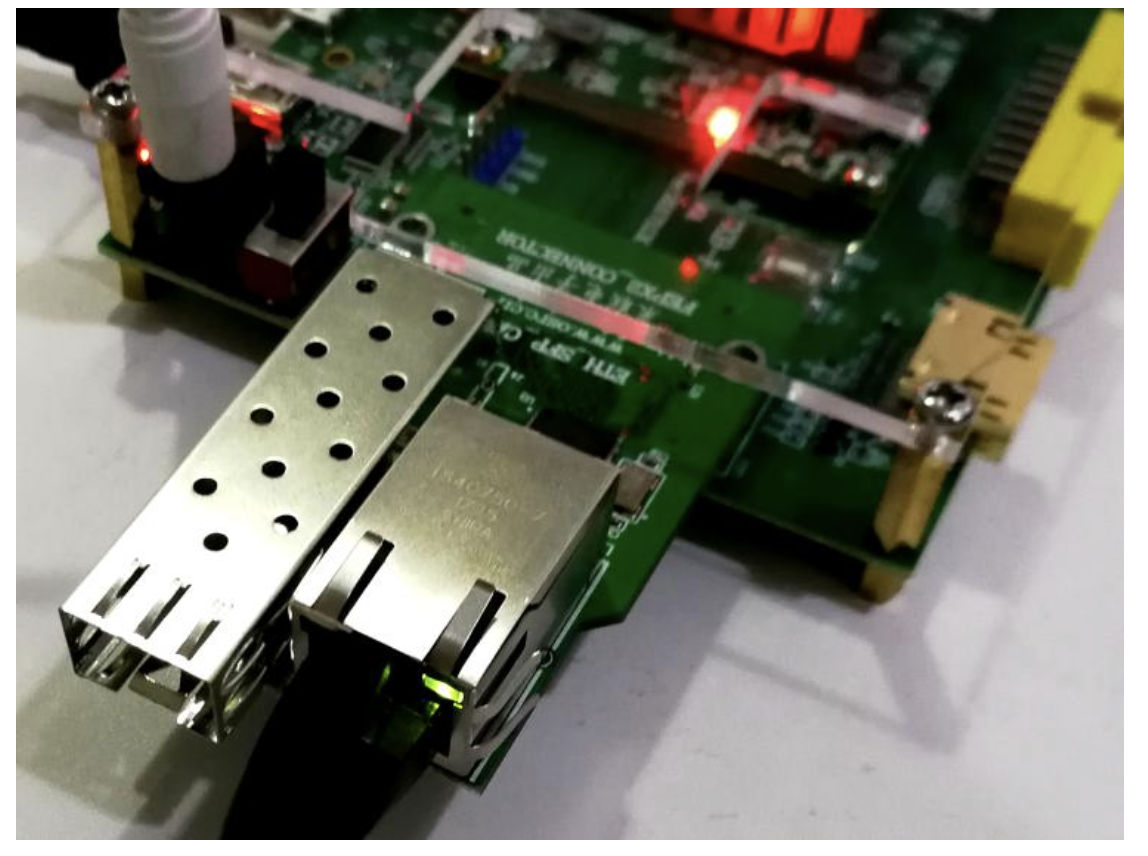

网络测试

将千兆网线插入子卡的 RJ45 座中,与电脑连接,将电脑的 ip 地址设为 192.168.1.100,子网掩码为 255.255.255.0。

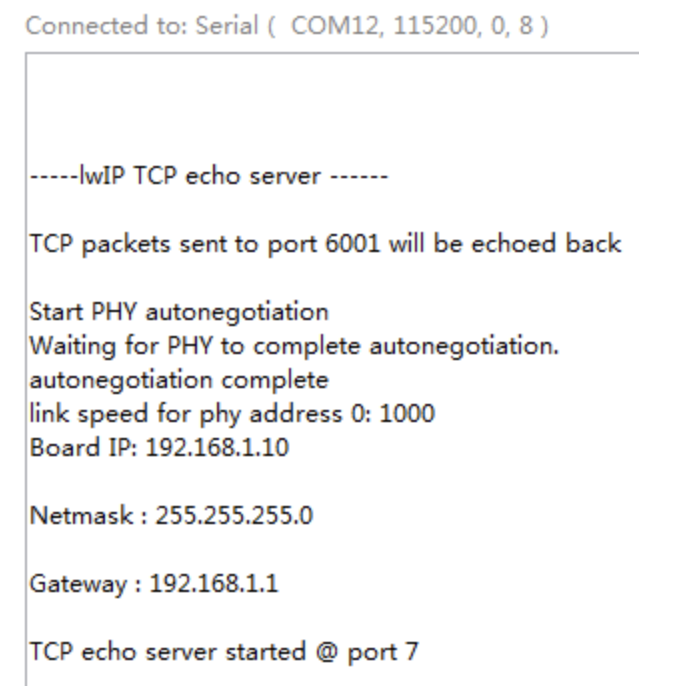

然后给开发板上电,通过 SDK 将程序下载入开发板后,观察 SDK 串口打印信息,如下图示所示。表示千兆网络连接正常。

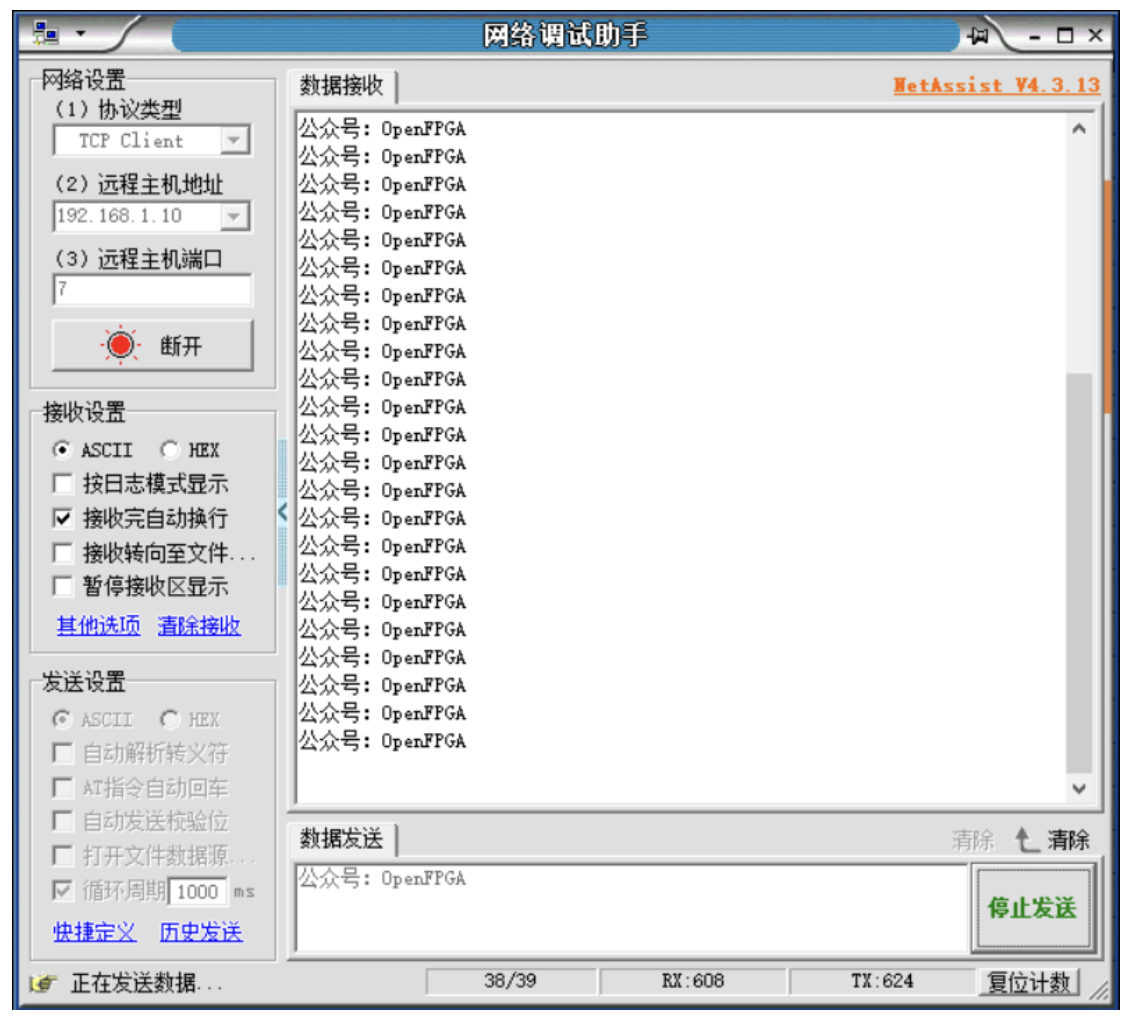

打开网络调试助手,以 TCP Client 模式连接开发板的 IP 地址 192.168.1.10,端口号 7,输入文字发送,网络调试助手便可收到开发板返回相同的文字, 如下图所示。

图8‑197测试结果

原文:OpenFPGA

作者:碎碎思

相关文章推荐

- 优秀的 Verilog/FPGA开源项目介绍(三十一)- OFDM

- HDBaseT是什么协议?与SDI和HDMI比较有哪些区别?

- Verilog“七宗罪”

- 优秀的 Verilog/FPGA开源项目介绍(三十零)- 暴力破解MD5

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。