作者:lijiasen.xy

博客地址:https://blog.eetop.cn/1778649

链接:https://blog.eetop.cn/blog-1778649-6951070.html

目录

ccopt阶段介绍

Initialize

1.1 Check Placement

1.2 update I/O latenty

1.3 set_propagated_clock

1.4 optDesignGlobalRouteStep

1.5 DPlace-Init

1.6 验证CTS配置

1.7 开始综合时钟树

二、Cluster

2.1 refine place

2.2 clock tree legalization

2.3 fix drv

2.4 Insertion Delay Reduction

三、Implementation

3.1 reduce power

3.2 balance

3.3 Polish

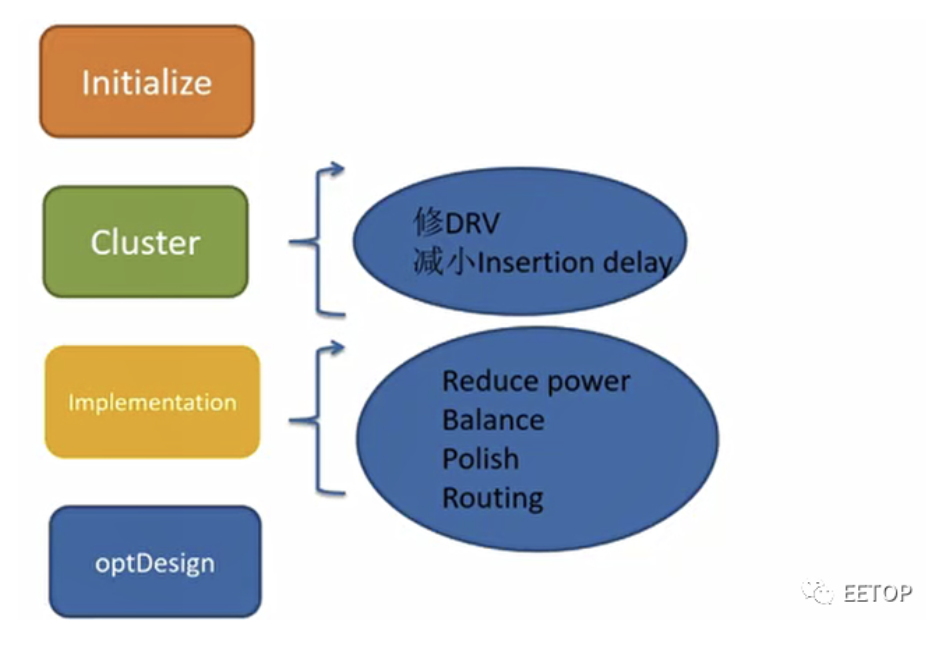

ccopt阶段介绍

cluster :ccopt里面特有的一个概念,聚拢。这里主要是两个步骤,修复drv和insertion delay。insertion delay也就是latency,pin到root点的latency。

implementation:主要的步骤。其中polish为磨平,打平。这里创建完时钟树之后通常是不会动了,处于fix的状态。

ccopt一共有四个步骤,如图所示,接下来分别看每个步骤都做了什么事。

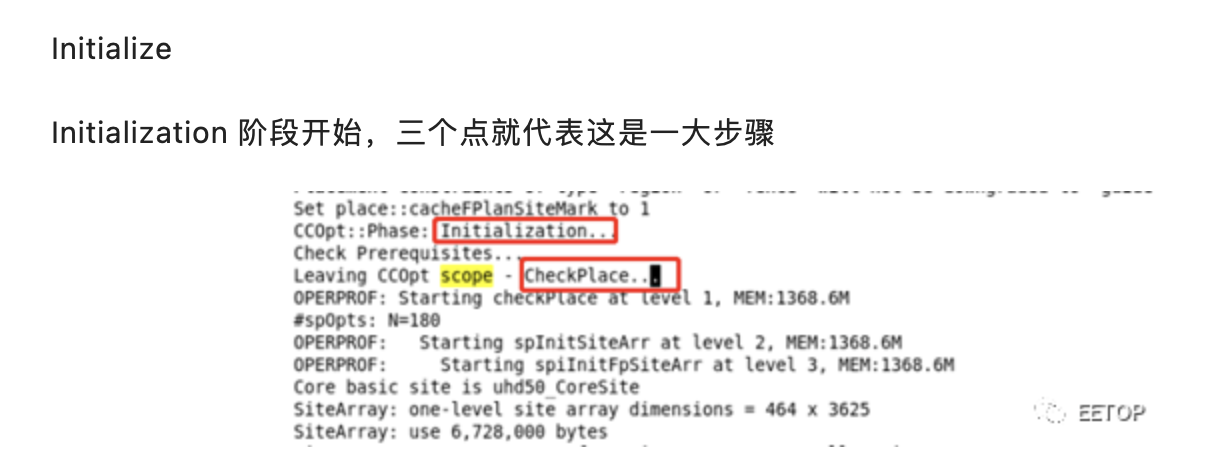

1.1 Check Placement

最先开始的就是对placement的检查,这里检查比较严格,有问题就会停止。

如图,最后报告了cell已placed的数量以及density等

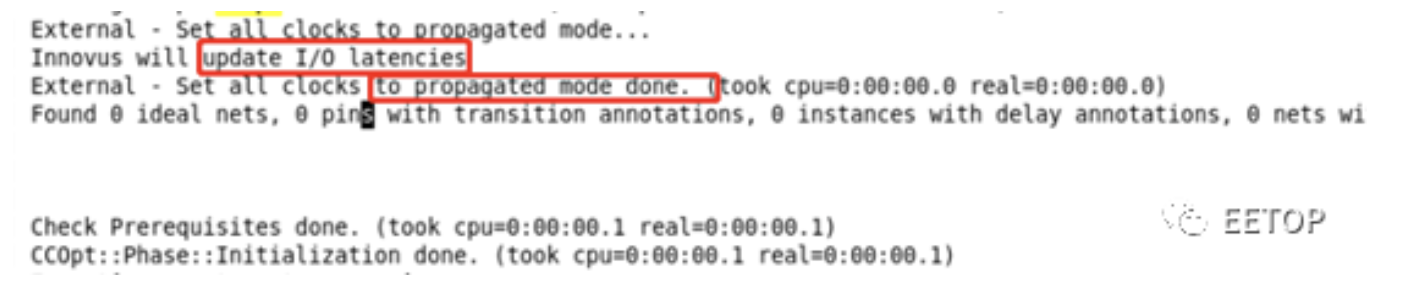

1.2 update I/O latenty

更新I/O latenty

1.3 set_propagated_clock

ccopt引擎会自动把clock path设置为propagated mode。

到这里前面的检查阶段就完成了。

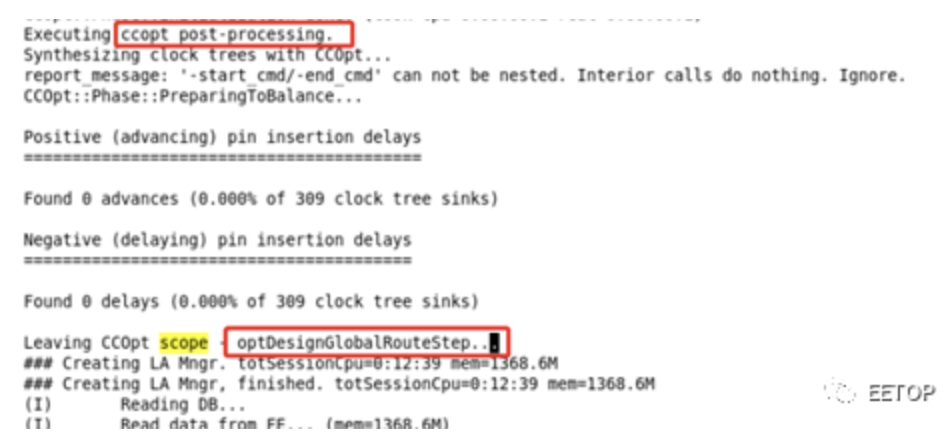

1.4 optDesignGlobalRouteStep

执行时钟树综合进程:

先对时钟树进行初步的global绕线

期间会进行绕线overflow和congestion分析。

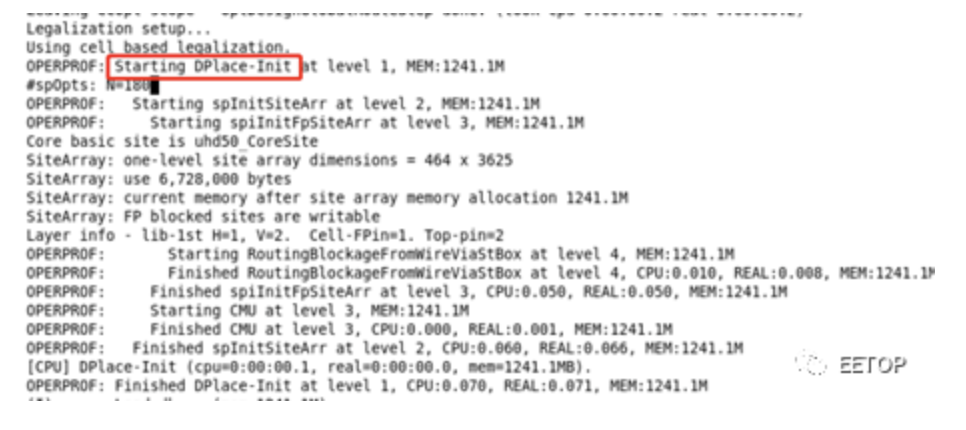

1.5 DPlace-Init

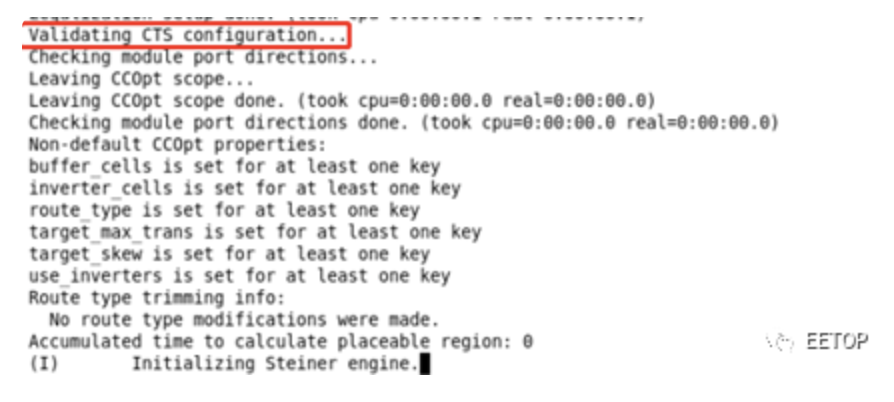

1.6 验证CTS配置

at least one key说明设置参数为非默认的。至少设置过一次,是用户自己设置的

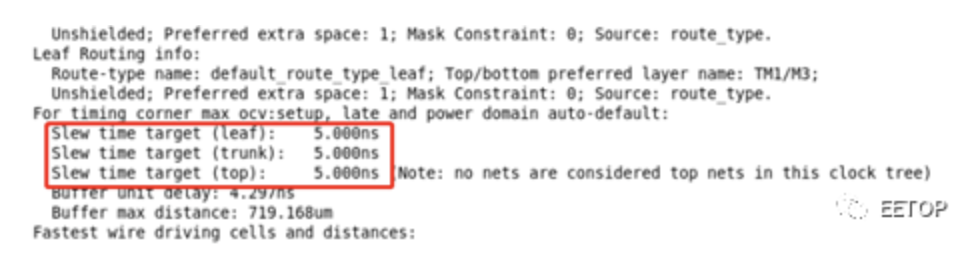

包括一些配置信息:还会自己设置上top的slew target

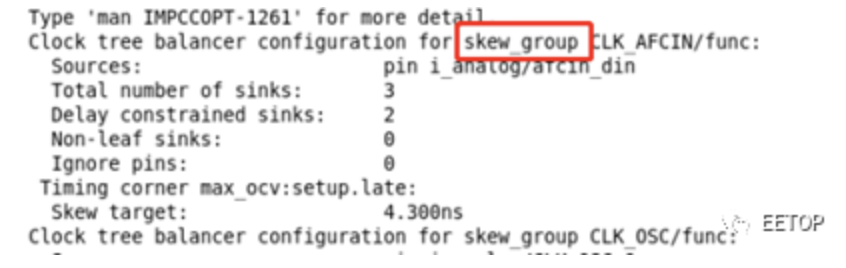

确认skew group上的一些信息

由于ccopt检查很严格,导致一些设置不合理的ingore pin被舍弃掉了

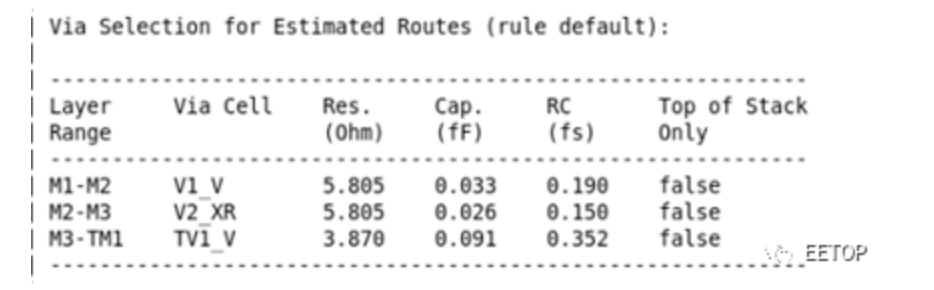

Estimated routes为cts阶段的绕线引擎,因为此时需要计算rc和插入buf等操作,需要计算net的delay信息。这里的via rc信息是供cts来使用的,后期的nanoroute是不会使用的。

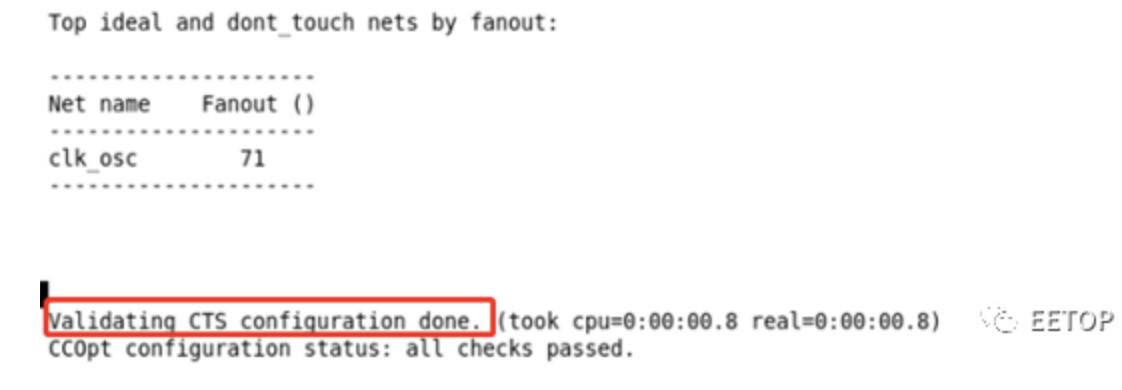

到这里验证配置阶段就结束了。

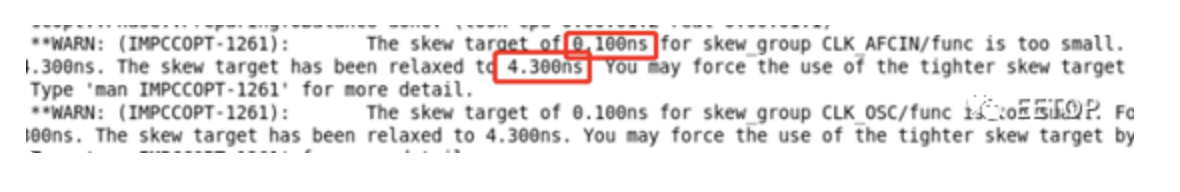

如果设置不合理,ccopt也会主动显示出来,并作出最优选择,例如:

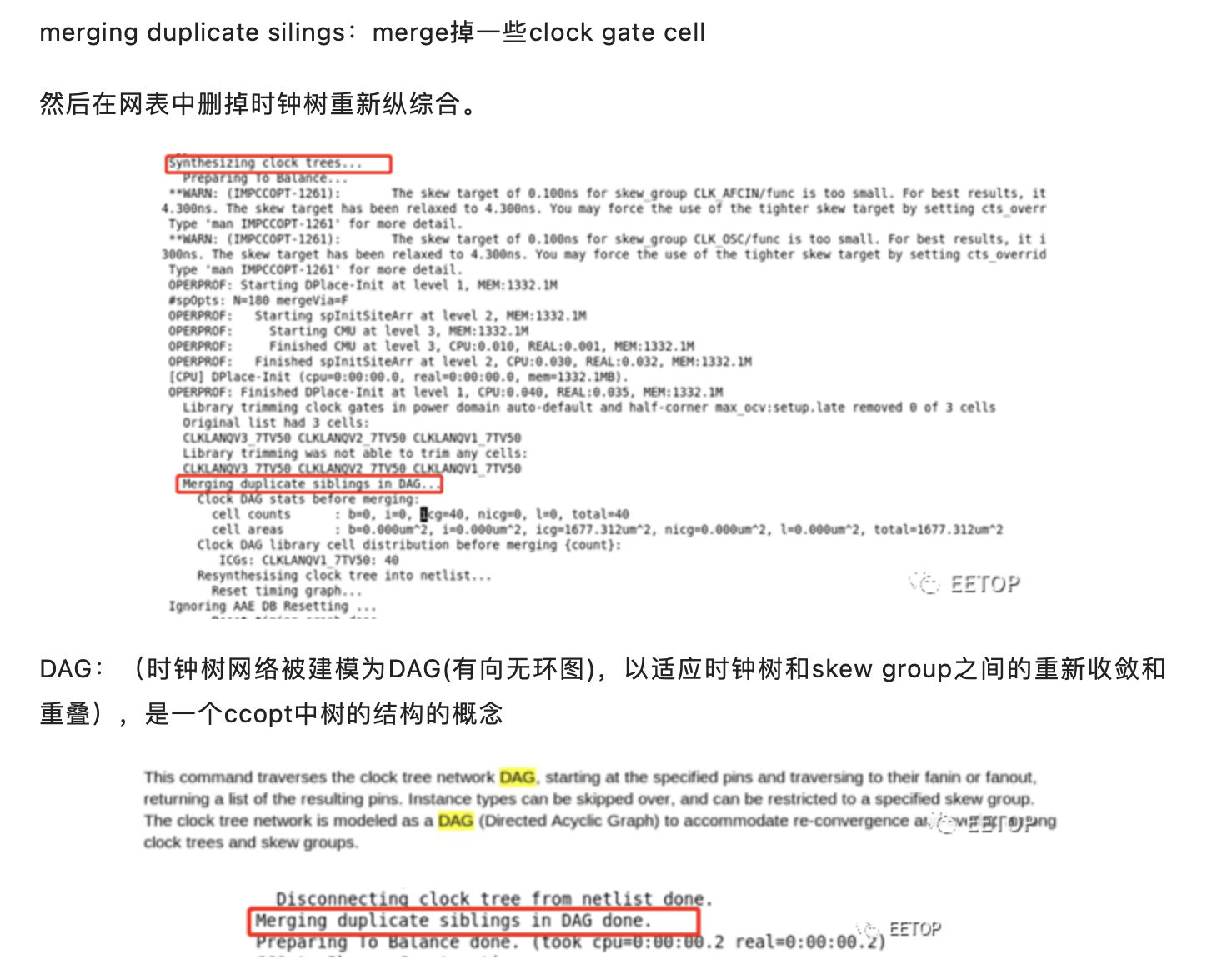

1.7 开始综合时钟树

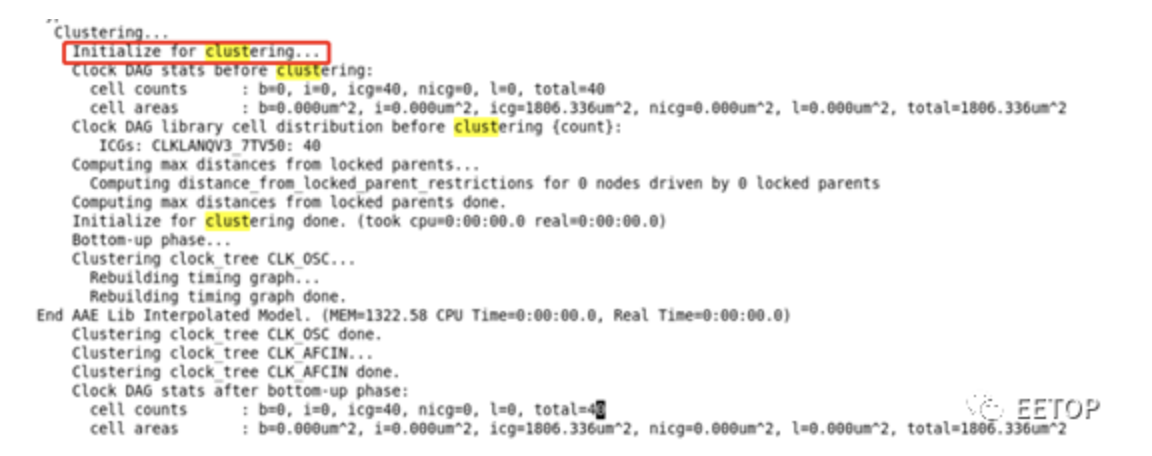

二、Cluster

cluster阶段:修复drv和insertion delay

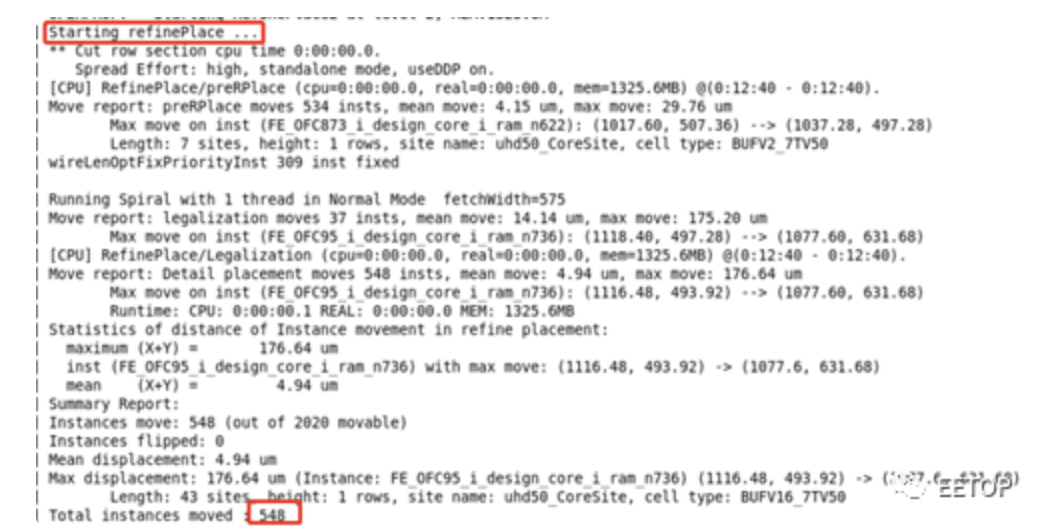

2.1 refine place

聚 拢cell,对全局的drv快速的修一下,并不是详细的修,所以后面调用了refine place得到cell的位置。后面显示了cell移动的数量和多少距离

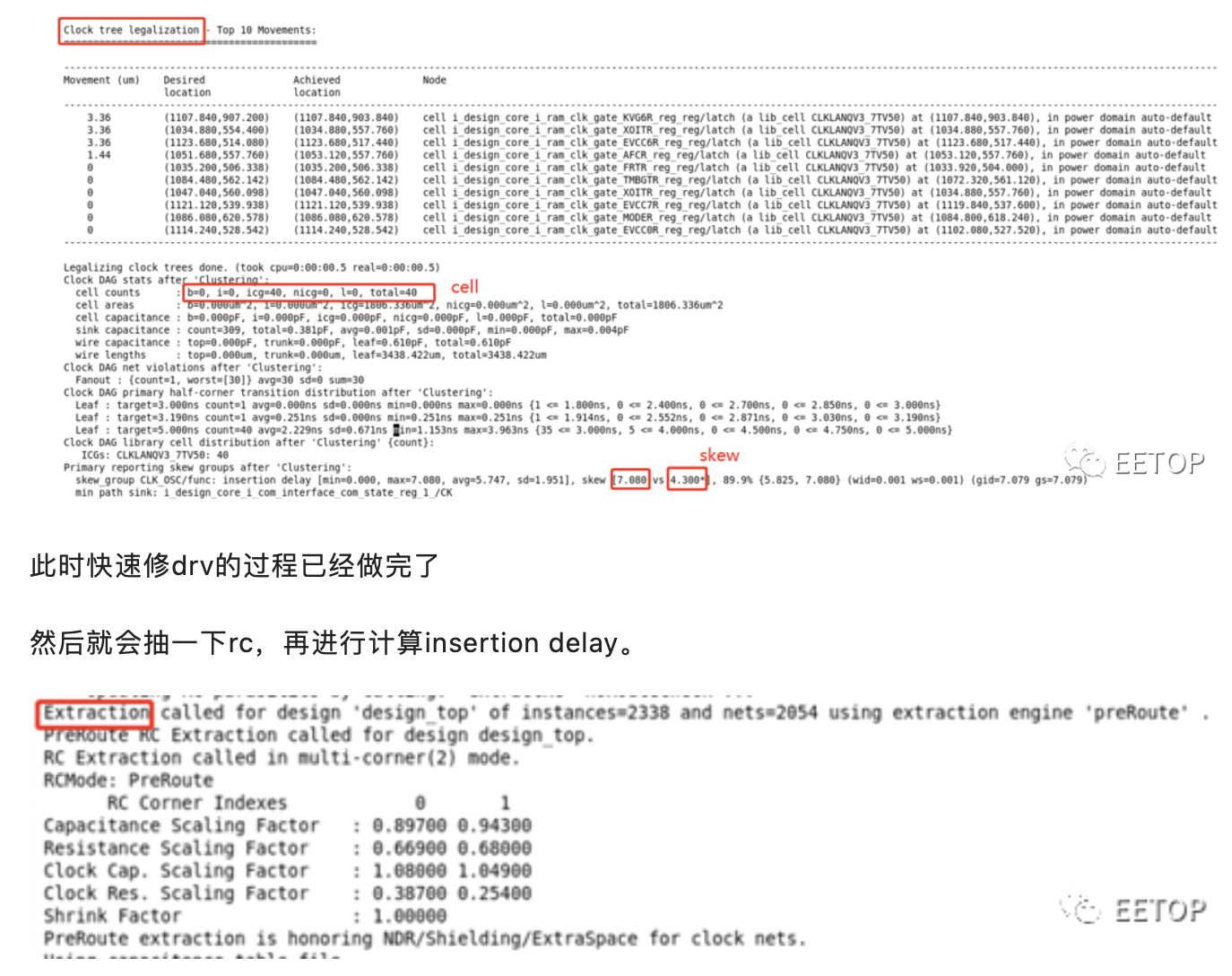

2.2 clock tree legalization

cluster之后显示使用了什么cell,

b:buffer 103个;i: inv 0个;nicg:clock gate cell 0 个;l:logic cell 0个

insertion delay:sd为方差

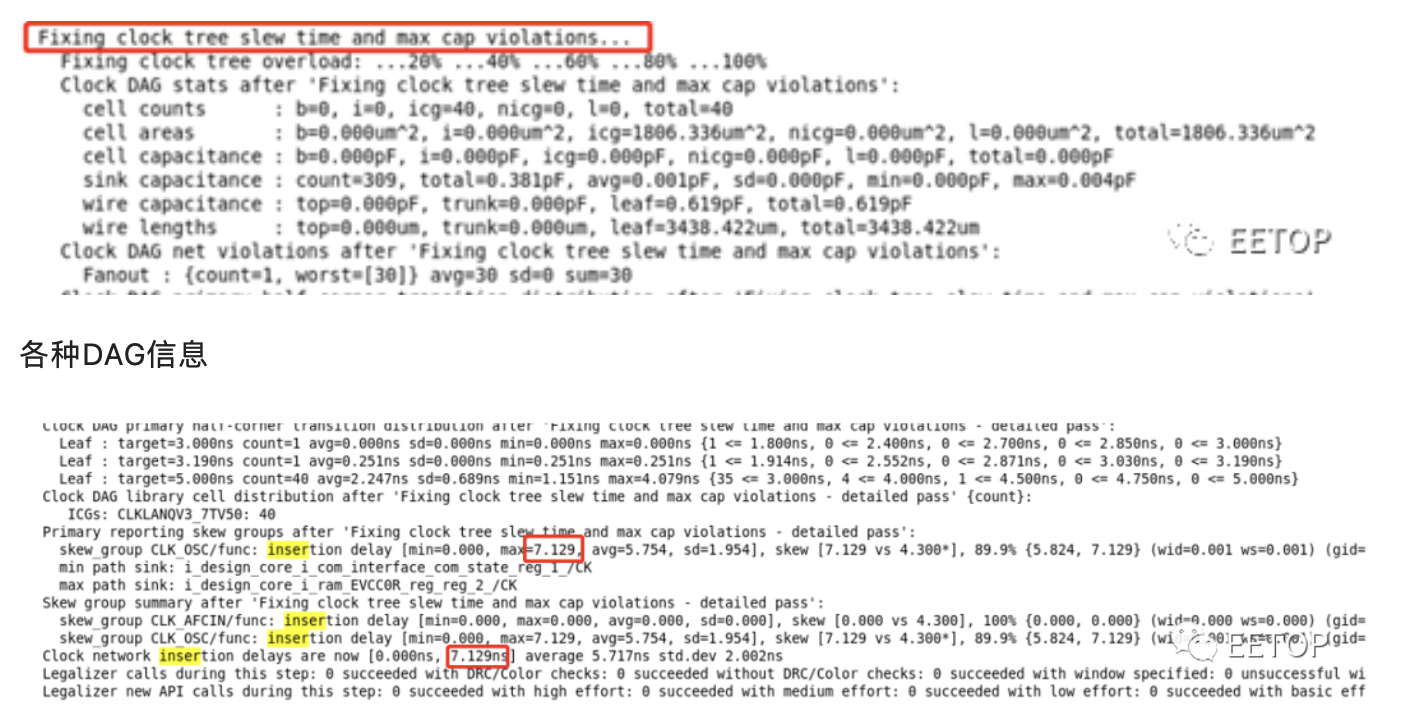

2.3 fix drv

接下来就是详细有drv的过程,这个过程会做两次。并且会报出优化之后使用的cell。

由于修复drv可能会插入inv,buf等cell会导致insertion delay变大,所以后面需要减少delay。

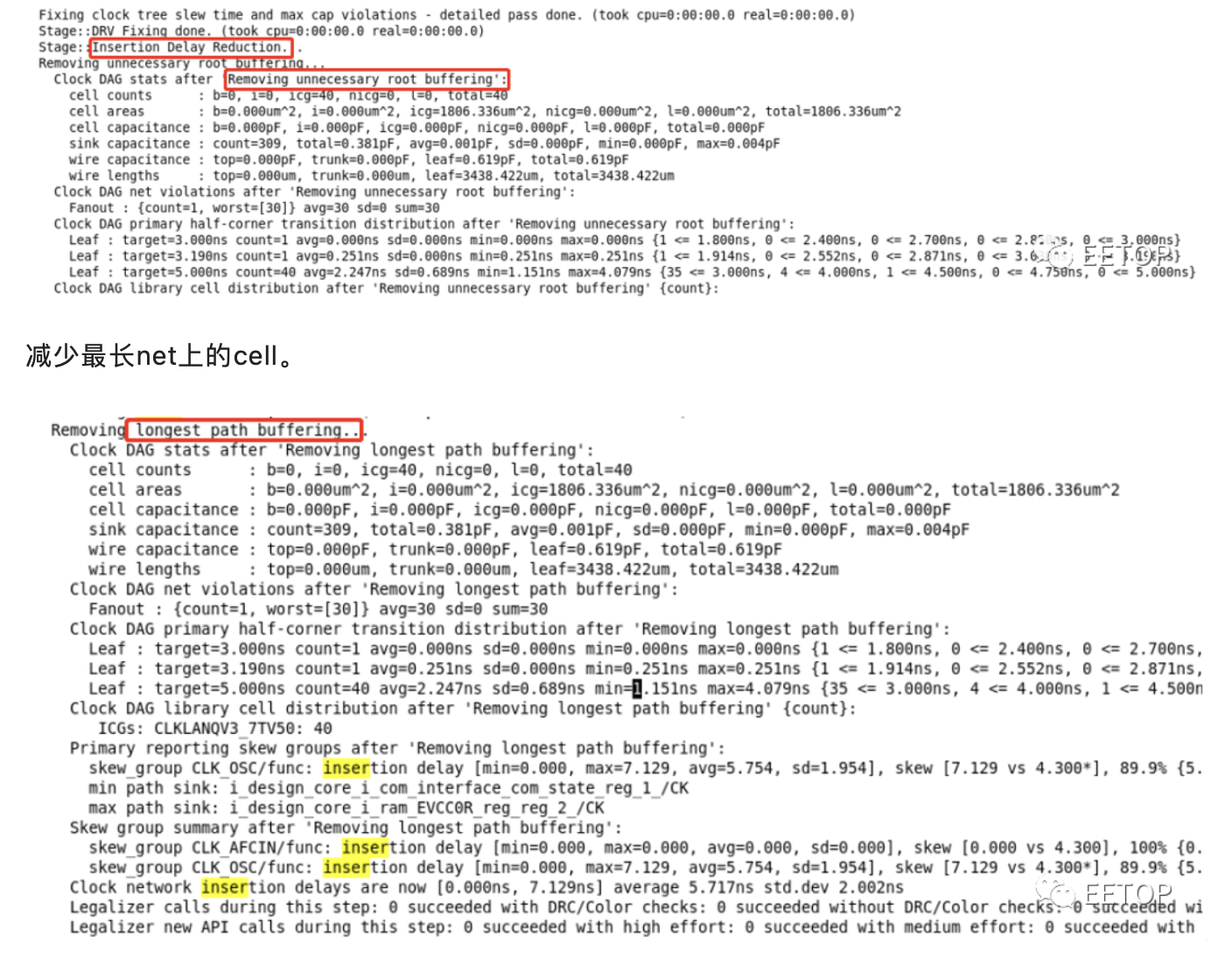

2.4 Insertion Delay Reduction

通过减少不必要的buffer,由于这个design很简单,这里没有可以减得buffer了。

这个过程也是两次。

此时cluster就做完了!

三、Implementation

减少功耗、balance、polish、route

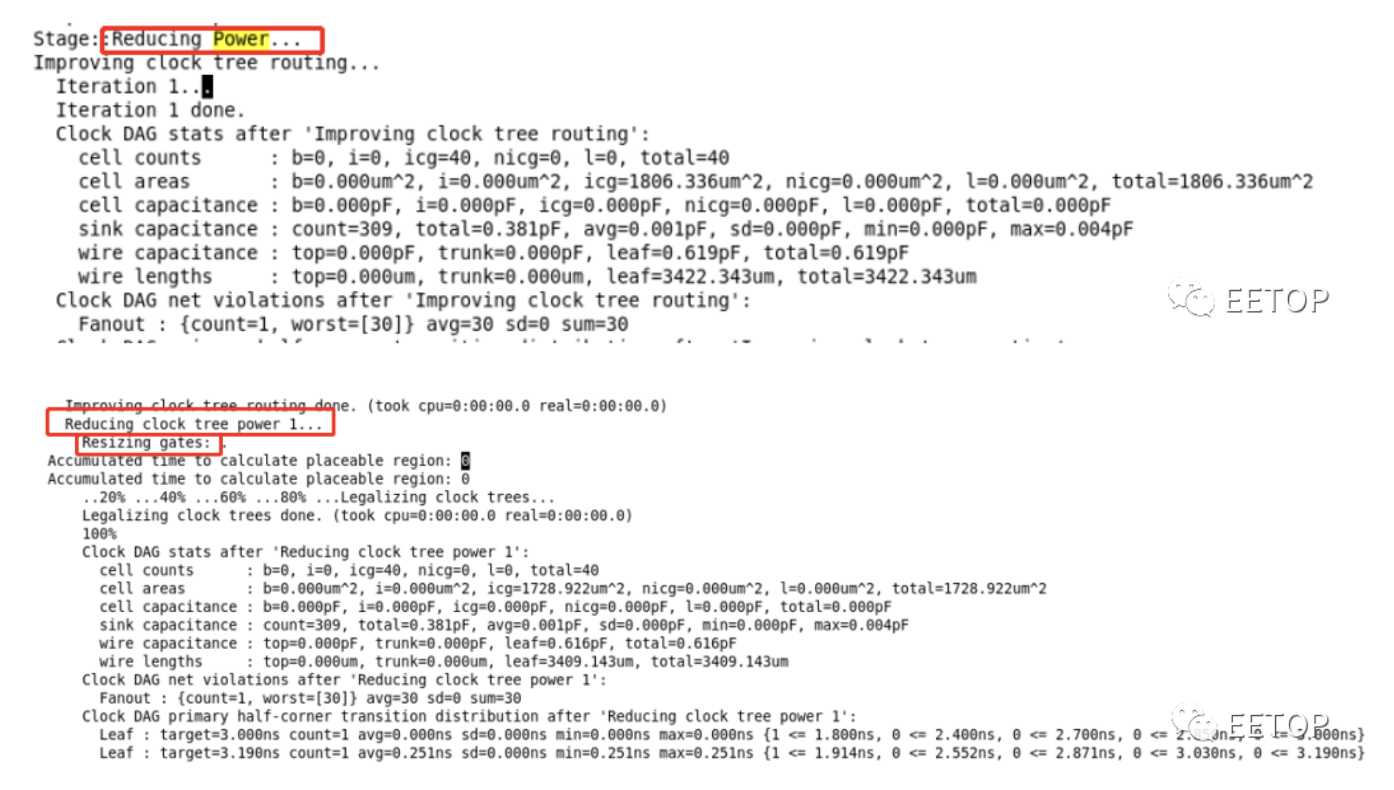

3.1 reduce power

cell越大的话,功耗会越大,所以可以通过size down的方式减小功耗,这里也会做两次。

功耗做完之后就会开始进行balance了,会分很多的小步骤。

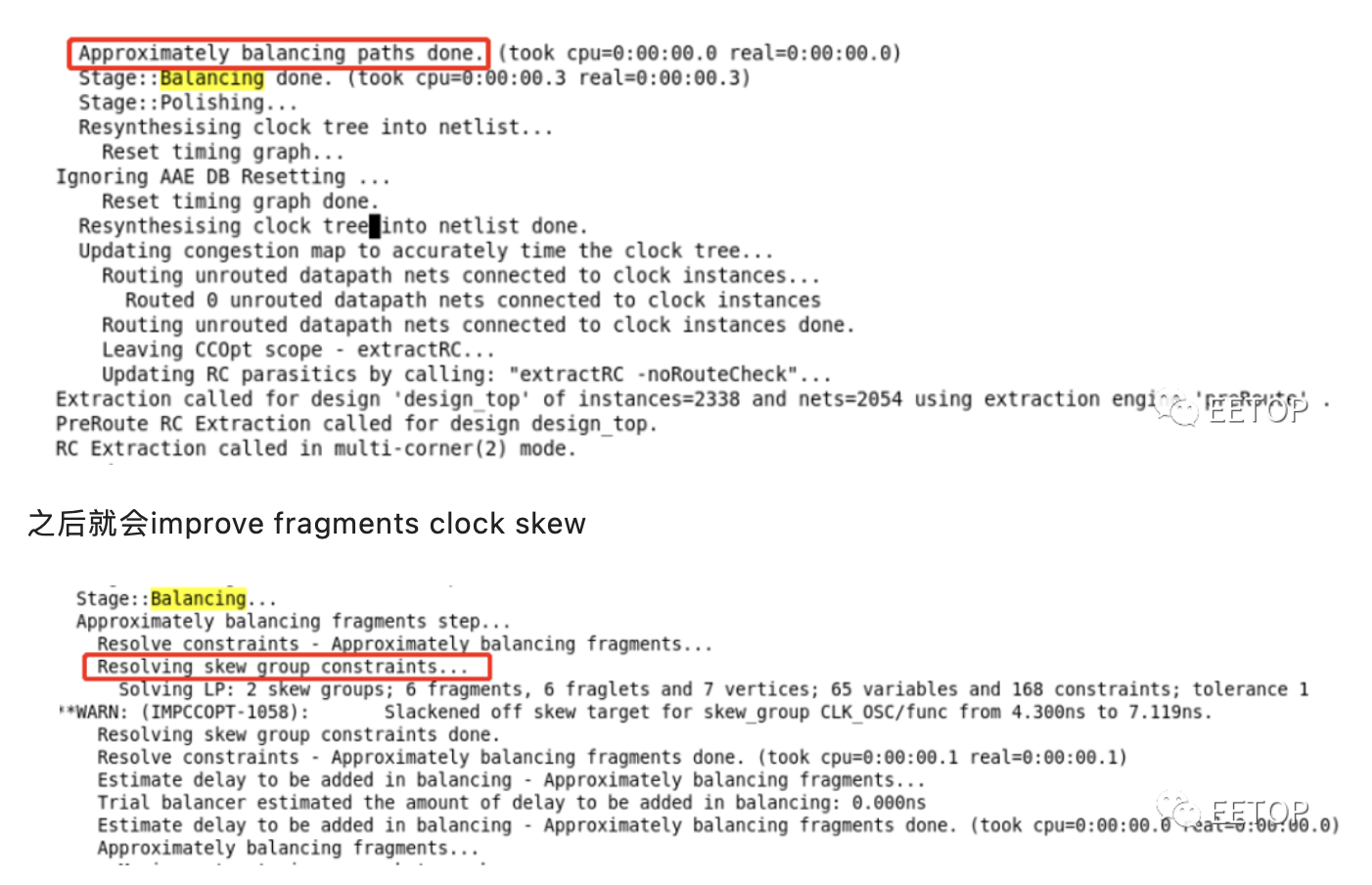

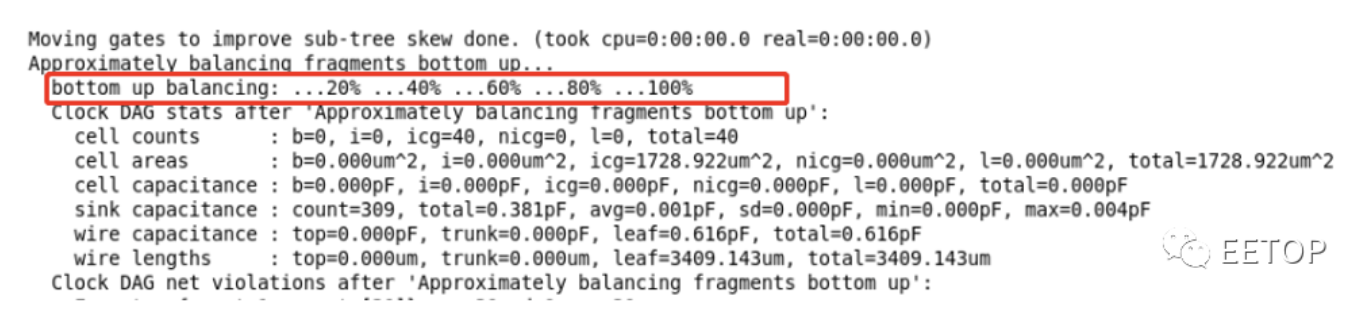

3.2 balance

首先是两轮的balance-Approximately balancing fragments step

前面的两次balance的effort是最大的,后面就是简单的修复工作。

balance之后由于插了buffer,可能影响drv,多以会在这些步骤上多次的修复,直到找到最好的平衡点。

通过一系列操作减少insertion delay,修复drv,balance等。

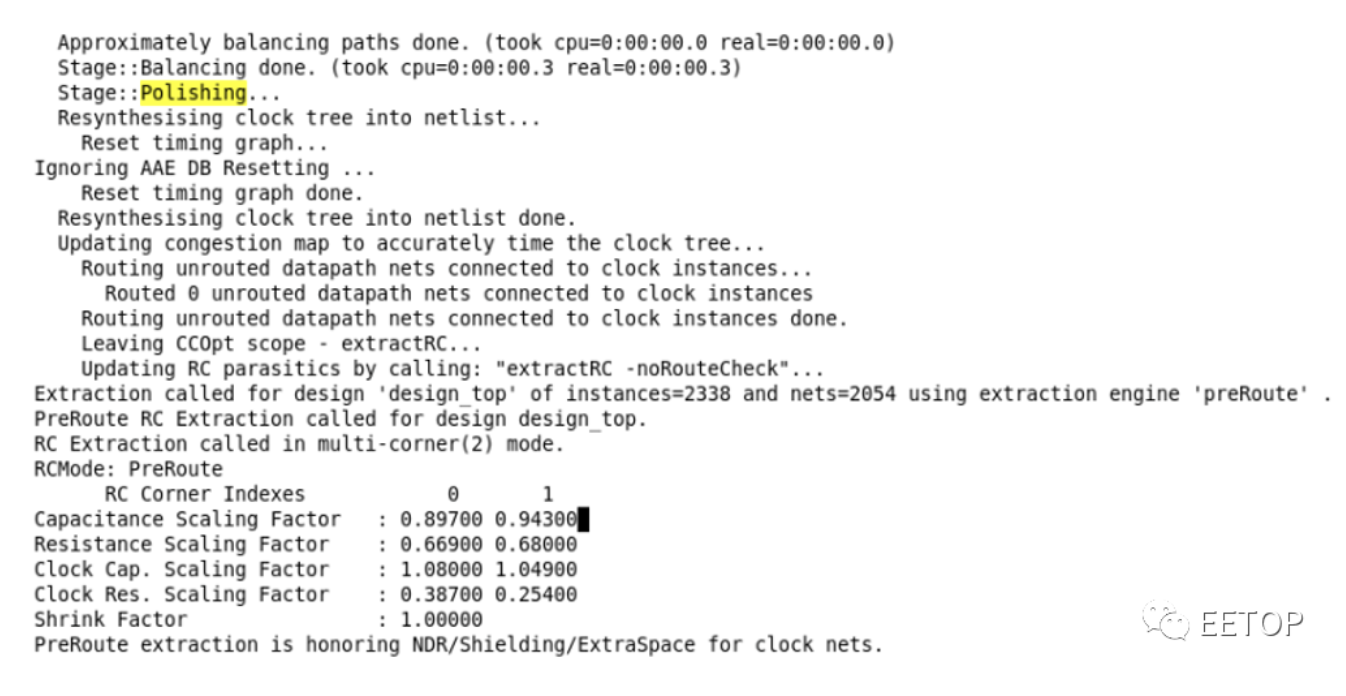

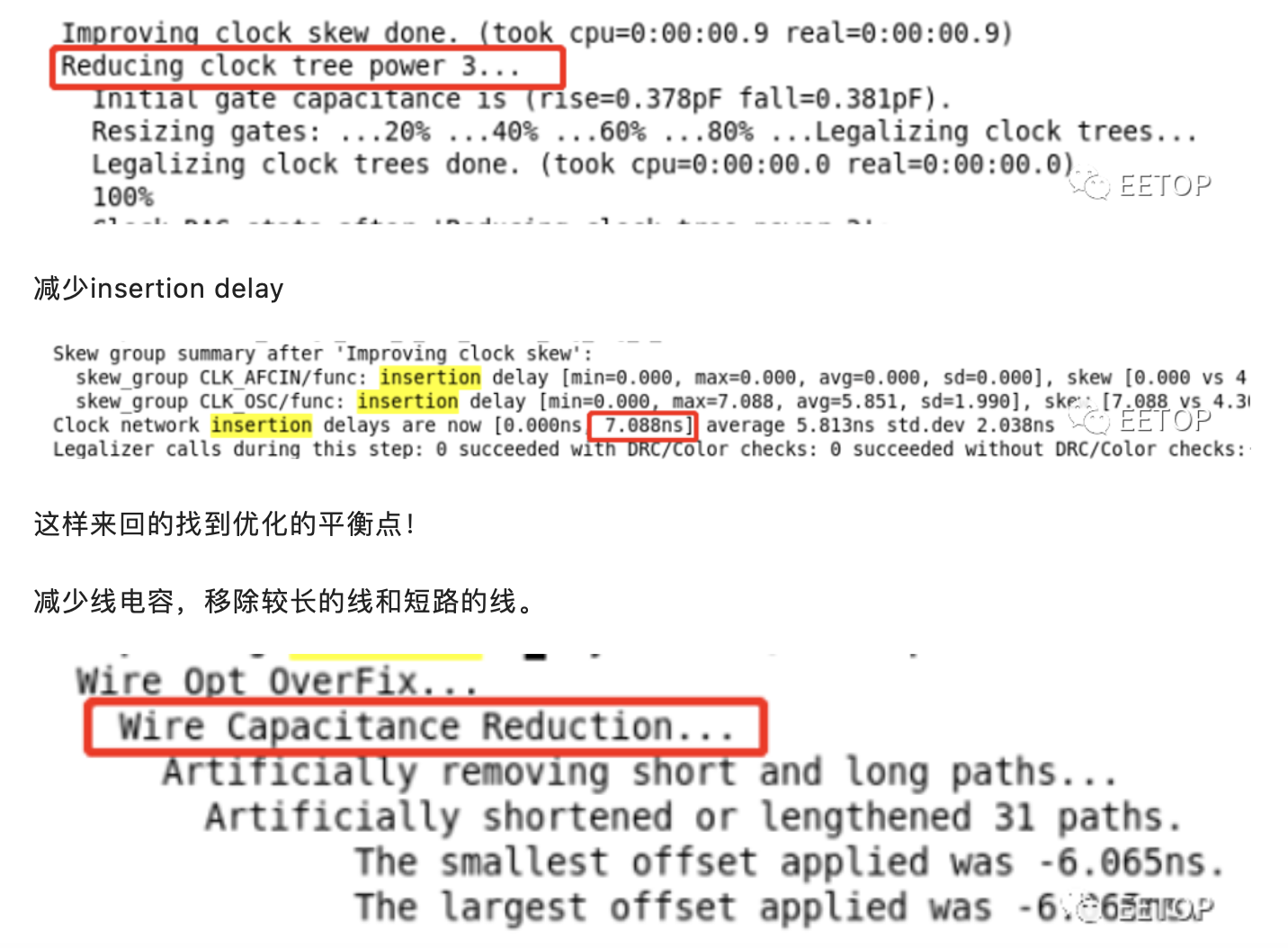

3.3 Polish

balance阶段过后进入polish阶段

把tree整体做短一点

第三次减少power

refine placement,合理摆放cell

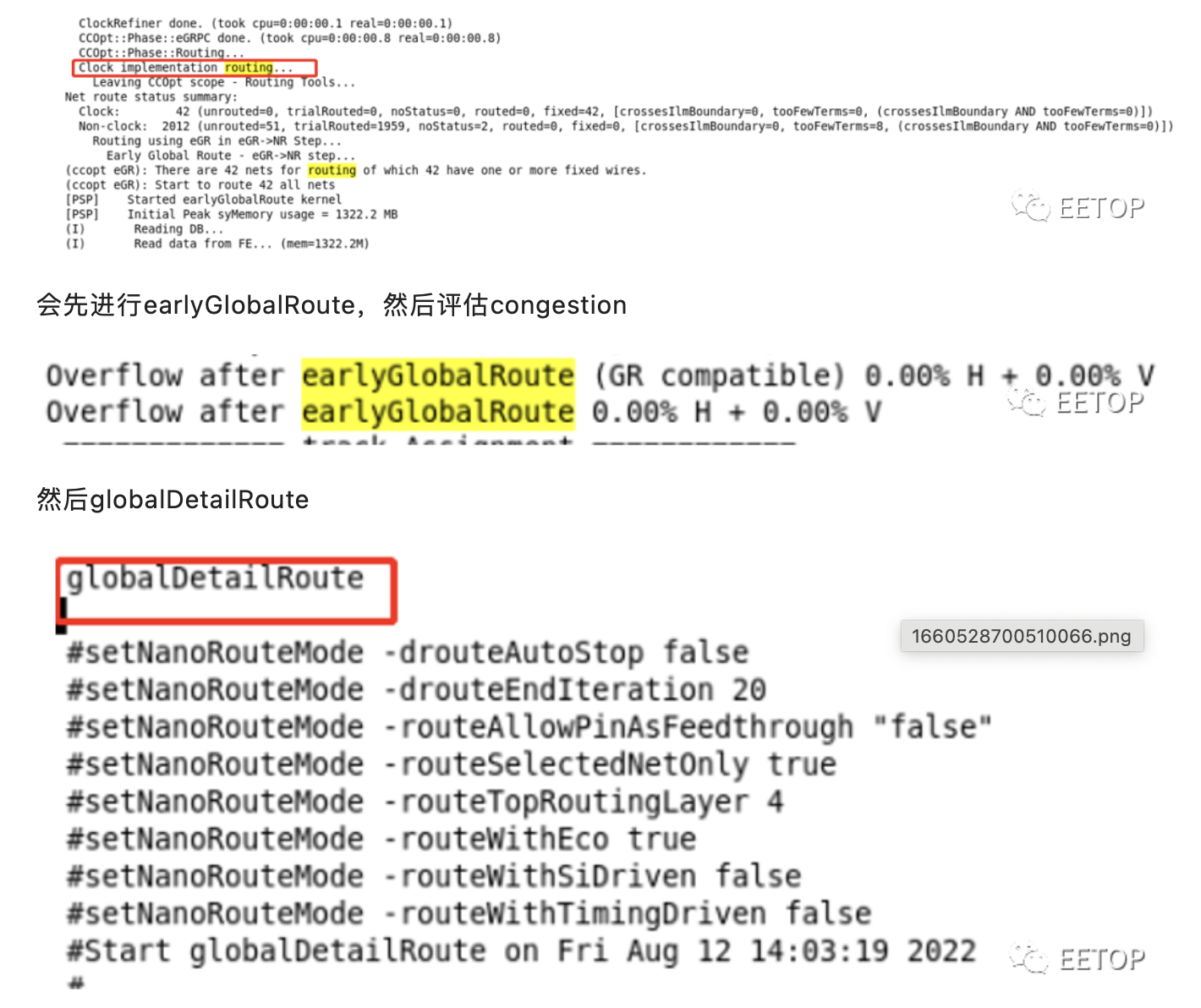

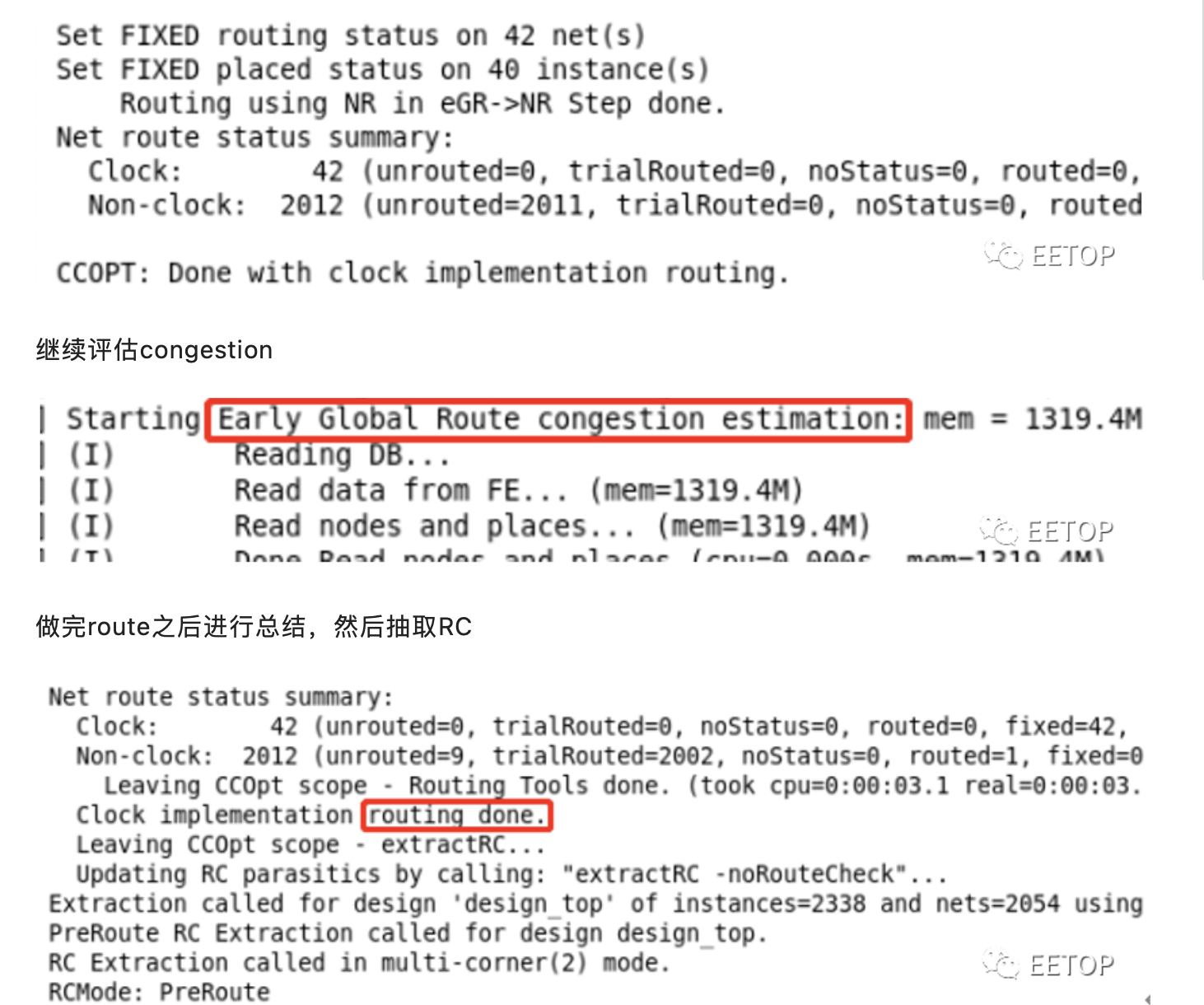

最后进入clock的route的过程,布线之后就fix。这里就会真正的调用nanoroute布线引擎。

3.4 route

开始对时钟树进行绕线

这里结束route

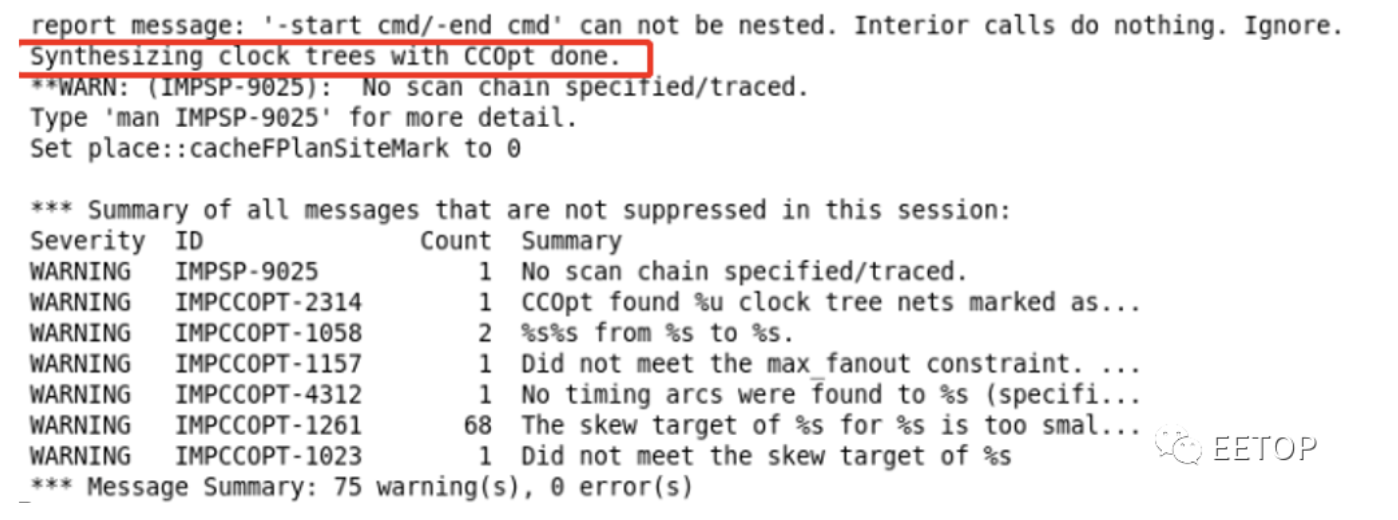

到这里就结束了

接下来就是对时钟树进行时序优化阶段,基本上内容类似。

作者: lijiasen.xy

文章来源: EETOP

推荐阅读

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。