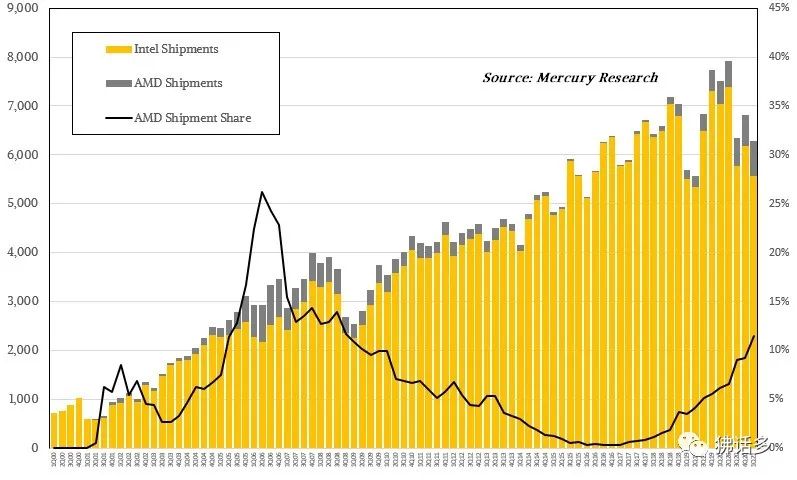

在本世纪初,AMD 通过引入 64 位、多核等设计,延续了 x86 的生命力, 自身也获得了略超四分之一的市场占有率:Mercury Research 的数据显示,2006 年第二季度,AMD 在 x86服务器 CPU 出货量上的份额达到 26.2%。

此后,英特尔重整旗鼓发起全方位的反击,AMD CPU 在服务器市场的占比一路走低。超过 10 年的衰退期随着第一代 EPYC(霄龙)处理器的诞生而宣告终结,经过三代霄龙产品的接力,仅用了五年时间,AMD CPU 在服务器市场上的份额就从几乎可以忽略不计,回升到 10% 以上——2021年第三季度达到 10.2%,第四季度升至 10.7%。

市场份额迅速回升的背后,是 AMD(再一次)探索出了 x86 服务器 CPU 的发展方向。

长久以来,制程和架构是 CPU 的两大支柱。

先说制程,AMD 采用的代工模式,使他们可以选择市场上最为先进的制程来生产 CPU。

不过,为 AMD 吹响服务器市场反攻号角的第一代 EPYC 处理器(代号 Naples),与同时期的英特尔第一代至强可扩展处理器都是 14nm,制程上并无优势。第二、三代 EPYC 虽然用上了英特尔还没有的 7nm,但也不是“纯”的 7nm,而是 7nm + 14nm 的混合结构。所以,重点还是要先落在架构上。

模块化与 Chiplet

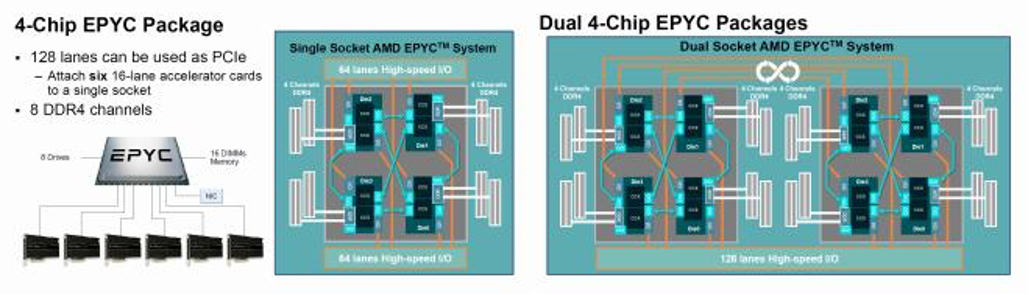

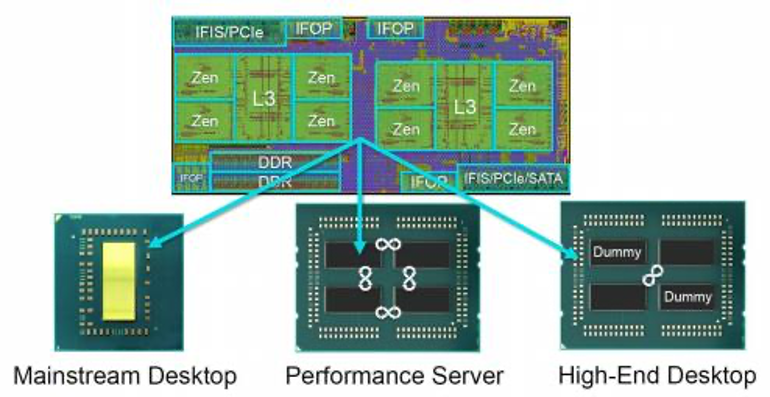

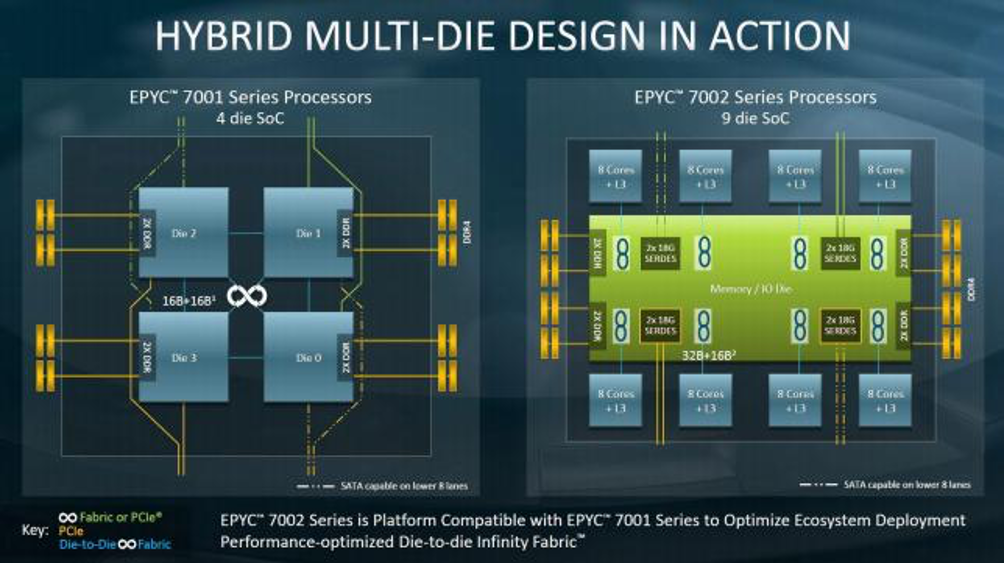

第一代 EPYC 处理器(7001 系列)最多能提供 32 个核心,超过前两代至强可扩展处理器。其核心价值并不在核心数略多几个,而是实现的方式:采用多芯片模块(multi-chip module,MCM)架构, 由 4 个对等的晶片(die)构成,每个晶片包括 8 个核心及其 Cache(4 MiB L2、16 MiB L3)、DDR 和 Infinity Fabric/PCIe 控制器,名为CCD(Core Complex Die, 核心复合晶片)。每个 CCD 内部,除了 2 个由核心和 Cache 组成的 CCX(Core Complex,核芯复合体), 还有 2 个 DDR 内存控制器(各对应 1 个内存通道),用于晶片间互连的 Infinity Fabric(IF On-Package,IFOP),而 CPU 之间互连的 Infinity Fabric(IF Inter-Socket,IFIS)与对外的 PCIe 通道是复用的。

AMD 提供的数据表明,每个晶片的面积为 213mm²(平方毫米), 4 个晶片的 MCM 封装总面积为 852mm²,如果要用大型单一芯片来实现,面积可以缩小到 777mm²,大约节省 10%,但是制造和测试成本要提高约 40%,完全 32 核的收益下降约 17%、成本提高约 70%。

道理不难理解:随着每个 CPU 核心越来越复杂,对应的 Cache 容量 越来越大,CPU 上的核心数还越来越多,在这种乘数效应下,要由一个完整的芯片提供 32 个核心和 80MiB+ Cache 所对应的晶体管,良率面临的挑战肯定会大很多。

很显然,生产 4 个 213mm² 的芯片,再互连为一体,也比生产 1 个 777mm² 的芯片要容易得多, 而且这种模块化的方法, 更具灵活性。

再通俗一点说,就是把(原本的)一个大芯片拆分成多个(互连的)小芯片,不仅能提供更多的核心,还可以降低成本。

但是,这种多晶片完全对等、全部直连的设计,在架构和制程上也有其局限性:

架构的扩展:增加晶片数量比较难,不利于核数的进一步增长;

制程的优化:CCD 中 I/O 器件占比过高, 会冲淡先进制程的效果。

在第一代 EPYC 处理器的 CCD(Core Complex Die)中,核心及其 Cache 构成的 CCX 所占面积为 56%,略多于一半。其余部分是 DDR 内存、Infinity Fabric(IFOP/IFIS)和 PCIe 的控制器等 I/O 器件,从制程提高到 7nm 中获益很小,没必要和 CCX 捆绑在一起。

代号 Rome 的第二代 EPYC 处理器(7002系列)拿出了解决方案:把 DDR 内存控制器、Infinity Fabric 和 PCIe 控制器等 I/O 器件集中到一个单独的晶片里,居中充当交换机的角色,叫作 I/O Die(IOD),仍然采用成熟的 14nm 制程;两边布置多达 8 个 CCD,CCD 内部的核心、Cache 等所占面积高达 86%,可以从 7nm 制程中获得较大的收益。

这种 7 + 14(nm 制程)的 1 + 8(数量) “大小芯片”异构组合,被称为 Chiplet(小芯片)架构。把 CPU 从单个完整的芯片拆分为多个小晶片,为不同制程搭配使用提供了可能,在 7nm 制程初期良品率不足的情况下尤显重要。这种模块化方法的另一个好处是,通过组合不同核心数的 CCD,或者直接调整 CCD 的数量,就可以按需提供从 8 核心到 64 核心的灵活选择。

虽然有 7nm 加持,毕竟核心数翻了一番,第二代 EPYC 处理器旗舰款的 TDP 也从第一代的 180 瓦猛增到 280 瓦。

将整个 CPU 连为一个整体的依然是 Infinity Fabric(IF), 由传输数据的 Infinity Scalable Data Fabric(SDF)和负责控制的Infinity Scalable Control Fabric(SCF)两个系统组成。如果将 Infinity SDF 比作芯片运输数据的血管,那 Infinity SCF 就是控制芯片的神经。在第二代 EPYC 处理器中,CCD 上还有互连 2 个 CCX 和外接 IOD 的 Infinity Fabric,而 IOD 上除了用于连接 8 个 CCD 的 IFOP,还集中了 CPU 全部的对外接口,包括 DDR4、PCIe 4.0,和连接另一个 CPU 的 IFIS。

△ 从第一代的 4 晶片结构,到第二代的 9 晶片结构,双 CPU 互连时用掉的 InfinityFabric(图中绿色线)也有所减少

第二代 EPYC 处理器兼容前一代的平台,就是可以在第一代 EPYC 处理 器的主板上使用。不过这个优点更多停留在理论上,主流的选择还是主板也随着 CPU 更新换代,这很大程度上是考虑到 PCIe 升级的需要。

第一代 EPYC 处理器提供 128 个 PCIe 3.0 通道,但在连接另一个 CPU时,有一半的通道要复用为 IFIS,结果单双路配置能提供的 PCIe 通道都是 128 个。第二代 EPYC 处理器率先支持 PCIe 4.0, 之前为第一代 EPYC 处理器设计的主板并未对此做好准备。带宽升级后也不需要那么多的 IFIS 用于互连,第二代 EPYC 处理器在双路配置下最多能提供 162 个 PCIe 4.0 通道。

设计足够成熟,指标上又有明显优势,第二代 EPYC处理器吸引来了很多重量级客户,譬如腾讯云选用该系列 CPU 打造 SA2 实例,在 2020 年春节过后,支撑腾讯会议 8 天扩容 10 万台云主机,满足疫情期间的复工需求。SA2 实例的规格是主频(基频)2.6GHz、睿频 3.3GHz,最大 180 个 vCPU,说明其基于腾讯云定制的 48 核 型 号,因为公开发售的 48 核型号基频(Base Frequency)只 有 2.2 ~ 2.3GHz。TDP未知,应该介于 225 ~ 280 瓦之间。

48 核虽然不是核数最多的一档,但单(物理)CPU 也能提供 90 个 vCPU,可以满足一些对核数要求较高的应用需求。腾讯云的客户案例显示,腾讯广告采用星星海 SA2 90 核超大规格 UMA(统一内存访问)单实例,检索业务延时比非自研服务器(物理机)降低 25%,单节点性价比翻倍提升,实现了降本增效。

缓存与 3D 封装

AMD 也很清楚,与竞争对手相比,运行频率是比较明显的短板。于是在 2020 年 4 月,AMD 发布了第二代 EPYC 处理器的高频版本 7Fx2 系列,字母 F 即代表 Frequency(频率)。这三个型号面向大数据分析和高性能计算(HPC)等需要高主频、高性能的核心业务应用,其中 8 核的 AMD EPYC 7F32 处理器主频最高,达到了 3.7GHz(睿频 3.9GHz),TDP 也有 180 瓦,已经与 7001 系列的旗舰款同一水平。

有一个经得起考验的整体架构作为基础,接下来的完善和迭代也就 顺理成章。2021 年 3 月,AMD 发布了代号 Milan 的第三代EPYC 处理器(7003 系列),依然是 8 个 CCD 围绕 1 个 IOD 的 Chiplet(小芯片)设计,主要的变化发生在 CCD 内部。

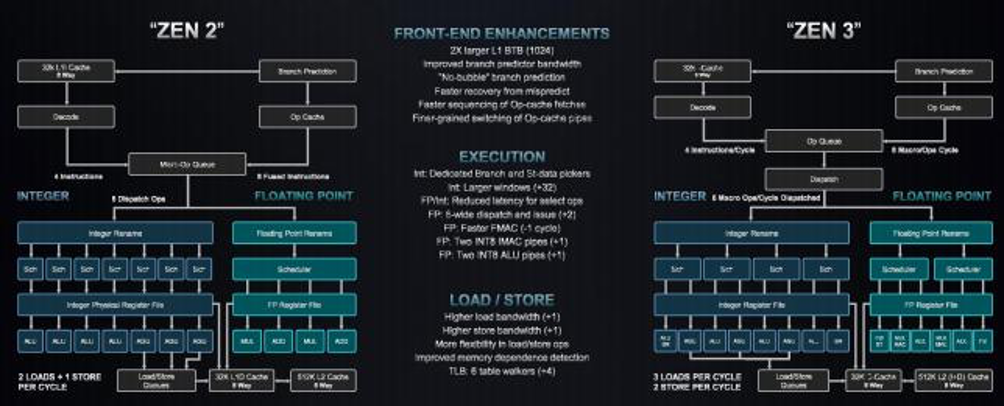

首先是单核性能的提升。新的 Zen 3 核 心,IPC(Instruction Per Cycle, 每时钟周期指令)性能比 Zen 2 提升约 19%,而 Zen/Zen+ 到 Zen 2 的增长“只有”约 15%。性能增幅的贡献来自 Cache 预取、执行引擎、分支预测、微操作 Cache、前端、Load/Store 等多个环节的累积改进。

△相比第二代 EPYC 处理器的 Zen 2 核心,第三代 EPYC 处理器的 Zen 3 核 心全面增强

看起来前端和 Load/Store(载入/存储)的贡献是最大的,其中 Load/Store 从每周期 2 Loads + 1 Stores 增至 3 Loads + 2 Stores,提升幅度分别达 50% 和 100%。Load/Store 属于内存操作,因此增加 Load/Store 带宽,主要受益的是涉及内存密集型的操作,具体要看程序里的动态 Load/Store 指令占比,L/S 动态指令占比越高 L/S 单元性能表现影响应该越大,当然访问内存要涉及一个多层级的复杂系统,所以 L1 D-Cache、L2 和 L3 Cache、硬件预拾取器、主内存等也会有相应的影响。

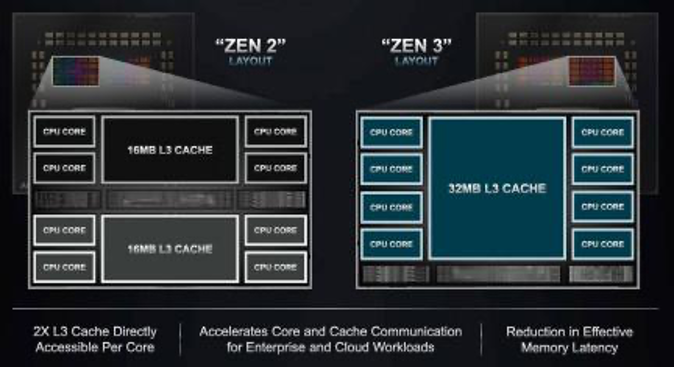

另一个重大的改变就是 CCD 内部的 2 个 CCX 合二为一,由原来的每 4 个核心共享 16MiB L3 Cache,变成 8 个核心共享 32MiB L3 Cache 的 1 个 CCX,也就是在 CCD 内部不再需要通过片上的Infinity Fabric 跨 CCX 访问,每个核心直接访问的 L3 Cache 翻倍,有助于提升大数据集应用的性能。

总的来说,第三代 EPYC 处理器可以视为第二代的完善版本:一方面,整体架构和对外 I/O 基本不变,共用服务器平台(主板)就很有价值了,譬如超微(SuperMicro)的 H12 代 A+ 服务器,只要把 BIOS 升级到 2.0 或更新版本,即可直接支持 EPYC 7003 系列 CPU;另一方面,虽然制程还是 7 + 14,但在同等 TDP 下,7003 系列的 CPU 加速频率比 7002 系列有 5 ~ 10% 的提升,为单核性能优化的高频型号也从 24 核扩展到 32 核,TDP 达到顶级的 280 瓦。

升级的门槛很低,跨度却可能很大。譬如腾讯云同步推出基于 64 核 定制款第三代 EPYC 处理器的 SA3 实例,2.55GHz 的主频只比公开发售的旗舰款 EPYC 7763(2.45GHz)略高,但是,论起最大规格,SA3 实例的 232 vCPU、940GB 内存,比 SA2 实例的 180 vCPU、464GB 内存,分别提高近 30% 和一倍。

旗舰款亦有广阔舞台。在 2021 年 6 月公布的高性能计算(HPC)TOP500 榜单中,前 10 名中唯一的新面孔 Perlmutter 就基于 AMD EPYC 7763,排名第5——之前的第 5 名 Selene 基于 EPYC 7742,也是 64 核,在第二代 EPYC 处理器系列中仅次于旗舰款 7H12。

不仅如此,在美国能源部规划的 Frontier、Aurora、El Capitan 三大 E 级超算(Exascale Computing)中,有两套都基于 AMD 平台实现,包括采用 AMD 提供的 CPU 和 GPU 等全套设备。以 Frontier 为例,使用了代号 Trento 的定制 CPU AMD EPYC 7A53,看型号可知也基于 Zen 3 架构,据传其 IOD 采用了 Infinity Fabric 3.0 来对接 AMD GPU。

△ Frontier超级计算机:业界公布的第一套 E 级超算

加大 L3 Cache 的容量有助于提高缓存命中率,减少内存访问次数,从而大幅度降低延迟。从这个目的来看,Milan 架构打通 CCD 内部只是让每个核心可直接访问的 L3 Cache 容量翻倍,Milan-X 的物理扩容才是大招。

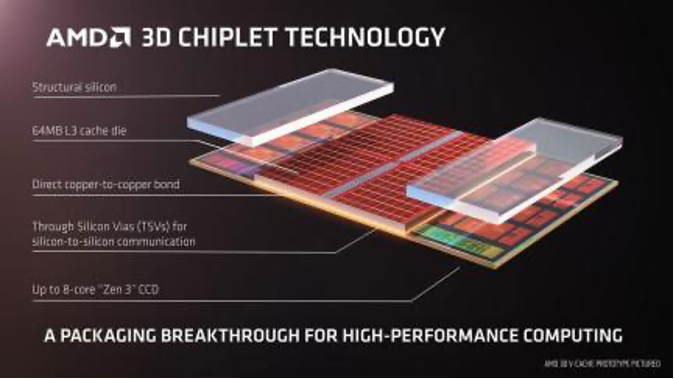

一年之后的 2022 年 3 月 21 日,AMD 宣布“全面推出世界首款采用 3D 芯片堆叠的数据中心 CPU”,即采用 AMD 3D V-Cache 技术的第三代 AMD EPYC 处理器,代号 Milan-X(米兰-X),共 4 款,型号以“3X”结尾。

3D V-Cache(3D 垂直缓存)是AMD 与台积电在 3D 封装技术上合作,将 Chiplet 封装技术与芯片堆叠技术相结合,开发出的 3D 芯片堆叠技术。在一个 CCD 上方直接堆叠一个 64MiB 的 7nm SRAM,将 L3 Cache 容量原地增加 2 倍,达到 96MiB,8 个 CCD 就有 768MiB 的 L3 Cache。

看起来简单粗暴,做起来科技拉满。3D V-Cache 通过硅通孔(Through Silicon Via,TSV)技术在堆叠的芯片间传递信号和电能,支持超过 2TB/s 的带宽,能够提供的互连密度是 2D Chiplet 的 200 多倍,是其他 3D 堆叠方案的 15 倍以上。不仅集成效率更高、密度更大,Die 之间的接口采用铜到铜的直接键合,没有任何形式的焊接凸点,极大的改善了热设计、晶体管密度和互连间距,而且单位信号的能耗只有微凸点 3D 法的三分之一。

应用 3D V-Cache 的目的是提供尽可能大的缓存容量,所以虽然 4 款 Milan-X 处理器的核心数分别为 16、24、32 和 64,但是全部配满了 8 个 CCD(每 CCD 有 2/3/4/8 个核心)和 768MiB L3 Cache,TDP 有 240 瓦和 280 瓦两档,而cTDP(c 代表“可配置”)范围都在 225 ~ 280 瓦之间。

在架构和制程之后,封装技术对 CPU 的重要性也日益凸显出来。

独立安全子系统

回顾三代 EPYC 处理器的发展历程,可以看到,CPU 的核心越来越强大,L3 Cache 的容量也一直在成倍增长。这些核心功能的持续进步,容易让人忽略,其安全特性也在不断完善。

三代 EPYC 处理器的安全性建立在一个独立的安全子系统之上,其核心是 CPU 集成的安全协处理器,这是一个基于 Arm Cortex-A5 的 32 位微控制器。安全协处理器运行一个安全的操作系统 / 内核,安全的片外非易失性存储(如SPI ROM)保存固件和数据,提供安全密钥生成和密钥管理等加密功能,启用经过硬件验证的引导。

在硬件验证的引导过程中,安全协处理器加载片上引导 ROM,该 ROM 加载并验证片外引导加载程序。引导加载程序在 x86 核心开始执行 BIOS 代码前验证 BIOS,也验证和加载安全协处理器使用的代码以提供密钥管理。

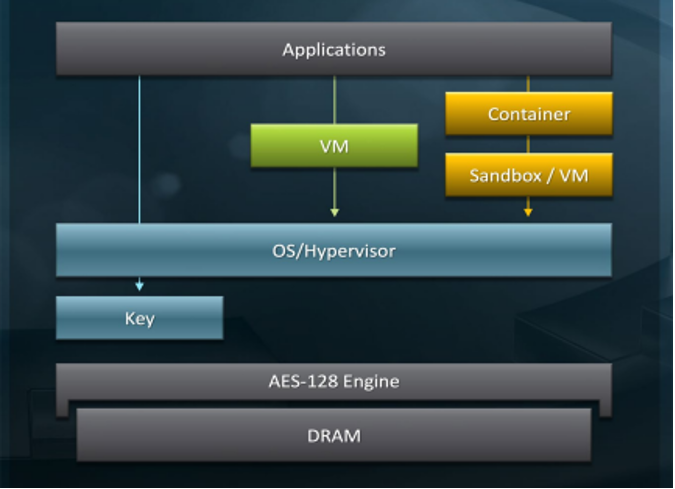

△ 第二代 EPYC 处理器的 SME 设计

EPYC 处理器提供基于硬件的内存加密,其内存控制器具备 AES-128 加密引擎,加密密钥由安全协处理器管理,不暴露给 x86 CPU(的部分)。安全内存加密(Secure Memory Encryption,SME)使用每次系统重启时随机生成的密钥加密全部系统内存。

安全加密虚拟化(Secure Encrypted Virtualization,SEV)在云计算时代的重要性不言而喻,它在虚拟机以及 hypervisor 之间提供强加密隔离,根据虚拟机 ID 选择活动的加密密钥。

第一代 EPYC 处理器支持 128 个线程和 16 个密钥,第二代扩展了 SEV 的能力,支持 256 个线程和 509 个密钥,还加入了 SEV 加密状态、加密 CPU 寄存器(SEV-ES)等功能。到了第三代,进一步增加了 SEV 安全嵌套分页、针对不受信任的 hypervisor 的高级安全特性、支持未修改的 Guest 操作系统, 并提供内存完整性保护(SEV-SNP)。

当然 Arm 的目标可不是在 x86 服务器 CPU 里当个小配角,他们要的是广阔的正面战场。