目录

12.3 Gen3 物理层发送逻辑

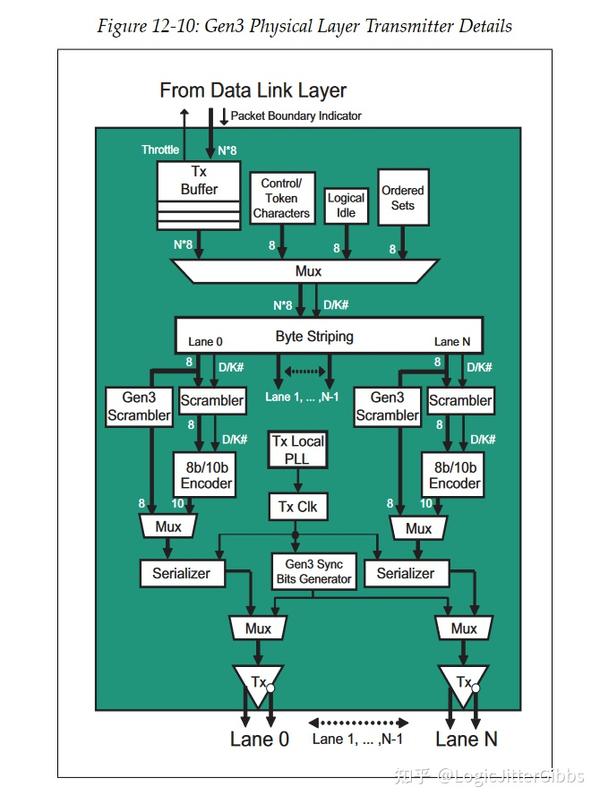

第 422 页的图 12-10 展示了支持 Gen3 速率的物理层传输逻辑的概念框图。整体设计与 Gen2 非常相似,所以没有必要再去重复讨论所有细节,但也存在一些区别。PCIe 新手建议回顾第 361 页的 “物理层-逻辑(Gen1 和 Gen2)” 一章,以了解物理层设计的基础知识。让我们从图的顶部开始,解释 Gen3 实现在整个过程中所做的更改。与之前一样,需要指出的是,下述的物理层实现讨论仅从教学目的出发,不是为了展示实际的 Gen3 物理层实现。

图 12-10 Gen3 物理层发送逻辑细节

12.3.1 多路复用器

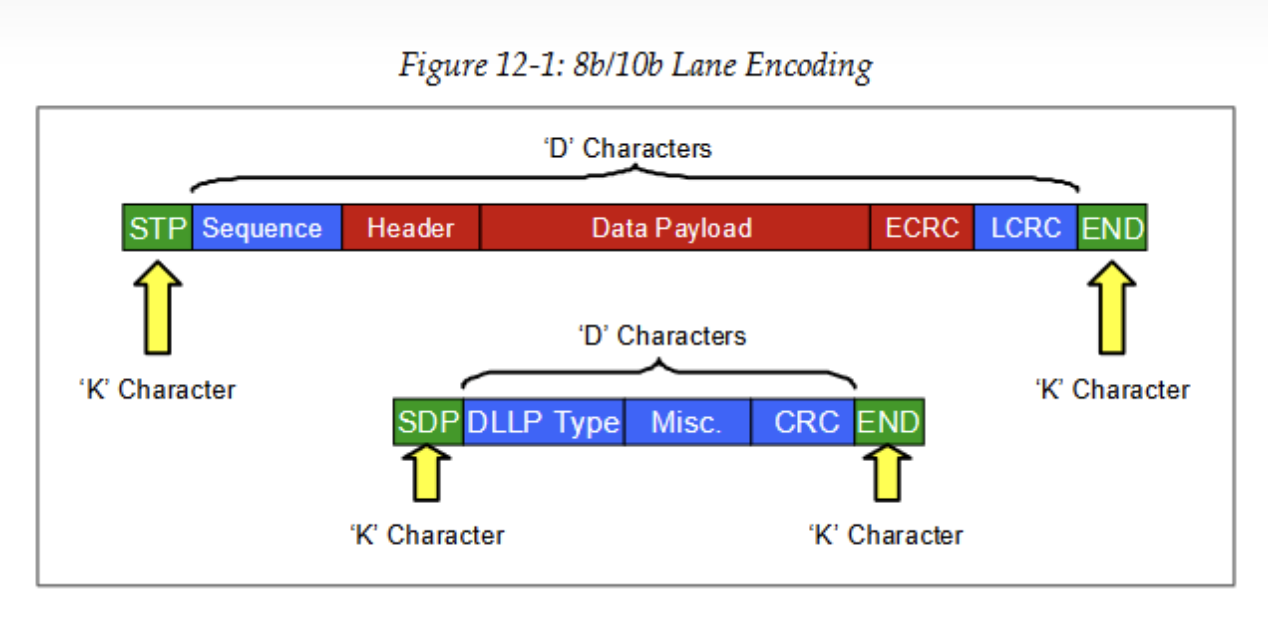

TLP 和 DLLP 来自顶部的数据链路层。多路复用器会在数据输入中添加构建完整 TLP 或 DLLP 所需的 STP 或 SDP 标记。上一节描述了标记格式。

Gen3 TLP 的边界由 TLP 数据包之前的 STP 标记长度字段中的双字计数定义,因此,不需要 END 帧字符。

当结束数据流时或在发送 SOS 之前,EDS 标记被加入数据流。多路复用器根据跳转计时器,定期将 SOS 插入数据流中。其他数据流之外的有序集,如 TS1、TS2、FTS、EIEOS、EIOS、SDS 也可以根据链路要求加入到数据流中。

数据包在由 2 位同步头标识的块中传输,同步头也是由多路复用器添加的。不过,在多通道链路的所有通道上复制同步头,是通过字节条带化(Byte Striping)逻辑实现的。

当没有要发送的数据包或有序集,但链路在 L0 状态下保持活动时,IDL(逻辑空闲,或数据零)标记被用作填充符。这些标记就像其他数据字节一样被加扰,并在接收端解码并识别为填充符。

12.3.2 字节条带化(Byte Striping)

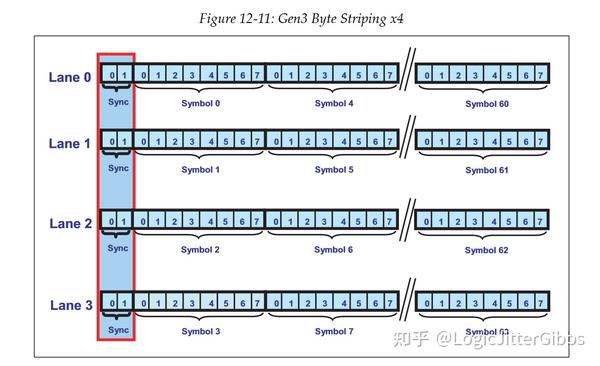

这种逻辑将要传送的字节分布在所有可用的通道上。帧规则已在第 417 页 “发送端帧要求” 中进行了描述,现在让我们看一些示例并讨论如何应用这些规则。

首先考虑第 424 页图 12-11 所示的示例,其中说明了 4 通道链路。注意,当一个新的块开始时,同步头位同时出现在所有通道上,并定义了块的类型(本例中是数据块)。块编码对于每个通道都是独立处理的,但字节(或符号)在所有通道上都是条带化(striped)的,就像早期几代 PCIe 一样。

图 12-11 Gen3 x4 比特条带化示例

12.3.2.1 字节条带化 x8 示例

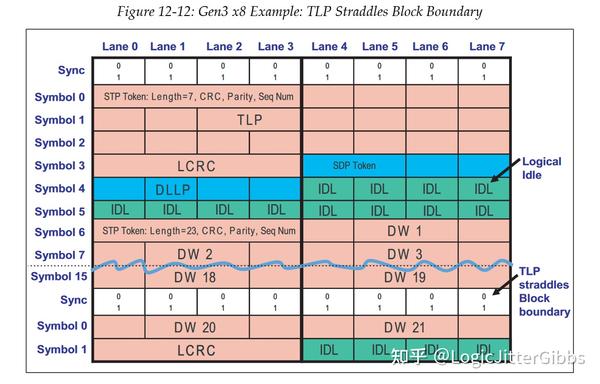

接下来,考虑第 425 页图 12-12 所示的 x8 链路,这是基于的规范中的一个示例重新绘制的,以便于阅读。注意这里的比特流是垂直绘制的,而不是像之前的图 12-11 那样是水平的。在图 12-12 顶部,我们可以看到按要求以小端顺序显示的同步位,同时出现在所有通道上,指示数据块传输的开始。

在此示例中,首先发送 TLP,所以符号 0-4 包含 STP 帧标记,包括标记在内的整个 TLP 长度为 7DW。接收端需要知道 TLP 的长度,因为对于 8GT/s 速度,没有 END 控制字符(标识 TLP 的结束边界) 。相反,接收端统计双字(来找到 TLP 的结束边界),如果没有观察到 EDB(End Bad),则认为 TLP 是正常的。在这种情况下,TLP 在符号 3 的通道 3 处结束。

图 12-12 Gen x8 示例:TLP 分跨块边界

接下来,从通道 4 和 5 上的 SDP 标记开始发送 DLLP。由于 DLLP 的长度始终为 8 个符号,因此它将在符号 4 的通道 3 结束。暂时,没有其他数据包要发送,因此 IDL 符号将被传输,直到另一个数据包准备就绪。发送 IDL 时,下一个 STP 标记只能在通道 0 中启动。在本例中,TLP 从符号 6 的通道 0 开始。

下一个 TLP 的数据包长度为 23 DW,这是一个有趣的情况,因为在下一个块边界之前只有 20 个双字(dwords)可用。当数据块结束时,发送端发送同步头,并在下一个数据块的符号 0 期间继续 TLP 传输。换句话说,数据包只是在必要时跨越块边界。最后,TLP 在符号 1 的通道 3 完成。再一次,没有需要发送的数据包了,因此发送 IDL(作为填充)。

12.3.2.2 无效的数据包 x8 示例

当跨交换机直通 TLP 以减少延迟时,可能会出现无效的 TLP。这称为交换机直通(Switch Cut-Through)操作。在继续讨论之前,读者可以选择阅读第 354 页标题为 “交换机直通模式(Switch Cut-Through Mode)” 的部分。

无效的 TLP 只可能出现在交换机的出端口,在接收方在入端口接收到数据包,即进行错误检查之前。此例中,因为会检测到一个错误,所以 TLP 肯定是无效的。

图 12-13 说明了使 TLP 无效的步骤。出端口发送的 TLP 从第一块开始(符号 6 的通道 0)。当检测到错误时,出端口反转 CRC(符号 1 的通道 0-3),并在 TLP(符号 1 的通道 4-7)之后立即添加一个 EDB 标记。这两个更改一起向接收端表明,这个 TLP 已经无效,应该被丢弃。请注意,EDB 字节不包括在数据包长度字段中,因为当发生错误时,它们会动态地添加到传输中的数据包中(译注:此时原 TLP 的长度已经在 STP 中传输给了对端,想改也不能改了)。

图 12-13 Gen3 x8 无效报文

12.3.2.3 有序集示例 – SOS

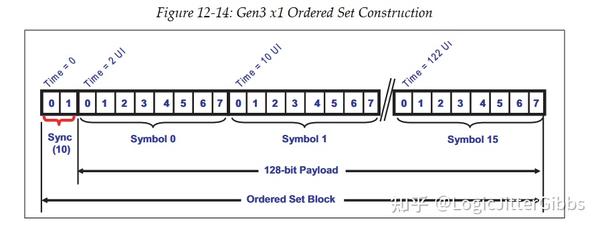

现在我们来考虑一个有序集传输的示例。如第 427 页图 12-14 所示,一个有序集的特征是其 2 位同步首部值为 01b。同步头之后的字节将被接收端理解为构成一个长度为 16 字节(128 比特)的有序集。唯一的例外是 SOS(Skip Ordered Set),因为它可以被中间接收方以每次增加 4 个字节增量改变,用于时钟补偿。因此,允许一个 SOS 的长度为 8、12、16、20 或 24 个符号。如果存在不会在 SOS 中添加或删除 SKP 的链路中继器设备,SOS 将由 16 个字节组成。(译注:原文如此 In the absence of a Link repart device that does not add or delete SKP)

图 12-14 Gen3 x1 有序集结构

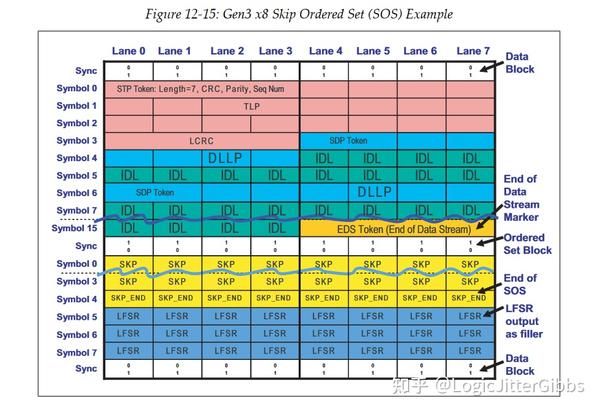

让我们以一个 SOS 为例来,说明有序集各种特性以及它们是如何一起工作的。注意第 428 页的图 12-15,图中数据块后面跟着的是 SOS。帧规则规定,前一个数据块必须以最后一个双字中的 EDS 标记结束,以便让接收端知道一个有序集即将到来。如果当前的数据流要继续下去,则后面的有序集必须是 SOS,而且 SOS 之后必须依次是另一个数据块。有一种场景并没有在本例中体现: 此时 TLP 有可能还没有完成,并在必须紧跟 SOS 之后的数据块中恢复传输,来跨越 SOS 传输一个 TLP。

收到 EDS 标记意味着数据流要么结束,要么暂停并插入一个 SOS。EDS 是唯一可以在与 IDL 相同的符号时间,在双字对齐的通道上开始的标记,这个例子就是这样,从符号时间 15 的第 4 通道开始传输 EDS。回顾一下背景知识,EDS 也必须位于数据块的最后一个双字里。根据接收端的帧要求,在 EDS 之后只允许有一个有序集块,而且必须是 SOS、EIOS 或 EIEOS,否则将被视为成帧错误。与早期规格版本一样,有序集必须同时出现在所有通道上。接收端可以选择检查以确保每个通道都收到了相同的有序集。

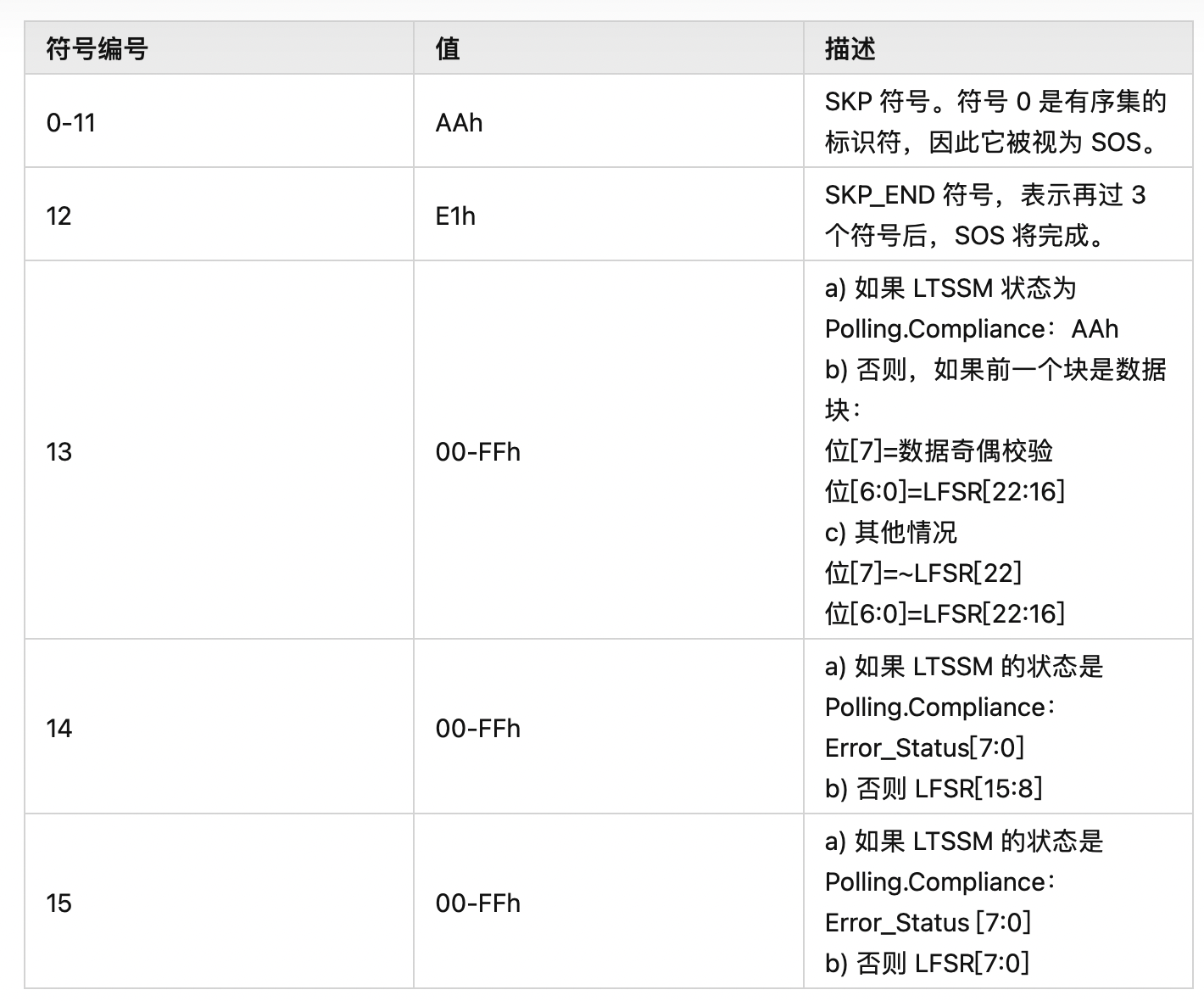

在我们的例子中,接下来看到的是一个 16 字节的 SOS,它在接收端由有序集的同步头以及 SKP 字节模式识别。在 SOS 的末尾始终有 4 个符号,包含了当前 24 位加扰器 LFSR 状态。在符号 12 中,接收端知道 SKP 字符已经结束,同时也知道该块还有三个字节要在每条通道上传输。这些是加扰逻辑 LFSR 的输出,如第 428 页的表 12-2 所示。

图 12-15 Gen3 x8 SOS 示例

表中提到的数据奇偶校验位是自最近的 SDS 或 SOS 以来,发送的所有数据块加扰字节的偶校验,并且为每个通道独立创建。接收端需要计算和检查奇偶校验。如果校验位与数据不匹配,则必须设置与出现错误的通道对应的通道错误状态(Lane Error Status)寄存器位,但这不会被视为接收端错误,也不会启动链路重新训练。

8 位的 Error\_Status 字段只有在 LTSSM 处于 Polling.Compliance 状态时才有意义(详情见第 529 页的 “Polling.Compliance”)。对于我们的数据块之后的 SOS 例子,第 13 字节是数据奇偶校验位和 LFSR[22:16],而最后两个字节是 LFSR 位[15:0]。

12.3.2.4 发送端 SOS 规则

使用 128b/130b 时,发送端的 SOS 规则包括。

• 一个 SOS 必须被安排在 370 至 375 个块内发出。然而,在 Loopback 模式下,Loopback Master 必须在这个时间段内安排两个 SOS,而且它们之间的距离不得超过两个块。

• SOS 仍然只能在数据包边界发送,因此可能会累积多个待发送的 SOS,但是,连续的 SOS 是不允许的;它们之间必须间隔数据块。

• 建议每当发送端处于电气空闲状态时,复位 SOS 计时器和计数器。

• 使用 128b/130b 时,链接控制寄存器 2 ( Link Control Register 2)中的一致性(Compliance)SOS 位无效。(它用来在 8b/10b 编码模式的一致性测试中禁用 SOS,但是 128b/130b 编码模式不支持这一选项)。

12.3.2.5 接收端 SOS 规则

使用 128b/130b 编码模式时,接收端接收 SOS(Skip Ordered Set)的规则包括:

• 他们必须容忍以 370-375 个块的平均间隔接收 SOS。请注意,电气空闲后的第一个 SOS 可能会提前到达,因为发送端不需要在电气空闲时间内复位 SOS 计时器(译注:虽然建议发送方这么做)。

• 接收端必须检查数据流中的每个 SOS 之前都有一个以 EDS 结尾的数据块。

12.3.3 加扰

128b/130b 的加扰逻辑是从前几代 PCIe 修改而来的,以解决 8b/10b 编码时代无需考虑(8b/10b 编码本身特性会解决这两个问题)的两个问题:保持 DC 平衡和提供足够的转换密度(transition density)。回顾一下,DC 平衡意味着比特流中的 1 和 0 的数量相等。这是为了避免 “DC wonder” 的问题,即传输介质持续充电/放电,以至于始终保持在某个电压值,通常为 1 或 0,以至于难以在必要短的时间内切换到另一信号电平值上。另一个问题是,接收端的时钟恢复逻辑需要在输入信号中看到足够的跳变边缘(edge),以便能够将它们与恢复的时钟进行比较,并根据需要调整时序和相位。

在没有 8b/10b 编码来处理这些问题的情况下,采取了三个步骤:第一,新的加扰方法在较长的时间段内改善了转换密度和 DC 平衡,但不能像 8b/10b 编码那样在短期内保证它们。第二,训练期间使用的 TS1 和 TS2 有序集模式包括根据需要调整的字段,以改善 DC 平衡。第三,接收端必须比前几代更加鲁棒,能容忍这些问题。

12.3.3.1 LFSR 的数量

在较低的数据速率下,每条通道都以相同的方式进行加扰,因此一个线性反馈移位寄存器(LFSR)可以为所有的通道提供加扰输入。然而,对于 Gen3,设计者希望为相邻的通道提供不同的加扰值。其原因可能包括希望通过加扰彼此的输出来减少通道之间串扰(cross-talk)的可能性,并避免在每个通道上有相同的值,比如发送 IDL 时。该规范描述了实现这一目标的两种方法,一种是强调更低的延迟,另一种是强调更低的成本。

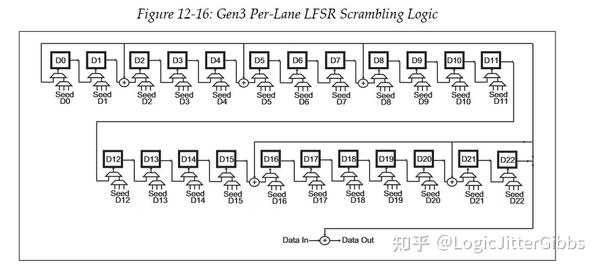

12.3.3.1.1 第一种选择:多个 LFSR

第一种选择:多个LFSR。一种解决方案是为每个通道实现一个单独的 LFSR,并用不同的起始值或 “种子” 来初始化每个通道。这具有简单和快速的优点,但代价是增加了逻辑数量。如图 12-16 所示,每个 LFSR 根据规范中给出的多项式 G(X)=X^23+X^21+X^16+X^8+X^5+X^2+1 创建一个伪随机输出。这个多项式比以前的版本要长,而且由于种子值的不同,通道之间的输出值也有一些不同。以 x8 通道为例,为每个通道分配的,共计八个不同的种子值需要八个不同的 LFSR,通道 0 到 7 各一个。

图 12-16 Gen3 各通道独立 LFSR 的加扰逻辑

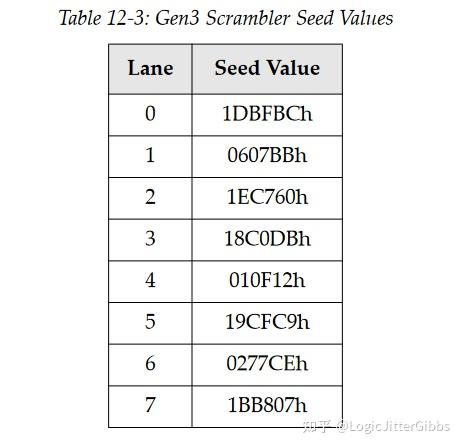

第 432 页的表 12-3 列出了每个通道的 24 位种子值。后续序列将重复先前的数值,这意味着通道 8 的种子值将与通道 0 相同,因此这里仅列出前 8 个值。每个通道使用相同的 LFSR 和相同的抽头(tap point)来创建加扰输出,使用不同的种子值来产生所需的差异。

表 12-3 Gen3 加扰种子值

12.3.3.1.2 第二种选择:单个 LFSR

第二种选择:单 LFSR:另一种解决方案只使用单个 LFSR,如第 433 页图 12-17 所示,图中展示的通道 2、10、18 和 26 共享的加扰逻辑,并通过将不同的抽头异或为各个通道创建加扰输入。由于只有一个 LFSR,所有通道的种子值是相同的(全 1, all ones),但每个通道的加扰 “抽头表达式(Tap Equation)” 是由不同的抽头组合而成的,如第 433 页的表 12-4 所示。该规范还指出,4 个通道的抽头表达式可以通过 XOR 它们的位邻的抽头值而得到。

• Lane 0 = Lane 7 XOR Lane 1(注意,需要比通道 0 更低的通道时,抽头规律是绕回的,因此 Lane 7 被认为是 Lane 0 相邻的低通道)。

• Lane 2 = Lane 1 XOR Lane 3

• Lane 4 = Lane 3 XOR Lane 5

• Lane 6 = Lane 5 XOR Lane 7

单 LFSR 解决方案使用的逻辑门数比多 LFSR 版本少,但 XOR 过程产生了额外的延迟,相较于多 LFSR 方案,提供了一个不同的成本/性能选择。

图 12-17 Gen3 使用单个 LFSR 的加扰逻辑

表 12-4 单 LFSR 方案抽头表达式

12.3.3.2 加扰规则

Gen3 加扰器 LFSR(无论是在一个还是多个 LFSR 方案中)并不会不断移位移位寄存器(advance),而只是根据正在发送的内容移位。加扰器必须定期重新初始化,每当检测到 EIEOS 或 FTSOS 时都会进行初始化。为方便起见,在本节总结规范中给出的以下几种加扰规则:

• 同步头位不会被加扰,也不会使 LFSR 中的码流。

• 当最后一个 EIEOS 符号被发送时,发送端 LFSR 被复位,当最后一个 EIEOS 符号被接收时,接收端 LFSR 被复位。

• TS1 和 TS2 有序集:

— 符号 0 不会被加扰

— 符号 1 至 13 被加扰

— 符号 14 和 15 可能会也可能不会被加扰。规范规定,如果有必要改善 DC 平衡,它们将绕过加扰,否则将加扰(关于如何保持 DC 平衡的更多细节,见第 510 页的“TS1 和 TS2 有序集”)。

• 有序集 FTS、SDS、EIEOS、EIOS 和 SOS 的所有符号都不会被加扰。尽管如此,输出的数据流将有足够的转换密度以允许时钟恢复,而且实现 DC 平衡,因为有序集本身的符号选择会实现上述两点。

• 即使旁路(bypassed)时,发送端也会将所有有序集符号移位至他们 LFSR 的码流中,除了 SOS 中的符号。

• 接收端也是这样做的,检查传入的有序集的符号 0,看它是否是 SOS。如果是的话,LFSRs 就不会移入该块中的任何符号。否则,LFSR 将移入该块中的所有符号。

• 所有的数据块符号被加扰并被移入 LFSRs。

• 符号是按小端顺序进行加扰,也就是说,这意味着最低有效位首先加扰,最高有效位最后加扰。

• 每个通道 LFSR 的种子值取决于 LTSSM 第一次进入 Configuration.Idle(已完成轮询状态)时分配给该通道的通道数。第 432 页的表 12-3 中显示了模数为 8 的种子值,一旦分配,只要 LinkUp=1,就不会改变,即使通道编号因为回到配置状态而已经被重新分配了。

• 与 8b/10b 不同,在使用 128b/130b 编码时,不能禁用加扰器,因为需要它来帮助实现信号完整性。如果没有加扰,预计链路将无法可靠运行,因此它必须始终处于使能状态。

• Loopback Slave 不得对回环(loope-back)位进行加扰或解扰。

12.3.4 串行器

这个移位寄存器的工作方式与 Gen1/Gen2 数据速率的工作方式类似,只是它现在一次接收 8 位,而不是 10 位(即,串行器是一个 8 位并行到串行移位寄存器)。

12.3.5 用于同步头位的多路复用器

最后,每个块中必须加入两个同步头位,使接收端能够区分下一个字符块是数据块还是有序集块。位于每一个 130 位块的前两位,同步头比特的相关逻辑可以添加到发送端中有设计意义的任何位置。在这本例中,为了简单起见,这些比特是在发送过程的最后注入的。无论他们包含在何处,上面的字节流必须停顿下来,以便为添加它们留出时间。在本例中,需要有一种方法来通知上述的逻辑暂停两个比特的时间。在发送同步位期间,传入的数据包流将在 Tx 缓冲区中排队。

12.4 Gen3 物理层接收逻辑

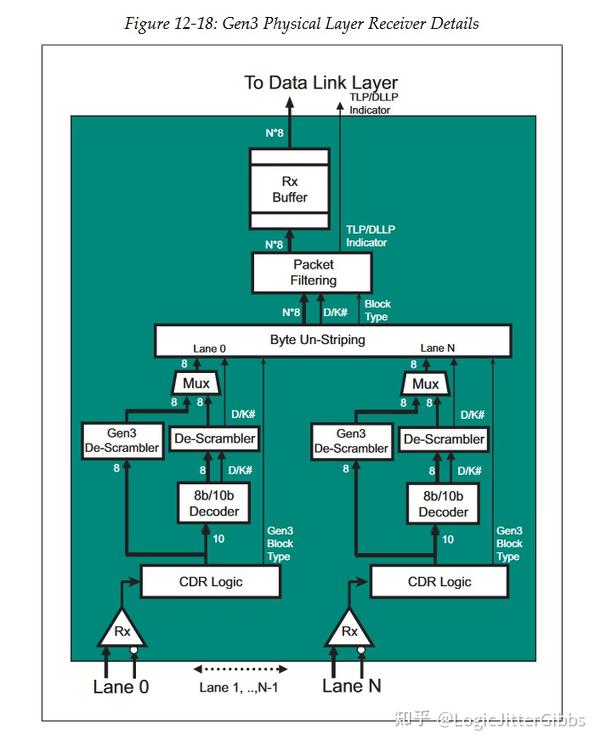

与前几代一样,如第 436 页图 12-18 所示,接收端的逻辑从 CDR(时钟和数据恢复,Clock and Data Recovery)电路开始。逻辑中可能包括 PLL,该 PLL 根据预期频率和比特流中的电平跳变锁定发送端时钟的频率,以产生恢复的时钟(RX 时钟)。这个恢复时钟将锁存输入数据到串并转换缓冲器中,在建立了块对齐后(在 LTSSM 的恢复状态下实现),另一个是 RX 时钟 8.125 分频的恢复时钟(RX Clock/8.125)将 8 位符号锁存到弹性缓冲器(Elastic Buffer)中。之后,解扰器从加扰的字符中重新恢复出原始数据。这些字节绕过 8b/10b 解码器,直接被送到字节拆分(Byte Un-striping)逻辑。最后,有序集被过滤出来,在物理层处理,剩下的 TLPs 和 DLLPs 字节流被转发到数据链路层。

在下面的讨论中,将从图 12-18 底部向上描述每个部分。重点是描述为 8.0GT/s 改变的物理层的各个方面。本节将不会描述那些相比 Gen1/Gen2 协议没有变化的子块。

图 12-18 Gen3 物理层接收逻辑详细框图

12.4.1 差分接收

差分接收端的逻辑没有变化,但有用于改善信号完整性的电气变化(参见第 468 页的 “信号补偿”),以及建立信号均衡的训练变化,这在第 577 页的 “链路均衡概述” 中有所介绍。

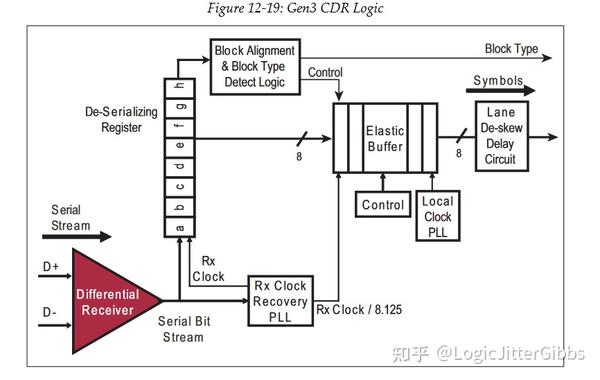

图 12-19 Gen3 CDR 逻辑

12.4.2 CDR(时钟和数据恢复)逻辑

12.4.2.1 RX 时钟恢复

尽管新的加扰方案有助于时钟恢复,但它并不能保证在短间隔内有良好的转换密度。因此,CDR 逻辑现在必须能够在没有那么多电平跳变边沿的情况下保持较长时间的同步。规范中没有给出实现这一目标的具体方法,但可能需要一个更鲁棒的 PLL(锁相环,Phas-Locked Loop)或 DLL(延迟锁相环,Delay-Locked Loop)电路。

CDR 逻辑的另一个不同之处在于,Gen3 弹性缓冲器使用的内部时钟并不像人们想象的那样,简单地将 RX 时钟 8 分频。显而易见的原因是 Gen3 输入数据不只是 8 字节的倍数。相反,它是一个 2 位的同步头,其后是 16 个字节。这额外的两比特必须在一些逻辑中进行处理。规范没有要求任何特定的实现,但一个解决方案是仍然将时钟除以 8.125,如第 437 页的图 12-19 所示,在 130 位时间内产生 16 个时钟边缘。

考虑到块类型检测逻辑始终需要提取出两比特同步头,对其进行检查,所以,可以在达到块边界时,使用块类型检测逻辑从串并转换器中取出额外的两位,以确保只有 8 位数据字节被传递到弹性缓冲区。

为了解决这个问题,8.0 GT/s 数据速率的内部时钟实际上是 8.0 GHz/8.125 = 0.985GHz。这导致比通常用来描述 Gen3 带宽的 1.0GB/s 数据速率略低,但差异很小(比 1GB/s 低 1.5%),所以通常不被提及。

12.4.2.2 串并转换器

如第 437 页图 12-19 所示,通过恢复的 RX 时钟将传入的数据采样到每个通道的串行-并行转换器中。8 位符号被发送到弹性缓冲器,并由 RX 时钟的另一个分频时钟锁存进弹性缓冲器,该时钟已经是 RX 时钟的 8.125 分频,以适应 130 比特块中的 16 字节数据。

12.4.2.3 实现块对齐

训练期间发送的 EIEOS 用于识别 130 位块的边界。如第 438 页图 12-20 所示,这个有序集可以在比特流中被识别出来,因为它是由 00h 和 FFh 的字节交替出现的数据模式组成。当识别这种数据模式时,EIEOS 的最后一个符号被认定为块的边界,通过测试接下来的 130 比特数据流,将显示当前提取的边界是否正确。如果不正确,逻辑就继续搜索 EIEOS 的特定数据模式。这个过程在规范中被描述为三个阶段:未对齐、对齐和锁定。

未对齐阶段。接收端在经过一段时间的电气空闲后进入这个阶段,例如改变速率至 8.0GT/s 或从低功率链路状态退出时。在这个阶段,块对齐逻辑观察 EIEOS 的到来,因为交替字节的结尾必须与块的结尾相对应。当看到 EIEOS 时,调整块边界以对齐,块对齐状态进入下一阶段:对齐阶段。在此之前,接收端还必须在接收到 SOS 后,根据 SOS 的内容,调整块对齐的边界。

对齐阶段。在这个阶段,接收端继续监测 EIEOS,并在看到 EIEOS 时对其位和块对齐边界进行任何必要的调整。然而,由于他们已经初步确定了块边界,他们现在也可以搜索 SDS(数据流的开始)有序集,作为数据流的开端。当看到 SDS 时,接收端就进入了锁定阶段。在此之前,它还必须继续在 SOS 到来时,调整其块对齐边界。如果检测到未定义的同步头(值为 00b 或 11b),接收端将被允许返回到未对齐阶段。规范指出,这将在链路训练期间发生,当 EIEOS 后面是一个训练有序集时(TS1/TS2)。

锁定阶段。一旦接收端达到这个阶段,它就不再调整其块对齐 边界。相反,它现在期望在 SDS 之后看到一个数据块,如果此时发现必须重新调整对齐,一些未对齐的数据可能会丢失。如果检测到未定义的同步头,则接收端将被允许返回到未对齐阶段。一旦数据流处理停止,接收端可以被指示从锁定阶段转换到其他阶段之一(关于数据流的规则,请参见第 413 页 “数据流和数据块”)。

特殊情况:环回。在讨论块对齐时,规范描述了当链路处于环回模式时的情况。环回主机(Loopback Master)必须能够在环回期间调整对齐,并允许发送 EIEOS,并在 Loopback.Active 状态期间,回传检测到的 EIEOS ,在其基础上调整其接收端。环回从机(Loopback Slave)必须能够在 Loopback.Entry 状态期间调整对齐,但不能在 Loopback.Active 状态期间调整对齐。当从机开始回环比特流时,从机的接收端被认为处于锁定阶段。

12.4.2.4 区块类型检测

一旦实现了块对齐,接收端就可以识别进入的块的起始时刻,并检查前两位,以确定当前块属于两种可能的类型中的哪一种。有序集块只对物理层有意义,所以它们不会被转发到更高的层,但数据块会被转发。当检测到同步头时,块类型信息被传递给物理层的其他部分,以确定是否应从转发给更高层的字节流中删除当前块。时钟恢复机制和同步头检测有效地完成了必须在物理层进行的,从 130 位到 128 位的转换。

请注意,由于每个通道的块信息是相同的,这个逻辑只需要在其中一个通道中实现,例如第 436 页图 12-18 中所示的通道 0。但是,如果支持不同的链路宽度和通道反转特性,那么更多的通道将需要包含该逻辑,以确保活动的通道始终有该逻辑可用。例如,能够作为通道 0 运行的每条通道都需要实现该逻辑,但只有当前作为通道 0 的通道需要使用它。还要注意的是,由于规范没有给出这方面的细节,这里讨论和说明的示例只是对可行实现的猜测。

12.4.3 接收端时钟补偿逻辑

12.4.3.1 背景

PCIe 8.0 GT/s 的时钟要求与早期规范版本相同:两个链路伙伴的时钟频率必须在中心频率的+/-300 ppm(百万分之一)范围内,这导致(在最坏的情况下)每 1666 个时钟就会获得或失去一个时钟周期。

12.4.3.2 弹性缓冲区的作用

如第 441 页图 12-21 所示,使用恢复的时钟将接收到的符号采样到弹性缓冲器中,并使用接收端的本地时钟打拍输出。弹性缓冲器和早先协议版本一样,通过添加或删除 SKP 符号来补偿频率差,但现在它一次添加四个符号,而不是一次仅添加一个符号。当 SKP 有序集到达时,监控缓冲器状态的控制逻辑会进行评估。如果本地时钟运行速度较快,缓冲区将接近下溢状态,逻辑可以通过在 SOS 到达时追加四个额外的 SKP 来补偿,以快速重新填充缓冲区。另一方面,如果恢复的时钟运行得更快,缓冲区将接近溢出状态,逻辑将通过删除四个 SKP 来补偿溢出情况,以便在看到 SOS 时快速排空缓冲区。

图 12-21 Gen3 弹性缓存逻辑

Gen3 发送端每 370 至 375 个块安排一次 SOS,但和早先协议版本一样,只能在块边界发送 SOS。如果在安排 SOS 时,有一个数据包正在传输,它们会被累积并在下一个数据包边界插入。然而,与较低的数据速率协议版本不同的是,在 8.0GT/s 下不允许有两个连续的 SOS。它们必须由用数据块隔开。接收端必须能够容忍由设备支持的最大数据包有效载荷大小分隔的 SOS。

事实上,仅以 4 个符号为增量进行调整,可能会影响到弹性缓冲区的深度需求,因为需要看到两个时钟之间差值大于 4,才会应用补偿,而一个大的数据包可能正在进行传输,占用了本来是适当进行补偿的时间。由于这个原因,需要谨慎确定这个缓冲区的最佳尺寸。所以,让我们考虑一个例子。在每块 16 个符号的情况下,375 块的 SOS 之间允许的时间等于 6000 个符号时间。将其除以最坏情况下获得或失去一个时钟的时间 1666,意味着在此期间最多可以获得或失去 3.6 个时钟。如果一个长度最大的 TLP(4KB)传输正好是在下一个 SOS 发送之前开始的,那么对于一个 x1 链路来说,它的整体延迟大约是 6000+4096=10096 符号时间,这意味着将获得或失去 10096/1666=6.06 时钟。因此,如果支持 4KB 大小的 TLP,缓冲器可能被设计成在保证 SOS 到达之前,能够处理 7 个过多或过少的符号。可能发生的情况是,在第一个 SOS 被发送之前,已经安排了两个 SOS。在较低的数据速率下,排队的 SOS 是背对背发送的,但对于 8.0GT/s 来说,它们不会被连续发送,必须用一个数据块隔开。每当 SOS 到达接收端时,它可以添加或删除 4 个 SKP 符号,以快速填充或耗尽缓冲区,避免出现问题。

12.4.4 通道与通道之间的偏斜

12.4.4.1 通道间的飞行时间差异

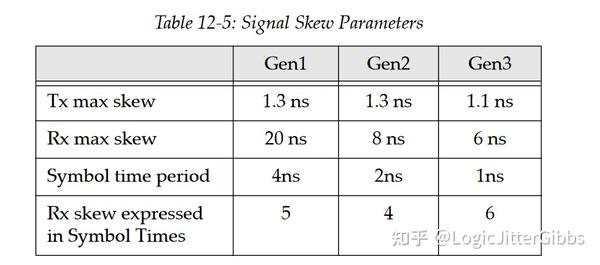

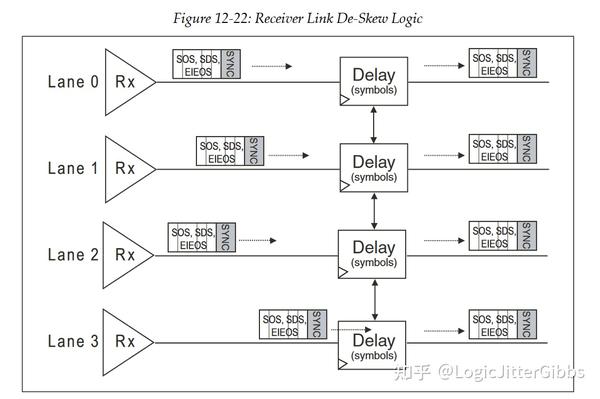

对于多通道链路,通道之间数据的到达时间差异,将在接收端被自动纠正,延迟较早到达的通道上的数据,直到最晚通道上的数据到达,以使所有通道的数据到达时间相同。该规范允许设计者以他喜欢的任何方式来实现去偏斜。但是如果在弹性缓冲器之后,使用数字延迟逻辑来实现去偏斜有一个好处,即到达时间差异此时已经被采样为接收端的本地符号时钟。如果在某个时钟边沿,一个通道的输入数据到达,而另一个通道的输入数据则没有,那么它们之间的差异将可以用若干个时钟周期来衡量,所以早到的通道可以简单地延迟适当数量的时钟周期,使其与晚到的通道保持一致(见第 444 页的图 12-22)。事实上,接收端的最大允许偏斜量是以时钟周期的倍数来衡量的,采用这一方案使衡量最大允许偏斜量指标变得容易,并推断出规范编写者可能倾向于这种实现方式。正如规范中所定义的那样,对于 Gen1(5 个符号时间的时钟,每个符号 4ns)和 Gen2(4 个符号时间的时钟,每个符号 2ns),接收端去偏斜(de-skewing)能力必须支持 20ns 偏斜, Gen3(6 个符号时间的时钟,每个符号 1ns)则是 6ns。

12.4.4.2 去偏斜的契机

必须在所有通道上同时看到相同的符号才能执行去偏斜,任何有序集都可以。然而,去偏斜只在 L0s、恢复(Recovery)和配置(Configuration)LTSSM 状态下执行。特别是,它必须是以下状态转移的必要条件:

• 离开 Configuration.Complete

• 离开 Configuration.Idle 或 Recovery.Idle 后开始处理数据流

• 离开 Recovery .RcvrCfg

• 离开 RX_L0s.FTS

如果偏斜值在 L0 状态下发生变化(例如,基于温度或电压变化),则可能会发生接收端错误并导致重放 TLP。如果问题持续存在,链路最终将转换到恢复状态,并在那里进行去偏斜处理。规范指出,虽然设备在 L0 状态下不允许对其链路进行去偏斜,但在此状态下必须定期发送的 SOS 包含 LFSR 值,目的是帮助外部工具完成这一工作。这些工具不受数据流规则的限制,可以搜索 SOS,并使用其数据模式来实现数据流中的位锁定、块对齐和通道间的去偏斜。

规范指出,当离开 L0s 时,发送端将发送一个 EIEOS,然后是正确数量的 FTS,并在每 32 个 FTS 后插入另一个 EIEOS,然后是最后一个 EIEOS,以协助块对齐,最后是一个 SDS 有序集,目的是启动数据流外,以及用于去偏斜。

14.4.4.3 接收端通道间的去偏斜能力

可以理解的是,发送端只允许引入最小的偏斜量,以便将剩余的偏斜预算用于覆盖走线差异和其他变化。接收端可校正的允许偏差量如第 443 页的表 12-5 所示,可以看出,这种偏差很容易与 Gen3 的符号次数相对应,就像早期数据速率一样。这使得可以选择在弹性缓冲器之后使用延迟寄存器来完成去偏斜,与先前章节中的 Gen1/Gen2 物理层实现一致。

表 12-5 信号偏斜参数

当使用 8b/10b 编码时,一种明确的去偏斜机制是监视 COM 控制字符,它必须同时出现在所有通道上。128b/130b 没有这个选项,但有序集仍然需要同时出现在所有通道上,如 SOS、SDS 和 EIEOS。因此,尽管在对通道进行去偏斜时要寻找的数据图样不同,但过程可以是相同的。

图 12-22 接收端去偏斜逻辑

12.4.5 解扰器

12.4.5.1 综述

接收端遵循与发送端完全相同的加扰多项式生成规则,并简单地将相同的值再次与输入数据进行 XOR 以恢复原始信息。与发送端一样,他们可以为每个通道实现一个单独的 LFSR,或者只实现一个。

12.4.5.2 禁用解扰

与 Gen1/Gen2 数据速率不同,在 Gen3 模式下,不能禁用解扰,因为它在促进时钟恢复和信号完整性方面起着重要作用。在较低的速率下,TS1 和 TS2 控制字节中的“禁用加扰” 位被用来通知链路邻居加扰特性被关闭。在 8.0GT/s 以及更高的速率该位是保留不使用的。

12.4.6 字节拆分(Byte Un-Striping)

这个逻辑与 Gen1 或 Gen2 的实现基本相同。在某些时候,Gen3 的字节流和较低数据速率的字节流必须混合在一起,第 445 页图 12-23 中的示例显示了在拆分(un-striping)逻辑之前发生的情况。

12.4.7 数据包过滤

由字节拆分(un-striping)逻辑提供的串行字节流包含 TLPs、DLLPs、逻辑空闲(IDLs)和有序集。逻辑空闲字节和有序集在这里被消除,不被转发到数据链路层。剩下的是 TLPs 和 DLLPs,它们与数据包类型的指示符一起被转发。

12.4.8 接收缓冲区(RX Buffer)

RX 缓冲区保存收到的 TLPs 和 DLLPs,直到数据链路层能够接收它们。规范中没有描述数据链路层的接口,因此设计者可以自由选择总线宽度等细节。通道越宽,时钟频率就越低,但需要更多的信号和逻辑来支持它。

12.5 关于 128b/130b Loopback 的注意事项

规范特别说明了环回模式在更高速率下的操作。基本规则可以归纳如下:

• 环回主机(Loopback master)必须发送实际的有序集或数据块,但在从数据块变为有序集时,他们不需要遵循正常的协议规则,在有序集变成数据块时反之亦然时。换句话说,SDS 有序集和 EDS 标记不是必需的。从机必须不期望或检查它们的存在。

• 主机必须像往常一样发送 SOS,并且必须允许环回流中的 SKP 符号数量不同,因为接收端将进行时钟补偿。

• 允许环回从机通过一次添加或删除 4 个 SKP 符号来修改 SOS,就像他们通常为时钟补偿所做的那样,但产生的 SOS 仍必须遵循正确的格式规则。

• 除了 SOS 和 EIEOS 之外,所有内容都应该完全按照发送时的情况环回,因为 SOS 可以像刚才描述的那样发生变化,而 EIEOS 和 EIOS 在环回中都有明确的用途,应该避免使用。

• 如果从机无法获取块对齐,它将无法按照收到的所有位进行环回,并允许根据需要添加或删除符号以继续操作。

原文: Mindshare

译者: Brook

校对: LJGibbs

转载自:知乎

推荐阅读

- 《PCI Express Technology 3.0》物理层逻辑(Gen3)1-2 节

- DDR 学习时间 (Part Z - 1):芯片设计中的 DDR 模型杂谈

- PIPE v3.0 协议信号速览表

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

更多招聘及面经请关注FPGA的逻辑,欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。