目录

引言

关于前一章

上一章描述了物理层与链路之间的电气接口,包括差分发送端与接收端的一些特性的细节。同时也讨论了信号均衡的需求以及均衡的方法。上一章的讨论包括了 Gen1, Gen2 和 Gen3 速率下的差分发送与接收端的特性。

关于本章

本章讨论物理层链路训练与状态状态机(LTSSM, Link Traning and Status State Machine)的行为,包括从上电或者复位开始,到链路进入正常工作状态(L0),报文流量开始的整个初始化过程。此外,本章还将讨论链路电源状态 L0s,L1,L2,L3 以及这些状态之间的转换。本章也会讨论链路恢复状态(Recovery)中,重新完成位锁定(Bit Lock)、符号锁定(Symbol Lock)或者块锁定(Block Lock)的过程。最后,还讨论了用于链路带宽管理的链路速率以及位宽转换。

关于下一章

下一章将讨论 PCIe 端口或者链路中存在的错误类型,如何检测、报告这些错误,以及这些错误的处理选项。因为 PCIe 设计中后向兼容了 PCI 的错误报告机制,所以将首先介绍 PCI 的错误处理机制作为背景知识。然后我们将关注于PCIe 对于可纠正、非致命以及致命错误的处理机制。

14.1 总览

链路初始化和训练是由物理层控制的,基于硬件 (而非软件) 的过程。该过程配置和初始化设备的链路和端口,使链路上能够进行正常的数据报文通信。

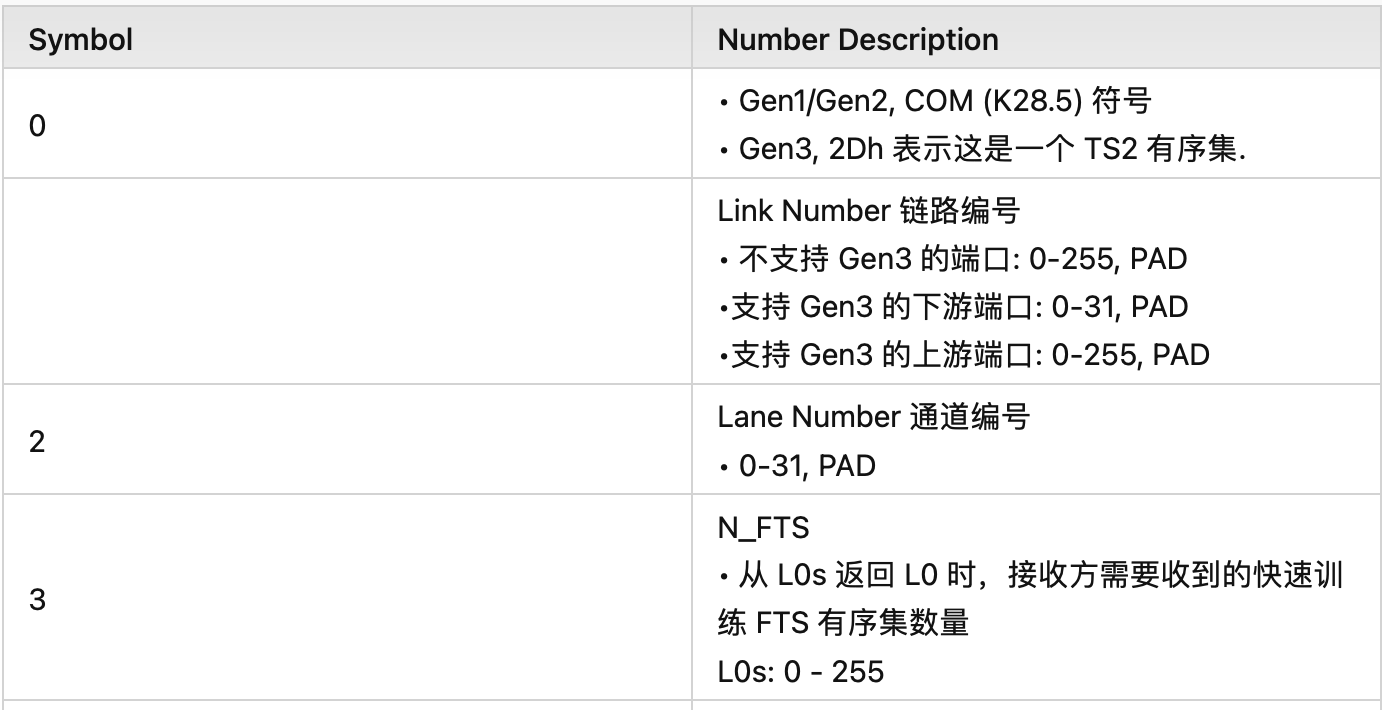

图 14-1 LTSSM 在 PCIe 架构中所处的位置

完整的训练过程在复位后由硬件自动启动,并由 LTSSM 管理,如 506 页图14-1 所示。

在链路初始化和训练过程中包括了几项步骤。让我们思考下它们都有哪些作用,并提前引入一些术语。

- 位锁定,Bit Lock:当链路训练开始时,接收端的时钟尚未与接收信号的发送时钟同步,无法可靠地采样输入信号的数据比特。在链路训练期间,接收端的时钟和数据恢复(CDR,Clock and Data Recovery)逻辑通过使用数据比特流作为时钟的参考信号,来重建发送端的时钟。一旦从数据流中恢复了时钟,就可以说接收端已经完成了位锁定,然后能够正确地采样输入数据比特。有关位锁定机制的更多信息,可以参阅第 395 页的 “实现位锁定”。

- 符号锁定,Symbol Lock:对于8b/10b编码 (Gen1/Gen2) 而言,训练的下一步是进行符号锁定。同位锁定类似,虽然接收端目前可以识别单个比特,但是不知道由 10 个比特组成的符号的边界在哪里。当发送端和接收端交换训练有序集 TS1 和 TS2 时,接收端在比特流中搜索可识别的数据图样(pattern)。通过查找 COM 符号的位置可以较为简单地实现这一点。COM 符号独特的编码使得它很容易识别,识别 COM 字符后,接收方不但定位到了两个符号之间的边界,而且也能定位到两个有序集之间的边界(译注:因为有序集 TS1/TS2 以 COM 字符作为开端)。有关这方面的更多信息,参见第 396 页的 “实现符号锁定”。

- 块锁定,Block Lock:对于8.0 GT/s(Gen3) 所使用的块锁定,处理过程与符号锁定略有不同,因为没有使用8b/10b 编码方案,所以也就不存在 COM 字符。然而,接收端仍然需要在接收比特流中找到可识别的报文边界。解决方案是在训练有序集中包含更多的电气空闲退出有序集( EIEOS,Electrical Idle Exit Ordered Set),用于定位边界。可以通过查找 00h 和 FFh 字节交替的数据图样来找到 EIEOS ,并且 EIEOS 的位置定义了块之间的边界,因为根据协议,当该有序集结束后,下一个块必须紧随其后开始。

- 链路宽度,Link Width:具有多个通道的 PCIe 设备可以使用不同的链路宽度。例如,具有 x2 端口的设备可以与 x4 端口的设备连接。在链路训练期间,两台设备的物理层会测试链路,并将链路宽度设置为两者能接受的最大值。

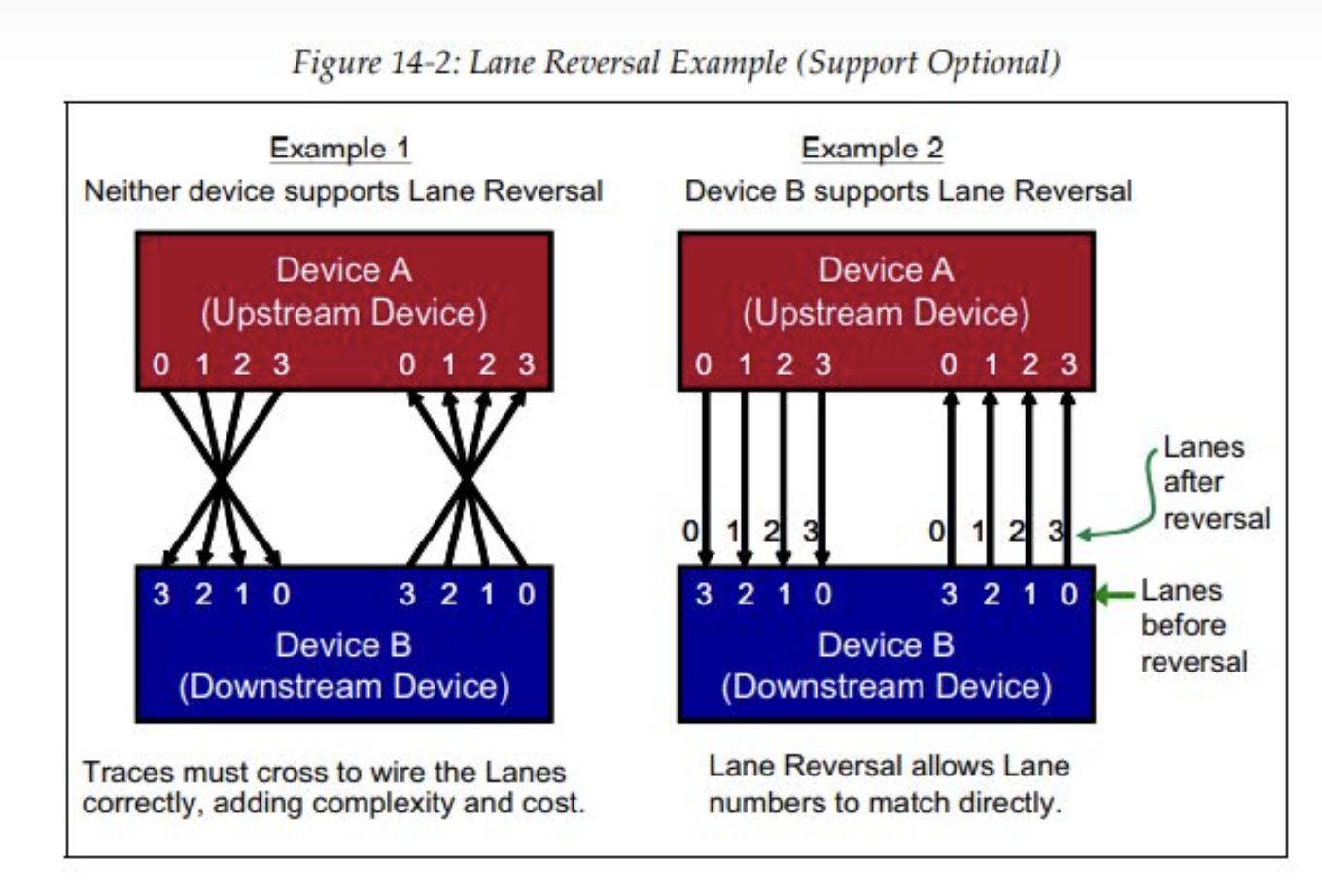

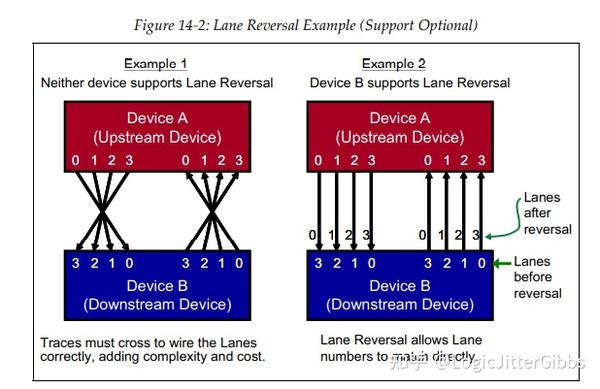

- 通道翻转, Lane Reversal:设备端口上的多个通道从 0 开始,按递增顺序编号。通常来说,端口的通道 0 同样连接到对端的通道 0,通道 1 连接到通道 1 ,依此类推。

然而,有时我们希望能够在逻辑上,颠倒各个通道间的编号,以简化 PCB 布线。并且能够允许各个通道间的连接走线不必交叉(参见第 508 页的图 14-2)。只要其中一个 PCIe 设备支持通道编号反转功能,就可以颠倒通道的连接关系,这是一项可选功能。

通道连接颠倒的情况是在链路训练期间检测到的,其后,其中一台设备必须在内部颠倒其通道编号才能使链路正常工作。由于规范没有强制要求支持此功能,电路板设计人员需要保证系统中至少有一个设备支持此功能,才能颠倒通道顺序布线。

图 14-2 通道翻转示例(可选支持特性)

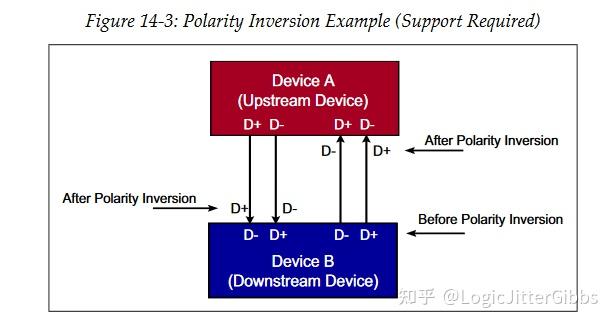

- 极性反转,Polarity Inversion:两端设备间的 D+ 和 D- 这一对差分信号互相之间是支持反接的(译注:即将 D+ 与对端 D- 连接,而不是 D+),为了在有必要的时候简化 PCB 的布局和连线。任何接收端都需要单独地检查差分信号的连接情况,并在极性翻转的情况下,在训练期间自动纠正,如图 14-3 所示。接收端通过检测输入 TS1 和 TS2 的符号 6-15 来实现这一点。如果接收端在 TS1 中收到了 D21.5 而不是预期的 D10.2(译注:),或者在 TS2 中收到了 D26.5 而不是预期的 D5.2,这代表当前通道差分对极性反转,需要进行纠正。与通道翻转不同的是,极性反转纠正是一项必须的特性,而不是可选的。

图 14-3 极性反转示例(可选支持特性)

- 链路数据速率,Link Data Rate: 在复位后,链路初始化与训练状态机总是会先将数据速率设置为默认的 2.5Gbit/s,以实现对第一代协议的后向兼容(第一代协议速率为 2.5Gbit/s)。如果链路宣称可以实现更高的速率,那么在训练时双方会通告自己支持的最高速率,完成训练后,LSTTM 会自动重新进行一次过程更短的训练,将链路速率改变为双方都支持的最高速率。

- 多 lane 间信号去偏移,Lane‐to‐Lane De‐skew: 各个通道之间的传输线长度差异或者其他因素,会导致多通道链路中原本同时传输的多个并行比特,到达接收方的时间有所差异,这被称之为信号偏斜(signal skew)现象。接收方需要通过延迟较早到达的通道,以对齐所有通道上的信号的到达时间,补偿通道之间信号传输快慢差异。在协议规定的可允许的信号偏移范围内,(对于 2.5Gbps 速率来说,最大信号偏斜是 20ns),接收方需要能够自动对偏移进行补偿。多通道间信号偏移补偿机制能够帮上 PCB 设计者一个大忙,因为他们不再需要设置复杂精细的约束,走出非常精确的等长信号传输线,有时候这是很难的。信号偏移补偿机制和极性翻转以及通道翻转机制一起,可以很大程度上简化高可靠的高速 PCIe PCB 设计。

14.2 链路训练中的有序集

14.2.1 概要

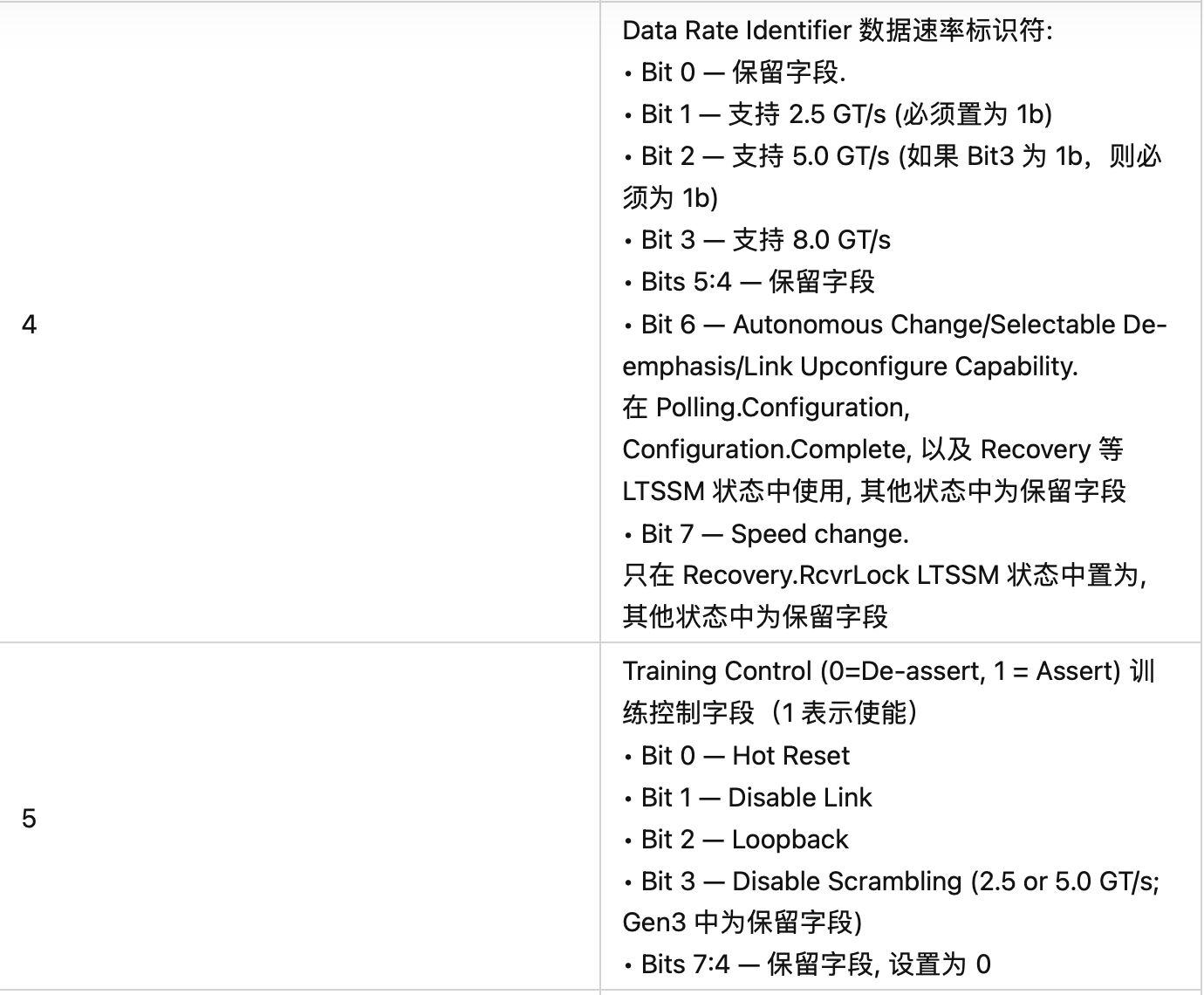

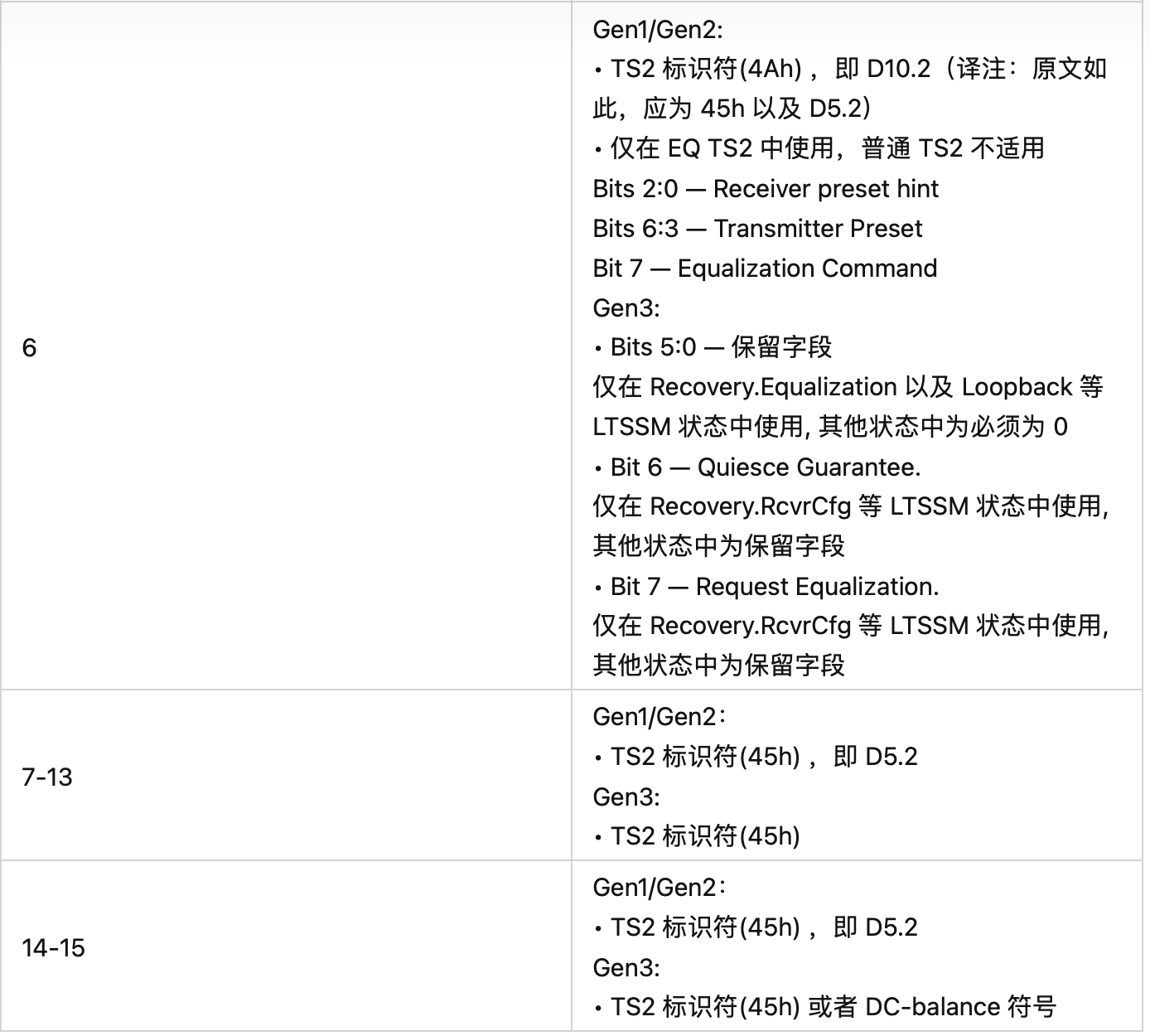

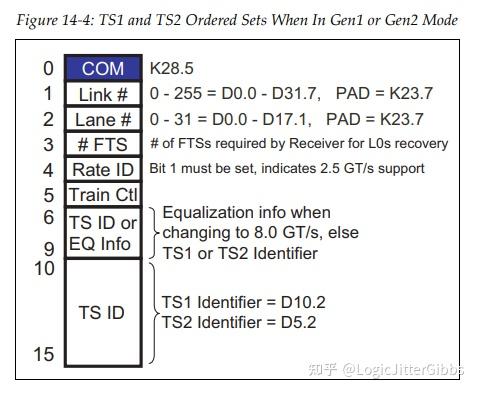

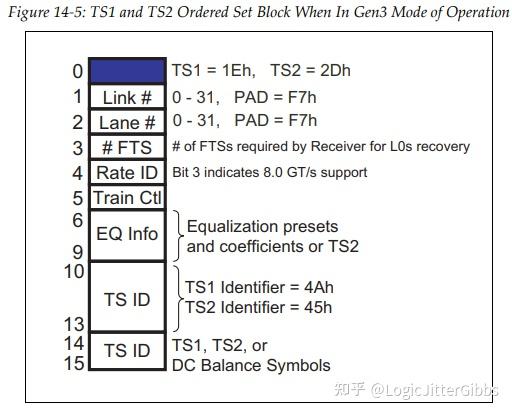

我们已经在本书 11 章的 “有序集” 这一节讨论过物理层所有不同类型的有序集。在训练过程中涉及到的物理层有序集包括训练有序集 TS1 以及 TS2 。图 14-4 中是 Gen1 以及 Gen2 模式下的有序集格式。图 14-5 是 Gen3 模式中所使用有序集的格式。接下来我们来进一步详细讨论他们。

图 14-4 Gen1/Gen2 中的 TS1/TS2 格式

14.2.2 TS1 以及 TS2 有序集

从图中 14-4 中可以看到,TS1/2 由 16 个符号(译注:字节)组成。在 LTSSM 的轮询、配置以及恢复状态中,通信双方会交换 TS1/2 有序集,本文会在后续的 LTSSM 章节详细讨论,后文分别在表 14-1/14-2中,用表格的形式描述了 TS1/2 16 个符号的具体含义。

为了便于理解和行文,以下用 Gen1 表示速率为 2.5GT/s 的情况,Gen2 表示速率为 5GT/s 的情况,Gen3 表示速率为 8GT/s 的情况。另外值得注意的是,在低速率中,Link 以及 Lane 字段中的填充字符(PAD character)使用 K23.7 ,而在 Gen3 中使用的是 F7h。我们后续的讨论中不会特别提及两者的差异,而统一表示为填充字符,因为这不重要。

图 14-5 Gen3 中的 TS1/TS2 格式

表 14-1 TS1 有序集内容汇总

读者可能会对符号 6 中的 EQ TS1 部分感到疑惑:既然只有 8GT/s 速率支持均衡,为什么较低的速率也会用到 EQ TS1? 他们其实是给那些支持 Gen3 但是当前工作在较低速率,并且想切换到 8GT/s 的通道传递 EQ 值用的。关于这部分的更多细节,以及 Gen3 均衡过程相关的内容,可以参阅本章 “链路均衡概览” 一节,原文 577 页。

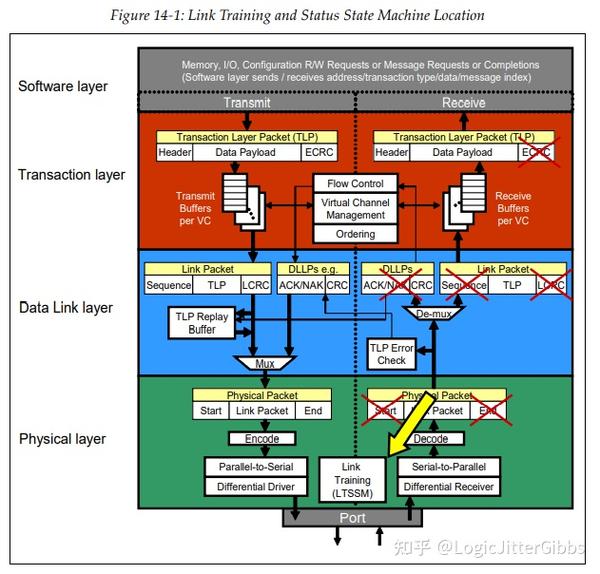

表 14-2 TS2 有序集内容汇总

表 14-1/14-2是 TS1 和 TS2 格式的大致描述,接下来我们仔细讨论下每个字段的含义。

- Symbol 0:

- Gen1/2,所有有序集的首个符号都是 K28.5(COM) 字符。接收方通过 COM 字符实现符号锁定(译注:即接收方通过正确接收的 COM,确认符号的边界)。因为 COM 字符需要同时出现在所有通道上,因此可以用于多通道间信号去偏斜。

- Gen3,有序集所在的 Block 之前是 2 比特同步头,同步头之后的首个符号用于表示有序集的类型。TS1 的首个符号是 1Eh, TS2 首个符号是 2Dh。

- Symbol 1(Link #):链路编号,在轮询状态中使用填充字符填充,其他状态中为链路被分配的编号

- Symbol 2(Lane #):通道编号,在轮询状态中使用填充字符填充,其他状态中为通道被分配的编号

- Symbol 3 (N\_FTS): 表示当前链路速率下,接收方从 L0s 电源状态退出返回 L0 状态所需要接收的快速训练序列(FTS)数量。在退出 L0s 状态时,发送方至少会发送 N\_FTS 个 FTS。这一过程所需的时间取决于所需 FTS 的数量以及当前的链路速率。举例来说,2.5GT/s 速率下,每个符号的发送时间为 4ns,所以如果需要 200 个 FTS,那么就是 200 FTS * 每个 FTS 4 个符号 * 4ns = 3200 ns。如果发送方置位了扩展同步比特,那么将发送 4096 个 FTS,发送这么多 FTS 是为了给外部链路观测工具建立比特同步和符号同步留出足够的时间,因为有些外部工具同步所需的时间比较长。

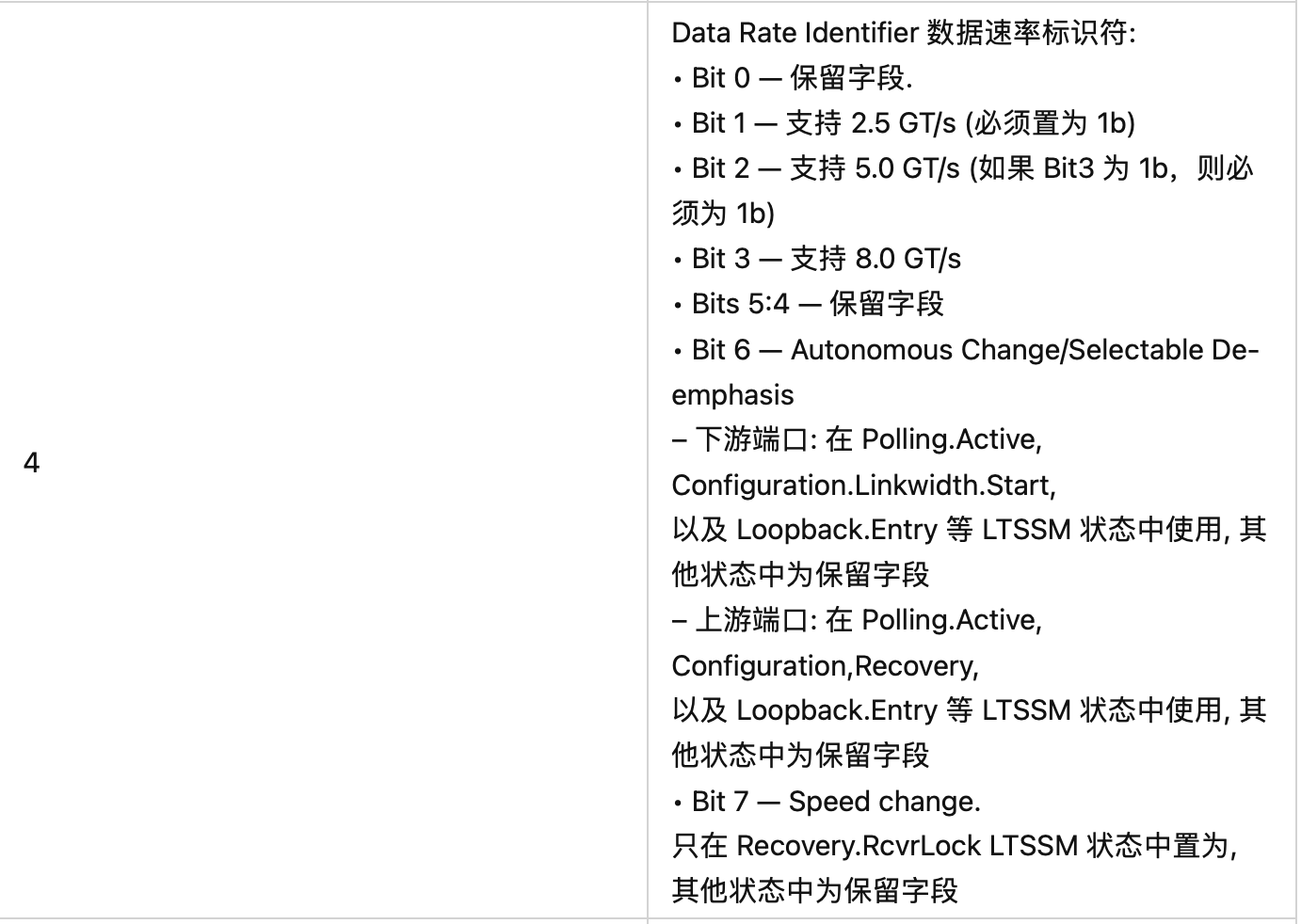

- Symbol 4 (Rate ID): 设备报告其所支持的数据速率,以及一些提供给由硬件发起的带宽改变功能的信息。所有设备必须支持 2.5GT/s 速率,并且链路在复位后始终会自动被训练为 2.5GT/s 速率,所以任何新的设备都需要后向兼容这个速率。如果设备支持 8GT/s 速率,那么它也需要支持 5GT/s 速率。此外,这个符号中还包括的其他信息有:

- Autonomous Change:当该比特置为 1 时,任何带宽改变的请求都是基于电源管理方面的原因而发起的。如果在发出带宽改变请求时,该比特未置为 1,那么代表设备在较高的速率或者较宽的链路上检测到工作不稳定的情况,需要改变带宽配置(降低速率或者减小链路宽度)来解决这些问题。

- Selectable De‐emphasis

- 上游端口(Upstream Ports)设置该域表示他们在 5GT/s 速率下期望的去加重水平设置,具体的预期设置取决于实现。在 Recovery.RcvrCfg 状态中,设备锁存接收到的该域的值,存放在设备内部。(协议描述中,这个值会被保存在一个名为 select\_deemphasis 的变量中)

- 下游端口(Downstream Ports)和根节点端口(Root Ports):在 Polling.Compliance 状态中,基于接收到的该比特数值,设置 select\_deemphasis 变量。在 Recovery.RcvrCfg 状态中,发送端设置发送的 TS2 中的该比特信息,数值基于 Link Control 2 寄存器相关比特。由于该寄存器的初始值是由硬件初始化的,所以预期需要在上电阶段后通过固件配置恰当的数值,或者将其硬件初始化值设置为一个保守但是安全(Strapping)的数值。

- 在 5.0 GT/s 回环模式中,从机去加重水平数值由主机发送的 TS1 中的对应比特设置。

- Link Upconfigure Capability:该域表示了一个较宽的链路在减少链路宽度后,是否有能力重新恢复原先较宽的链路宽度。如果在 Configuration.Complete 状态中,双方设备都报告自己具有这个能力,那么就做为一项共识记录下来。(比如将内部的一 upconfigure\_capable 比特置位)

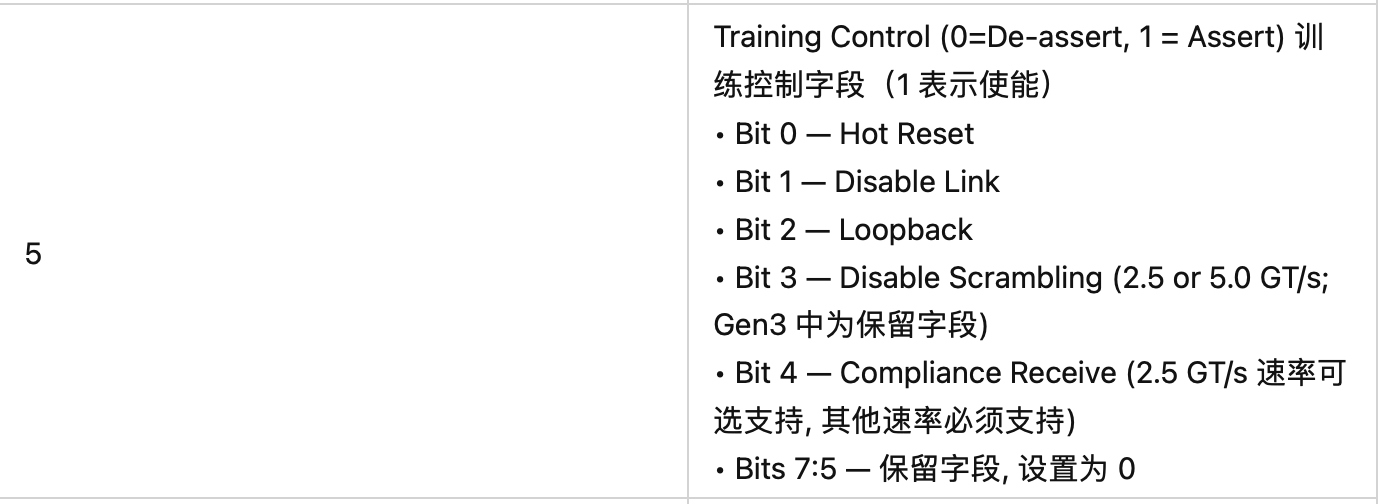

- Symbol 5 (Training Control): 交流链路双方的一些特殊情况,比如进行一次热复位(Hot Reset),使能回环模式,关闭链路或者关闭加扰。

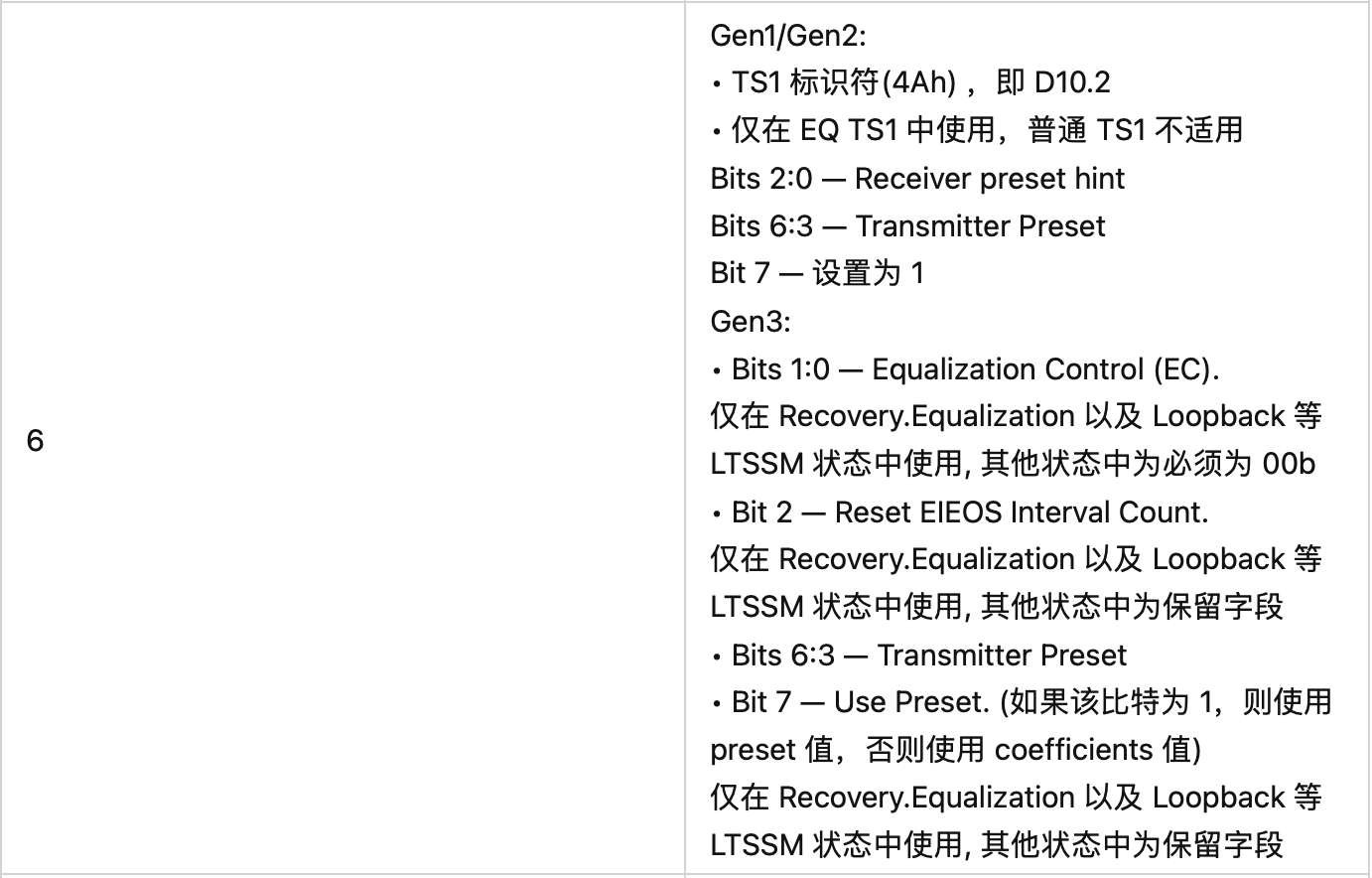

- Symbols 6‐9 (Equalization Control):

- Gen1/Gen2,符号 7-9 仅仅是 TS1 或者 TS2 的标识符,符号 6 通常也只是标识符,此时符号 6 比特 7(Use Preset 域) 为 0 。但是,如果这一比特为 1,那么代表当前的有序符号集是一个下游端口(DSP,面向下游的端口,比如 RC 的端口)发送的 EQ TS1 或者 EQ TS2。其中 ”EQ“ 代表均衡(Equalization),发送 EQ TS1/TS2 意味着链路速率将被提高为 8GT/s,此时上游端口(USP,面向上游的端口,比如 EP 的端口)需要知道当前使用的均衡参数。在 EQ TS1 和 TS2 中,符号 6 提供给 USP 的信息包括发送端预设集选择(Preset)以及接收端预设集选择提示(Preset Hint)。支持 8GT/s 速率的端口需要能够接收任意的 TS 类型(包括普通 TS 以及 EQ TS),但是如果端口不支持 8GT/s 速率,则不需要接收 EQ TS 的能力。可能的预设集数值列在原文 579 和 580 页的表 14-8 和表 14-9 中。

- Gen3,符号 6-9 提供均衡过程所需的预设集选择数值以及参数。TS2 的符号 6 的比特 7 (Request Equalization 域)现在被 USP 用于申请重新进行均衡。此时,符号 6 的比特 6 ( Quiesce Guarantee 域)可能也需要被置起,表示只要重新均衡的速度够快,那么所耗费的时间不会导致诸如完成包超时等问题(返回 L0 的时间在 1ms 以内)。在有些场景会使用到这个功能,举个例子,如果在使用均衡得到的设置时检测到了问题。 DSP 可以使用比特 6 和 7,要求 USP 来发起重新均衡的请求,并保证重新均衡不会带来副作用,尽管 USP 不需要对此做出回复。(译者:没有太明白这个例子)如果想了解更多均衡过程,请参阅原文 577 页的 “链路均衡概览” 一节。

- Symbols 10‐13 : TS1 或者 TS2 标识符

- Symbols 14-15 (DC Balance):

- Gen1/Gen2,仅仅是 TS1 或者 TS2 的标识符,因为 DC 均衡已经由 8b/10b 编码完成。

- Gen3,这两个符号的数值基于本通道上 DC 均衡的需要。发送方必须在每个通道上独立地追踪当前所有正在被发送的加扰后的 TS1 或者 TS2 的实时 DC 均衡(Running DC Balance)情况。实时 DC 均衡(Running DC Balance)是指目前发送的 1 和 0 之间的数量差,各个通道必须能够在收发两个方向上追踪 0 和 1 的数量差值,最大支持的差值为 511。这些计数器在记满后保持不变,但是会更新差值减小的变化。举例而言,如果计数器记录到发送的 1 数量比 0 多 511 个,此后无论发送多少个 1,计数值仍然停留在 511。然而,如果发送了 2 个 0,那么计数器会减少到 509。在发送 TS1 或者 TS2 时,符号 14 和 15 的数值由以下算法决定:

- 如果在符号 11 结束时, DC 均衡差值 > 31,如果发送的 1 数量更多,那么符号 14 = 20h,符号 15 = 08h。如果发送的 0 数量更多,那么符号 14 = DFh,符号 15 = F7h。

- 如果 DC 均衡差值 > 15,那么符号 14 = 正常的 TS1 或者 TS2 标识符,符号 15 = 08h 以减少 1 的数量,或者符号 15 = F7h 以减少 0 的数量。

- 其他关于 Gen3 DC 均衡的注意事项:

- DC 均衡计数器将在退出电气空闲状态时,或者在一个数据块之后收到 EIEOS 时复位。

- DC 均衡符号将绕过加扰,来保证发送的是预期的符号。

- *

原文: Mindshare

译者: LJGibbs文章来源:https://zhuanlan.zhihu.com/p/571308775

《PCI Express Technology 3.0》翻译系列

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3 节(完)

- PCI Express Technology 3.0:PCIe配置概述 3.1-3.7 节

- PCI Express Technology 3.0:PCIe配置概述 3.8-3.14 节(完)

- PCI Express Technology 3.0:地址空间与事务路由4.1-4.2节

- PCI Express Technology 3.0:地址空间与事务路由 4.3-4.4节

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。