AXI4S视频IP介绍及系统设计指南(一)

本文主要介绍使用AXI4S(AXI4-Stream)接口的视频IP细节。

介绍

本文总结了AXI4S接口视频协议,该协议在视频IP中的应用,其中AXI协议参考:

https://docs.xilinx.com/v/u/en-US/ug1037-vivado-axi-reference-guide

对于做过BT.1120总线的,这部分学习起来一点问题没有,只不过信号名称稍微修改了一下。

1.1 AXI4-Stream 信号接口

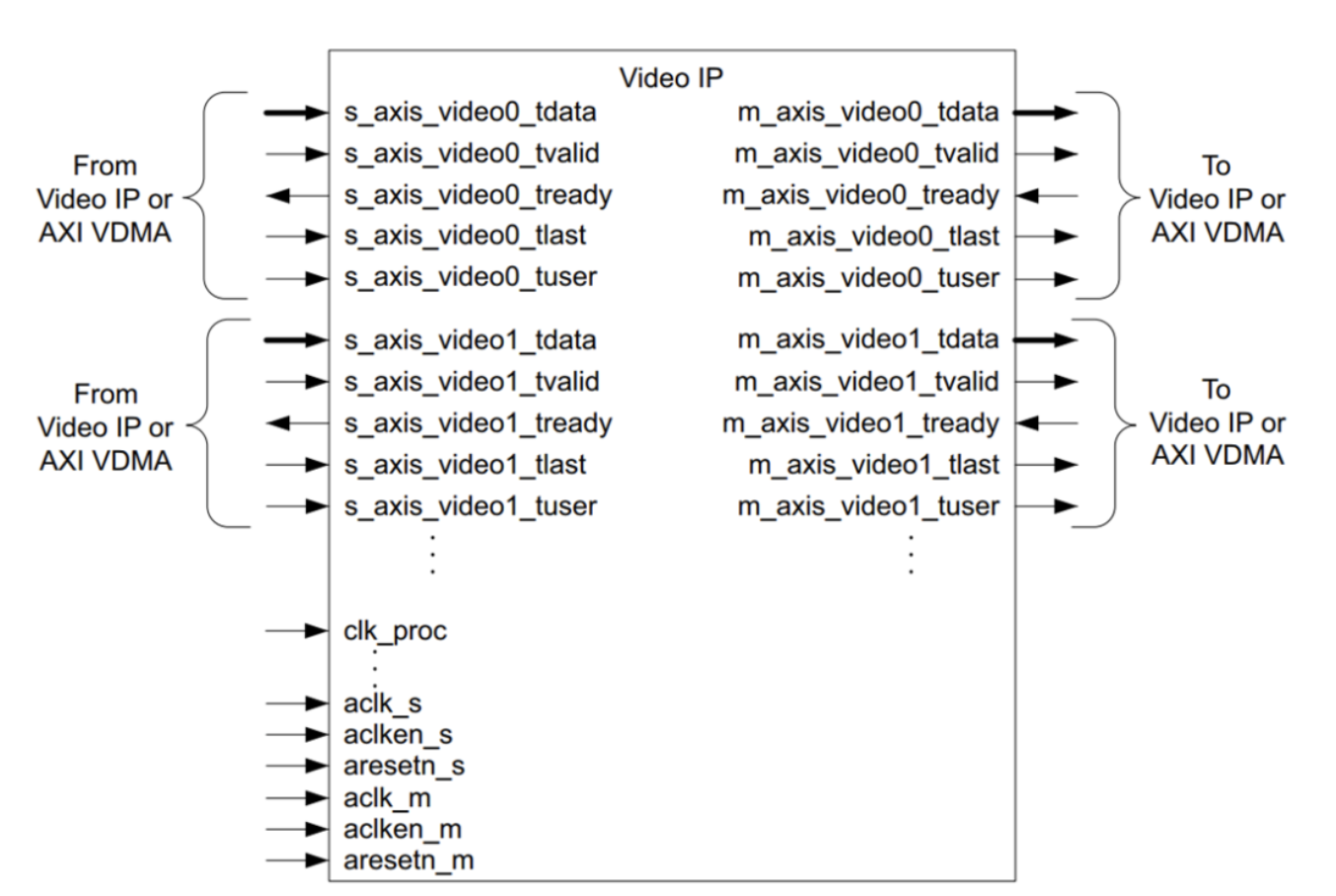

AXI4S携带实际的视频数据(无行场消隐),由主机和从机接口驱动,如Figure 1-1所示。

Figure 1‐1: 具有多个AXI4S从(输入)和主(输出)接口的视频IP

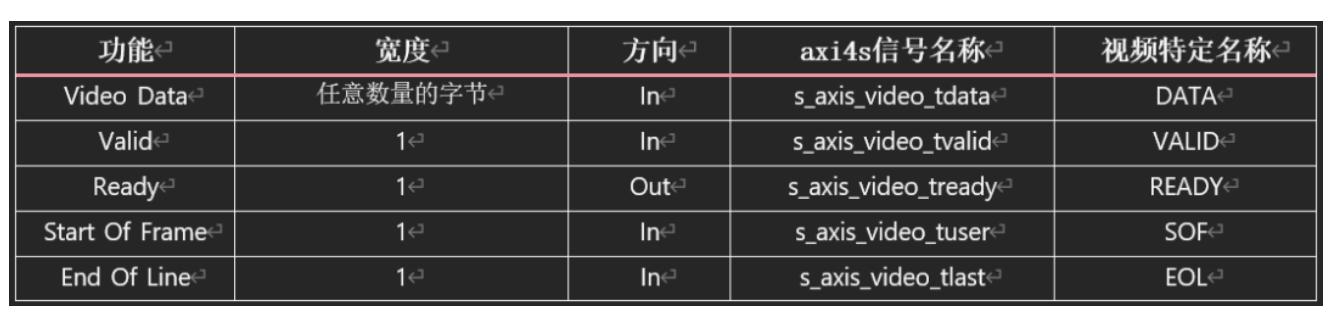

空白时段(行场消隐)、音频数据和辅助数据包不会通过AXI4-Stream上的视频协议传输。Table 1-1 和Table 1-2 中列出AXI4S接口视频IP需要的所有信号。

Table 1-1 显示了输入(从)侧连接器的接口信号名称和功能。为了避免命名冲突,对于具有多个AXI4S输入接口的IP,信号前缀s_axis_video应该附加到s_axis_videok,其中k是各个输入AXI4S的索引;例如,对于流0,axis_video_tvalid变为s_axis_video0_tvalid,对于流1,变为s_axis_video1_tvalid。

Table 1‐1: AXI4S视频协议输入(从机)接口信号

Table 1-2 显示了输出(主)侧的接口信号名称和功能。类似地,对于具有多个AXI4-Stream输出接口的IP,信号前缀m_axis_video应该附加到m_axis_videok 之后,其中k是各个输出AXI4-Stream的索引;例如,对于流0,axis_video_tvalid变为m_axis_video0_tvalid,对于流1,变为m_axis_video1_tvalid。

Table 1‐2: AXI4S视频协议输出(主机)接口信号

1.1.1 READY/VALID 握手

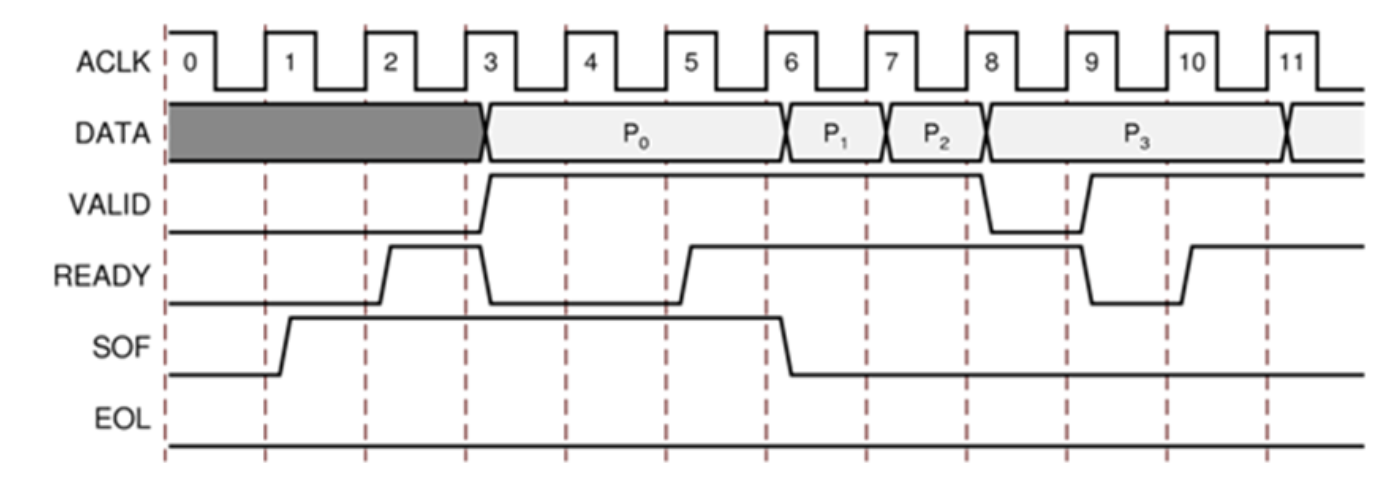

每当就绪(READY)、有效(VALID)、ACLKEN和ARESETn信号在ACLK的上升沿为高电平时,就会发生有效传输,如Figure 1-2所示。

Figure 1‐2: 就绪/有效握手示例,新帧开始

在有效传输期间,数据仅携带有效视频数据。AXI4S上的视频不会传输空白时段(行场消隐)和辅助数据包。

1.1.2 帧开始信号(start of frame (SOF))

帧开始(SOF)信号通过AXI4S TUSER0信号进行物理传输,表示视频场或帧的第一个像素。SOF脉冲是一个有效的事务宽度,并且必须与场或帧的第一个像素一致(Figure 1-2).SOF充当帧同步信号,允许下游内核重新初始化,并检测场或帧的第一个像素。

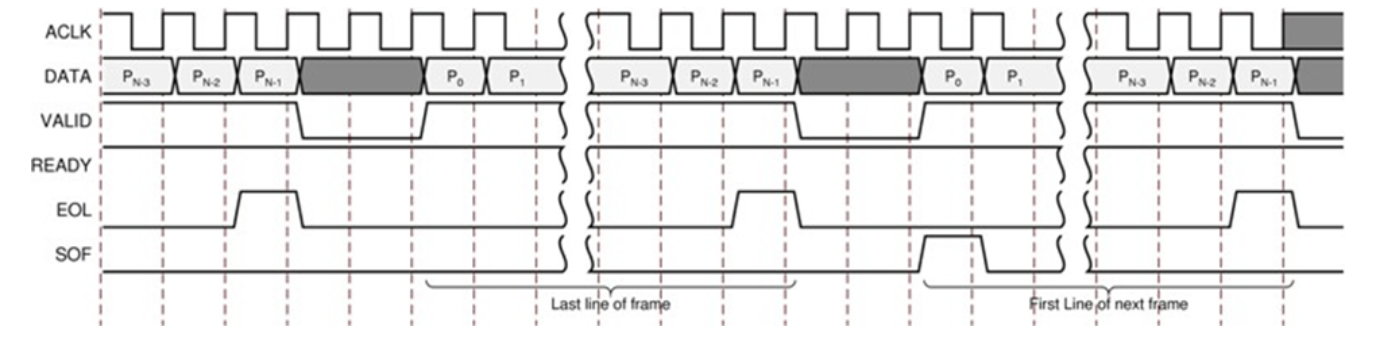

1.1.3 行尾信号(End of Line Signal)

行尾(The end of line,EOL)信号通过AXI4S TLAST信号进行物理传输,表示一行的最后一个像素。EOL脉冲是一个有效的事务宽度,并且必须与扫描线的最后一个像素一致(Figure 1-3).

Figure 1‐3: EOL和SOF信号的使用

1.2 数据格式

为了传输视频数据,数据格式对物理数据信号的逻辑信道子集进行编码。视频模块之间的AXI4S接口可以有助于使用不同精度(例如,每个颜色通道8、10或12位)和/或不同格式(例如,RGB或YUV 420)以及每个数据拍不同数量的像素来传输视频。

总结就是,数据格式通过AXIS接口的TDATA信号线传输,根据传输的视频格式改变信号线的宽度。

1.2.1 AXI4-Stream 特定参数化

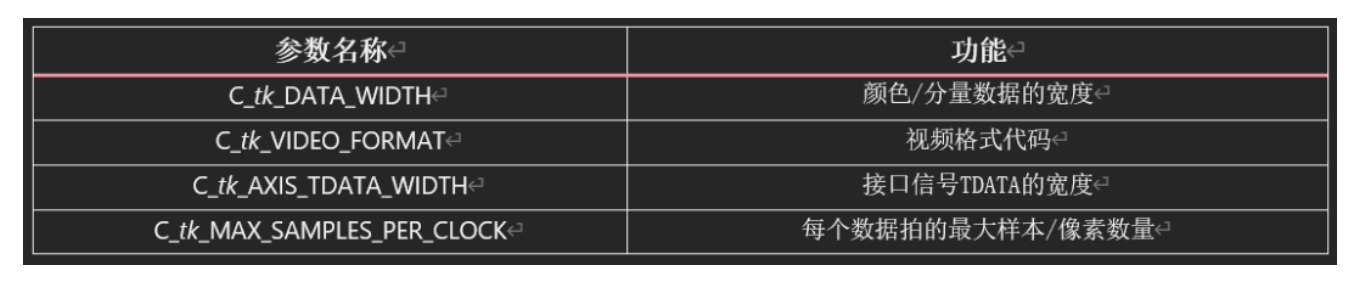

视频IP配置参数在第3章的IP参数化中描述。AXI4S接口视频协议的具体参数在Table 1-3中列出。

Table 1‐3: AXI4-Stream 特定参数化

C_tk_AXIS_TDATA_WIDTH参数确定AXI4S接口tk上可变宽度接口信号TDATA的宽度,其中接口类型t可以具有指定主或从接口的值[m,s],而可选整数k指定接口ID。通常,C_tk_AXIS_TDATA_WIDTH是分量数据宽度、每个数据拍的像素/样本数以及实际视频格式使用的分量数的函数。

组件数据宽度的推荐参数名称是C_tk_DATA_WIDTH。可选的格式参数C_tk_VIDEO_FORMAT可以帮助IP使用HDL函数确定数据中存在的颜色成分的数量。视频IP通常在输入接口上需要特定的格式,并且可以在IP中硬编码颜色分量通道的数量。然而,当C_tk_VIDEO_FORMAT(由主接口上的默认值设置)在HDL设计中传播到从接口时,IP源代码可以使用断言执行DRC,以确保AXI4S视频接口由以预期格式编码的视频驱动。

1.2.1 编码

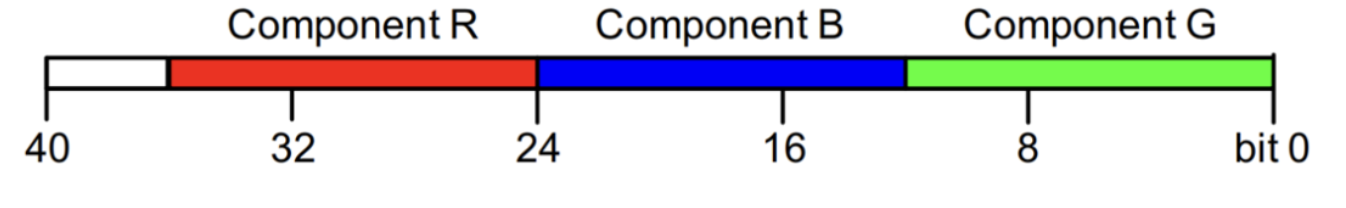

数据位使用[N-1:0]位编号惯例(N-1至0)表示。数据的隐式子字段的组成部分应该紧密地打包在一起;例如,DW=10位RGB数据打包成30位。如有必要,打包后的数据字应使用最高有效位(msb)进行零填充,使数据宽度使是8的倍数整数,如Figure 1-4所示。

Figure 1‐4: 多像素TDATA的视频数据填充

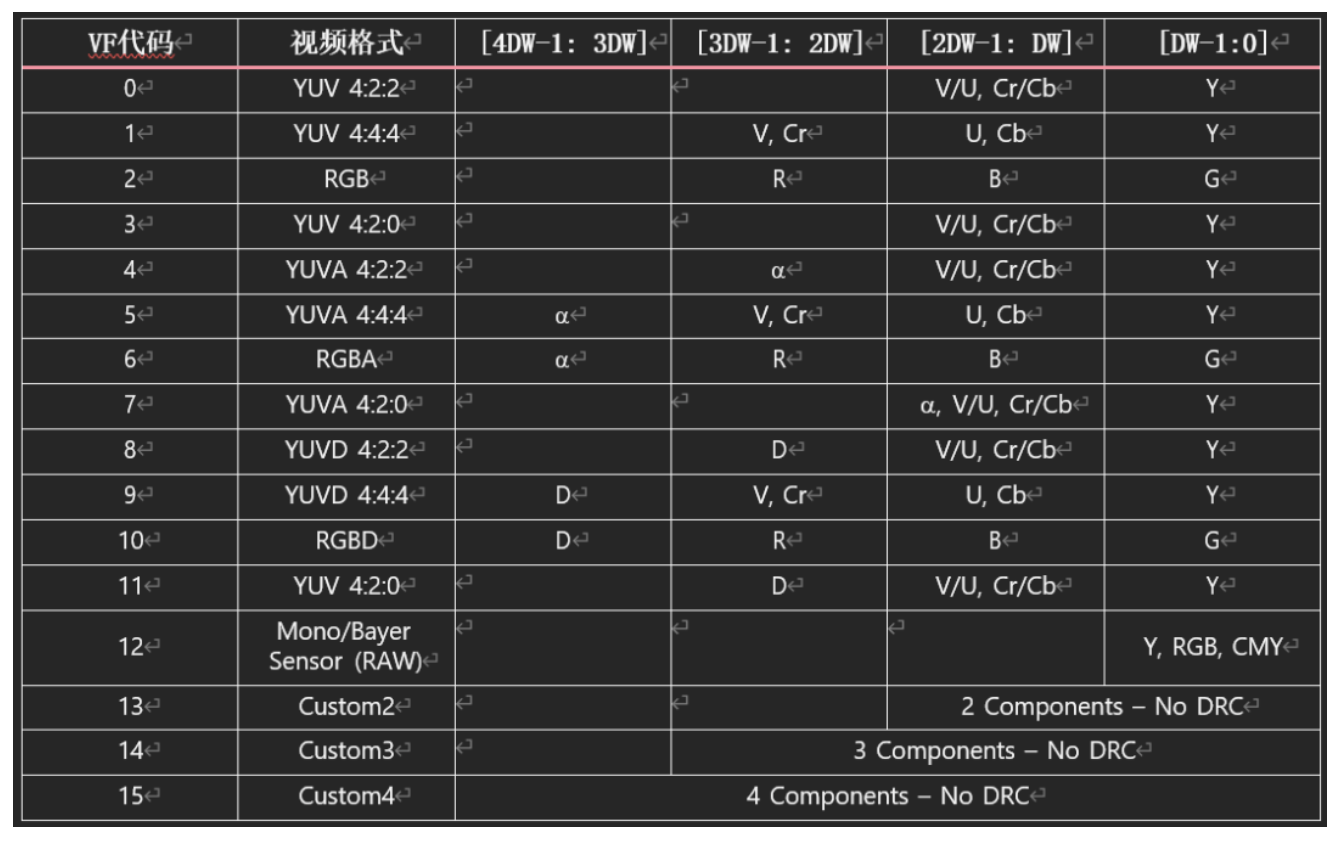

不同格式的详细表示在Table 1-4中列出,其中DW = C_DATA_WIDTH,VF = C_VIDEO_FORMAT。

Table 1‐4: C_tk_MAX_SAMPLES_PER_CLOCK =1的视频格式代码和数据表示

注:对于4:2:2和4:2:0格式中的任何一种,Cb(或U)和Cr(或V)样本被分割到两个数据拍上,但只能在每个时钟一个样本的模式下进行。第一个数据拍保持Cb(或U);第二个数据拍保持Cr(或V)。换句话说,帧的第一个有效像素包含[Cb0:Y0],下一个像素包含[Cr0:Y1]。4:2:0格式在4:2:2格式的基础上增加了垂直子采样,这是通过省略每隔一行的色度数据在AXI4-Stream上的视频中实现的(和BT.1120完全类似)。

注:拜耳传感器数据也称为原始数据,一般为RAW8/RAW10/RAW12/RAW14/RAW16等格式。

1.2.1.1 多个像素编码-静态TDATA配置

当AXI4S携带多个样本/像素时,像素应该从最低有效位(LSB)打包到MSB,例如,最低有效像素应该对应于扫描线中最左边的像素,或者对应于时间上最早捕获的像素。例如,如果每个数据拍发送4个样本/像素,则第一个样本位于最低有效位,第四个样本位于最高有效位。

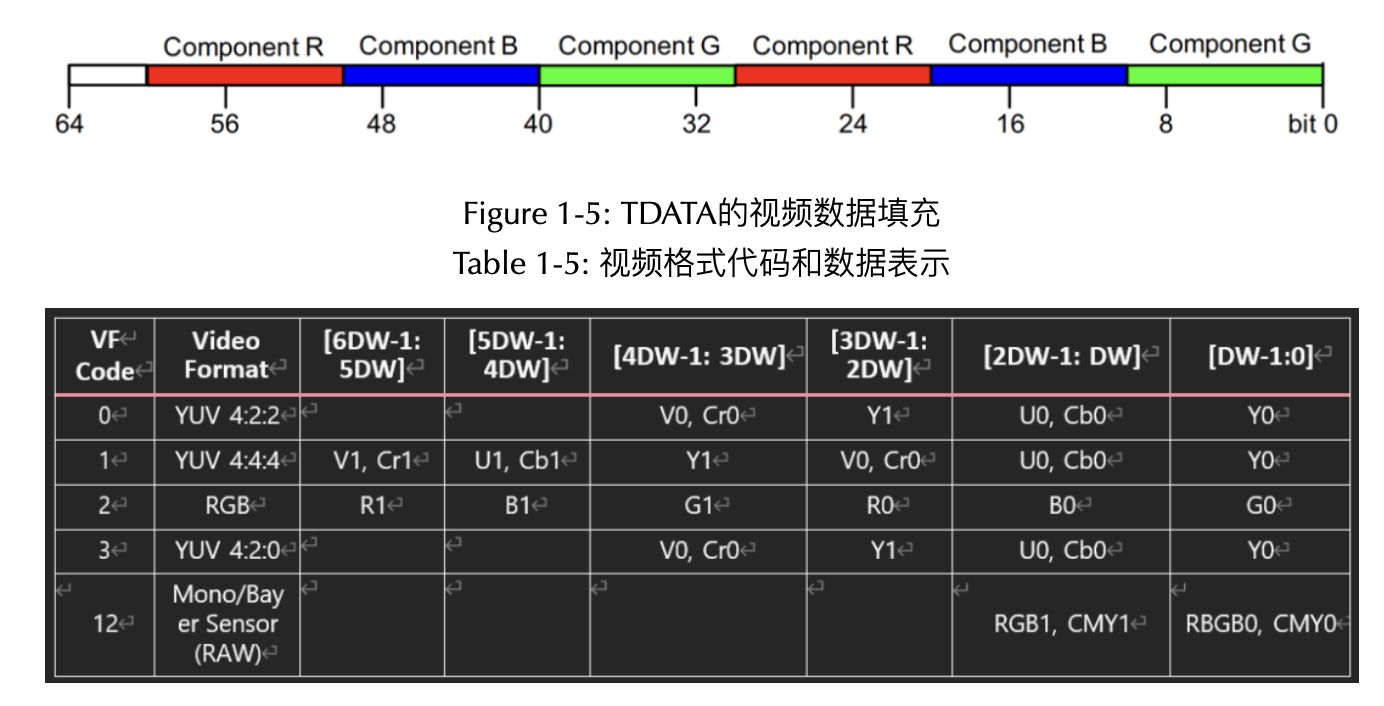

当使用AXI4-Stream上的视频协议传输多个像素或样本时,与各个像素相关的颜色分量按照下式排列,Table 1-5给出了用于传输视频模式0、1、2、3、12的两个像素的例子。像素数据被连续打包,像素之间没有任何填充。当N*DW不是8的倍数整数时,视频数据在msb上补零,如Figure 1-5所示。

如果行大小不能被每个数据拍的像素/样本数整除,则行的最后一拍应使用LSB。然后,该行最后一个数据拍的msb中未使用的像素应补零。

1.2.1.2 多像素编码动态TDATA配置

对于视频IP可以动态改变颜色分量宽度、视频格式或每个数据拍的像素/样本数量的应用,像素和分量应该保持在由用于实例化的通用参数确定的静态位置。例如,如果只有一个像素通过支持每个数据拍最多两个像素的接口传输,则样本/像素应该与最低有效像素位置对齐。同样,如果每个器件只有8位通过为每个器件产生的10位接口传输,则有效位应MSB对齐,LSB用零填充。

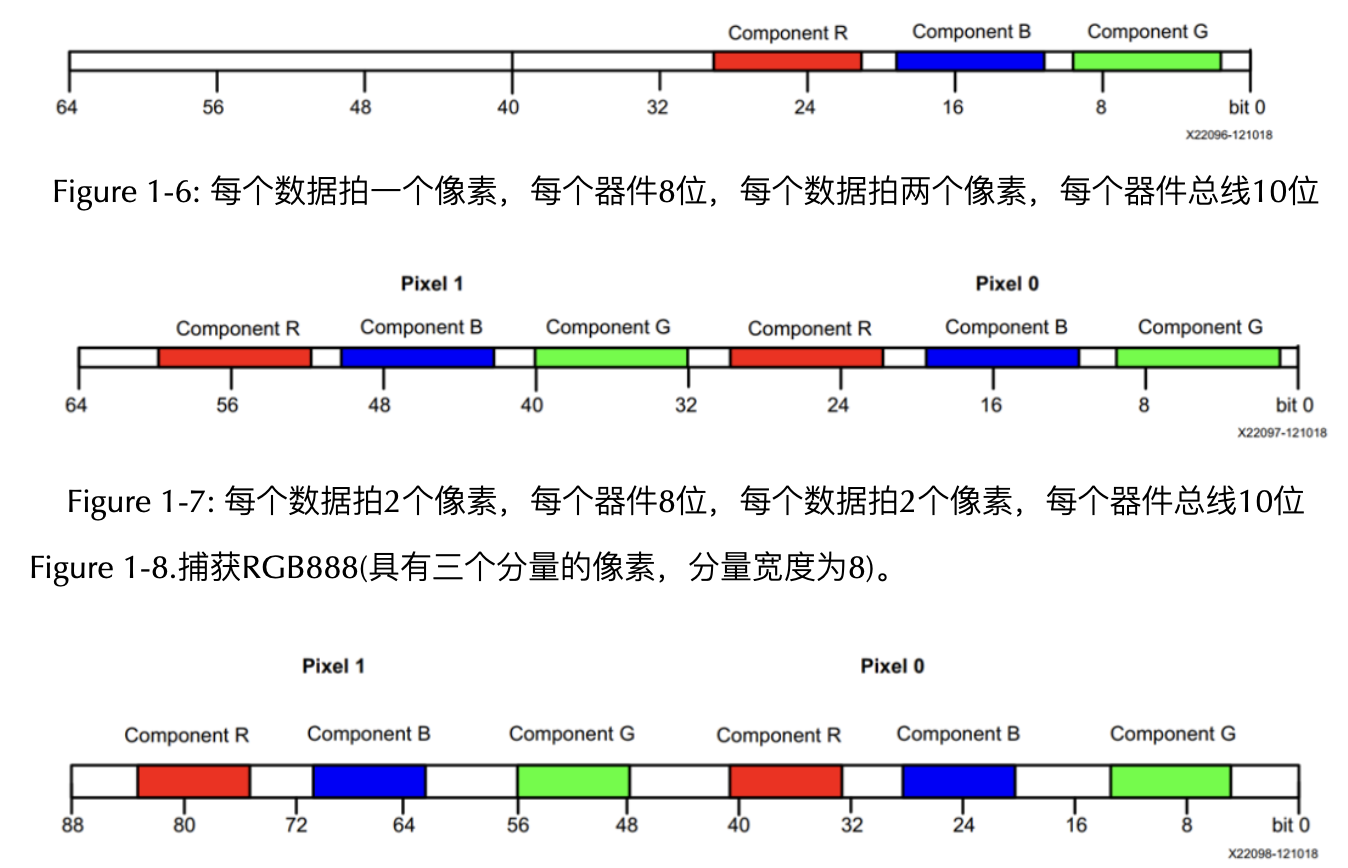

Figure 1-6 和 Figure 1-9中显示了三个示例。

重要提示:尽管本规范支持动态更改每个数据拍的像素/样本数,但不建议这样做,因为并非所有IP都支持此功能。

Figure 1‐8: 每个数据拍两个像素,每个分量八位(RGB888,VF码2),每个数据拍两个像素,每个分量总线14位

注意事项:

- 每个G、B、R元件位于14位空间,MSB对齐。

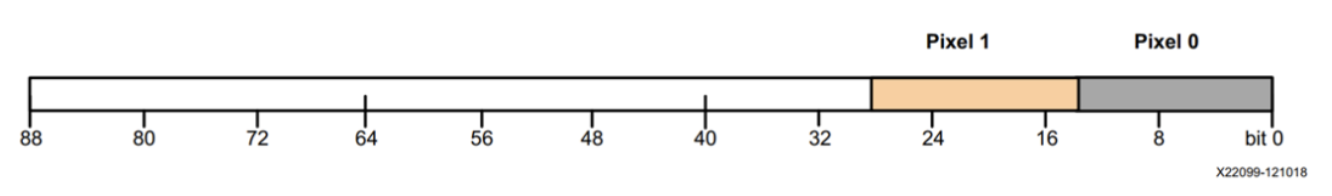

Figure 1-9.捕获RAW14(具有单个组件的像素,组件宽度为14)。

Figure 1‐9:每个数据拍两个像素,每个元件14位(RAW14,VF代码12),每个数据拍两个像素,每个元件总线14位

注意事项:

- 虽然RAW14可能仅使用较低的28位,但完整的AXI4S接口仍然是88位,因为在处理动态TDATA时,如果需要,它必须能够以每种颜色完整的14位切换到RGB。下游逻辑必须意识到这一点,并应提供适当的总线接口,然后在内部丢弃不使用的位。

比较Figure 1-8 和Figure 1-9中的两种数据类型组件宽度,RAW14,VF Code 2数据类型具有14位组件和RGB888 (VF Code 2) 8位组件。

因此,RGB888元件在14位元件总线上以MSB对齐、LSB补零的方式放置。此外,RAW14像素紧密地封装在一起。

1.2.2 多像素编码示例

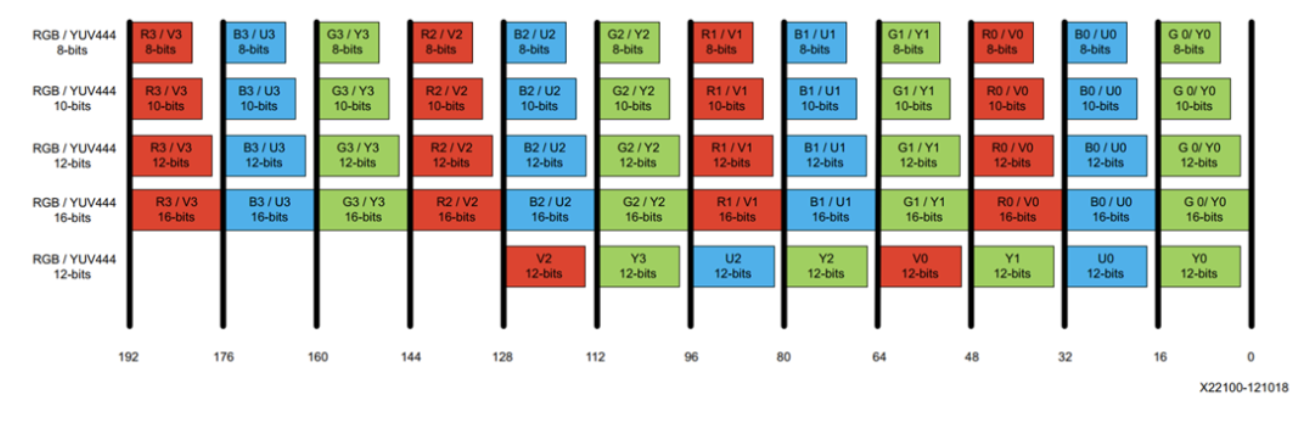

AXI4S视频接口支持每时钟双像素或四像素,对于RGB、YUV444和YUV420色彩空间,每个分量有8位、10位、12位和16位。当参数“每个组件的最大位数”设置为16时,Figure 1-10 显示了完全符合AXI4S视频协议的每时钟四像素数据格式。

Figure 1‐10: 四像素数据格式(每个分量的最大位数= 16)

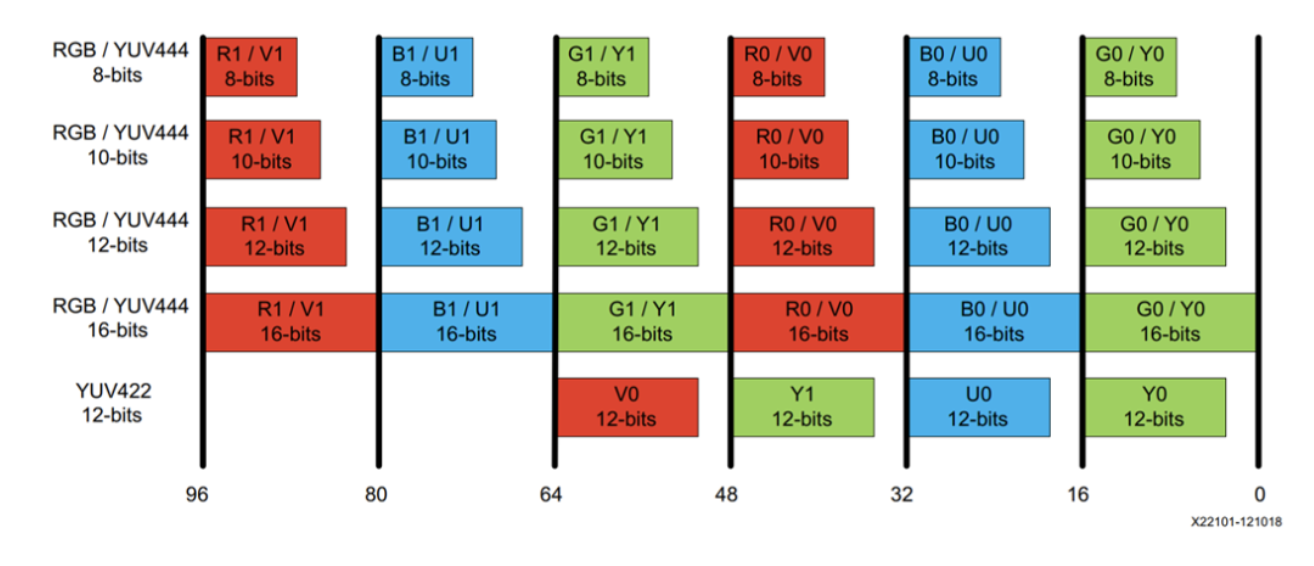

每时钟双像素的数据格式完全兼容AXI4S视频协议,如Figure 1-11所示。

Figure 1‐11: 双像素数据格式(每个组件的最大位数= 16)

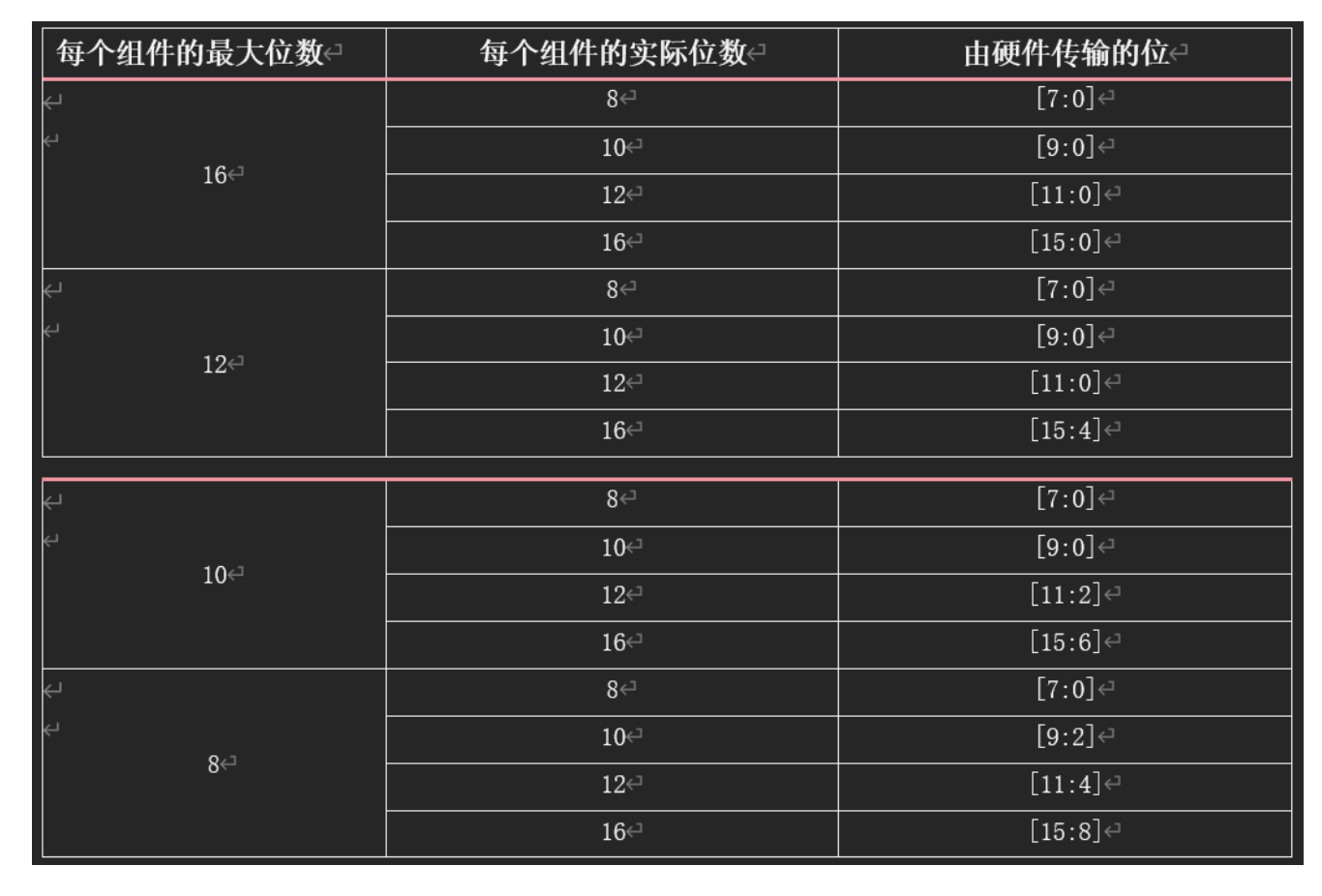

当参数“每个分量的最大比特数”设置为12时,每个分量的实际比特数大于12的视频格式将被截断为每个分量的最大比特数。剩余的最低有效位被丢弃。如果每个器件的实际位数小于Vivado IDE中设置的每个器件的最大位数,则所有位都以MSB对齐方式传输,其余LSB位以0填充。这适用于所有每个组件的最大位数设置。

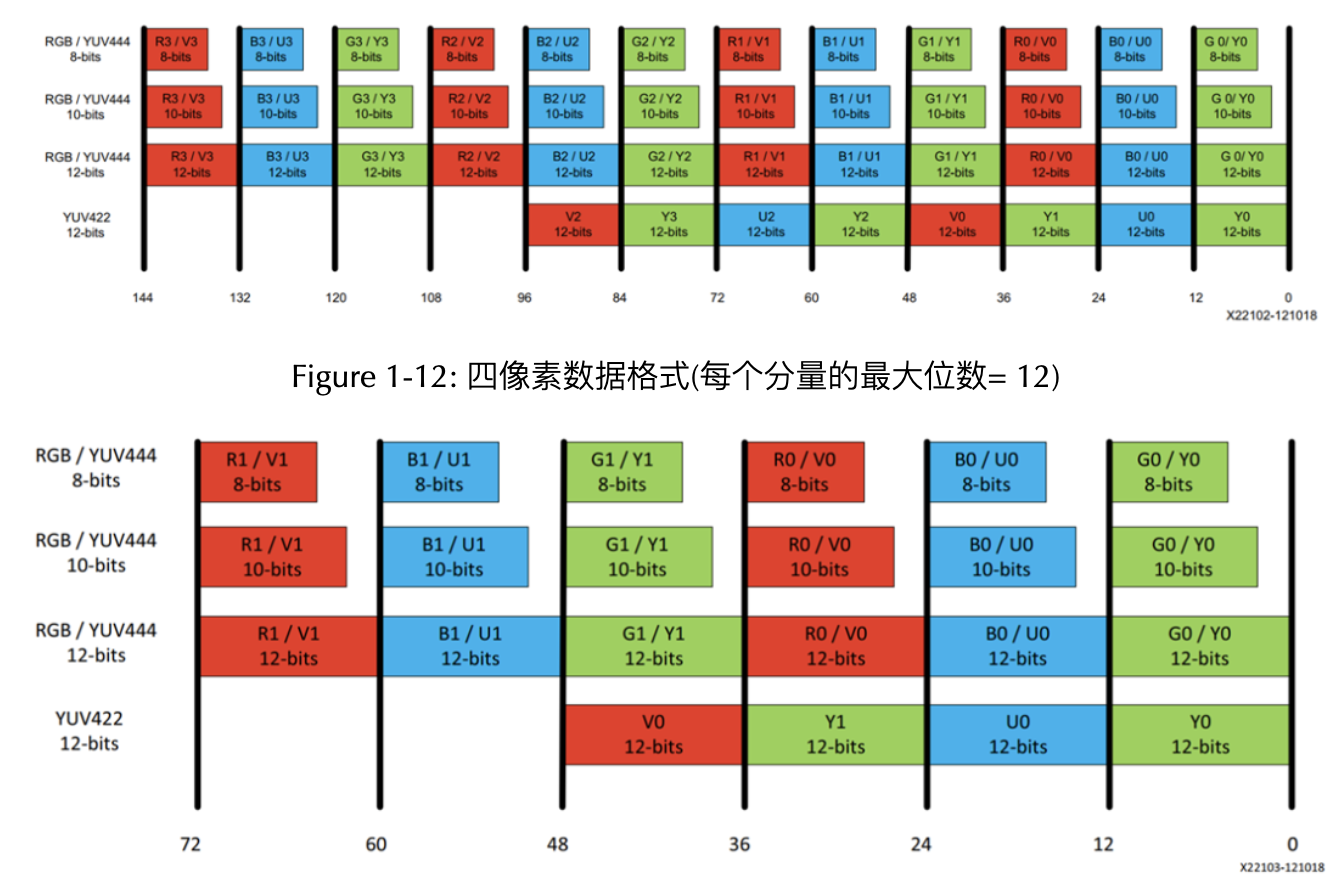

举例来说,当每个组件的最大比特数被设置为12时,Figure 1-12 显示了完全符合AXI4S视频协议的每时钟四像素数据格式。

完全兼容的每时钟双像素AXI4S视频协议的数据格式如Figure 1-13所示。

Figure 1‐13: 双像素数据格式(每个组件的最大位数= 12)

当参数“每个分量的最大比特数”设置为12时,每个分量的实际比特数大于12的视频格式将被截断为每个分量的最大比特数。剩余的最低有效位被丢弃。如果每个器件的实际位数小于Vivado IDE中设置的每个器件的最大位数,则所有位都以MSB对齐方式传输,其余LSB位以0填充。这适用于所有每个组件的最大位数设置。

Table 1‐6: 每个组件支持的最大位数

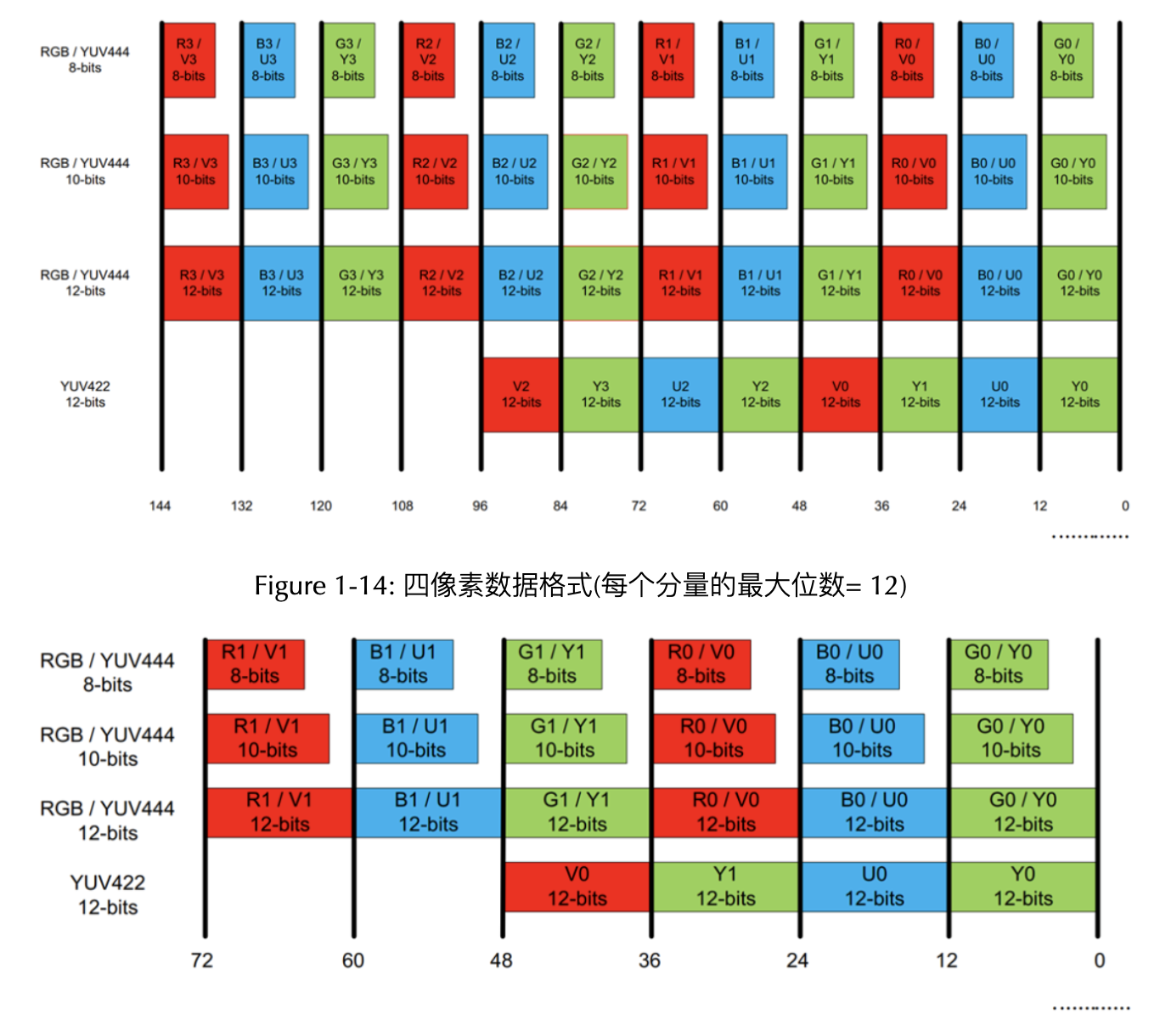

举例来说,当每个组件的最大比特数被设置为12时,Figure 1-14 显示了完全符合AXI4S视频协议的每时钟四像素数据格式。完全兼容的每时钟双像素AXI4S视频协议的数据格式如Figure 1-15所示。

Figure 1‐15: 双像素数据格式(每个组件的最大位数= 12)

视频接口还可以传输YUV420色彩空间中的四像素和双像素。

类似地,对于YUV 4:2:0深色(10、12或16位),数据表示是相同的。唯一的区别是每个组件携带更多的位(10、12和16)。当使用AXI4-Stream传输时,数据表示需要符合UG934中定义的协议。借助重新映射功能,相同的原生视频数据将被转换为AXI4S格式,如Figure 1-16所示。4:2:0格式在4:2:2格式的基础上增加了垂直子采样,这是通过省略每隔一行的色度数据在AXI4-Stream上的视频中实现的。

Figure 1‐16: YUV 4:2:0 AXIS流视频数据(每时钟双像素)

注意:对于RGB/YUV444/YUV422,视频数据直接从AXI4S映射到原生视频接口,没有任何行缓冲。因此,Figure 1-12 到Figure 1-15 通常表示AXI4S和本地视频的数据接口。图中省略了控制信号。

该子系统利用配置参数、每个元件的最大位数和每个时钟的像素数,提供了构建系统的充分灵活性。设置这些参数,以便目标设备支持视频时钟和链路时钟。例如,当选择每时钟双像素时,与每时钟四像素设计相比,AXI4S视频需要以更高的时钟速率运行。在这种情况下,系统更难满足定时要求。因此,对于旨在发送更高视频分辨率的设计,建议使用每时钟四像素数据映射。

某些视频分辨率(例如720p60)的水平定时参数(1650)不是4的倍数。在这种情况下,必须选择每时钟双像素数据映射。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多IC设计干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。