在最近的ISSCC会议上,来自英特尔的Mozhgan Mansuri就有线和无线接口设计中与时钟有关的内容做了一个很有启发性的简短演讲。这次演讲非常深入,包括了从基本的时钟原理到合成和分配时钟信号的独特电路设计策略的回顾。

由于涉及的主题过多,这里将重点介绍基于有线的设计注意事项。

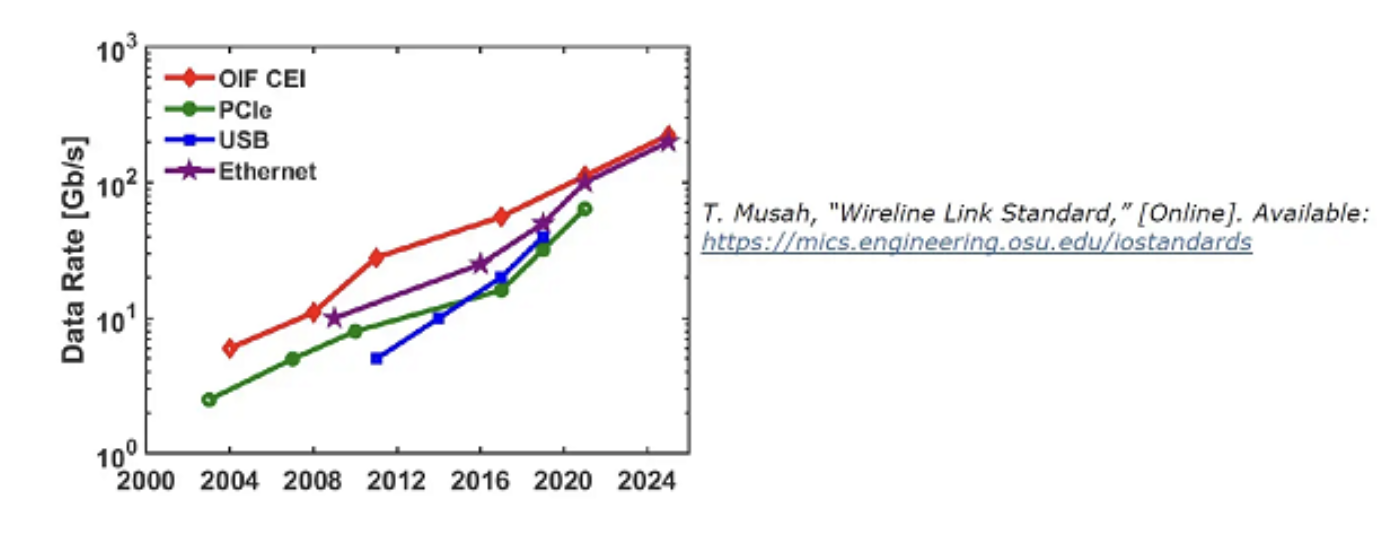

有线数据速率趋势

描述了几种接口标准下线缆“每通道数据率”的进展情况。

摩尔定律的PPA效益与接口数据率的增强是并行发展的,每2-3年翻一番。然而,由于有线链接横跨硅芯片、封装、电路板互连、连接器和电缆,单单硅技术的扩展并不能说明所有的数据速率提升。封装/PCB材料的改进和仿真工具的进步无疑是有帮助的。

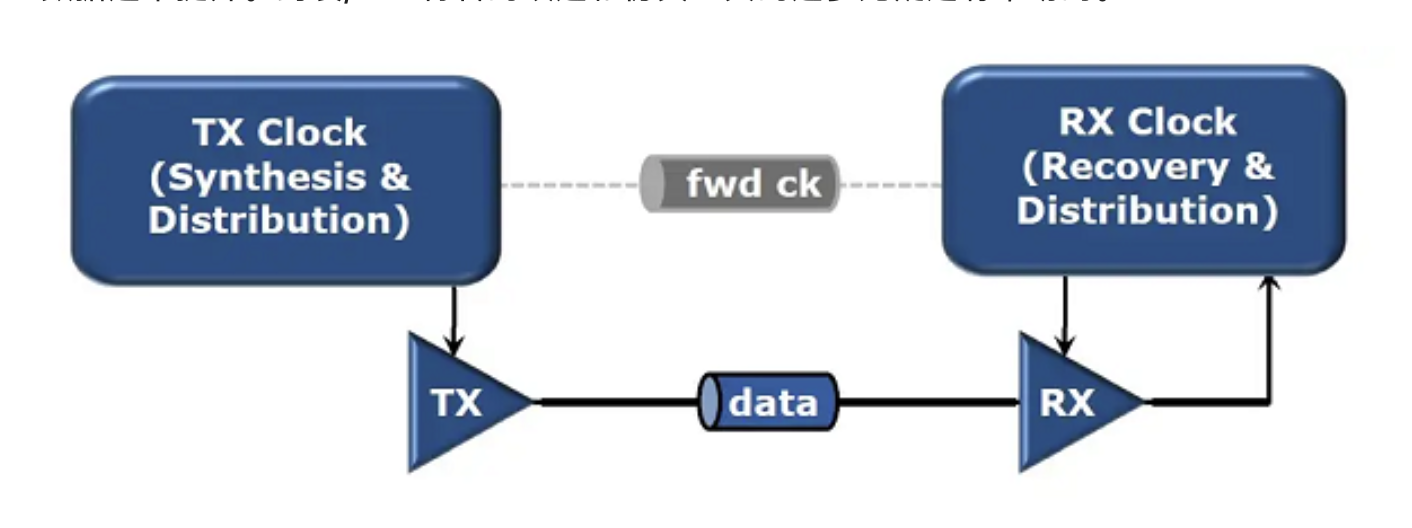

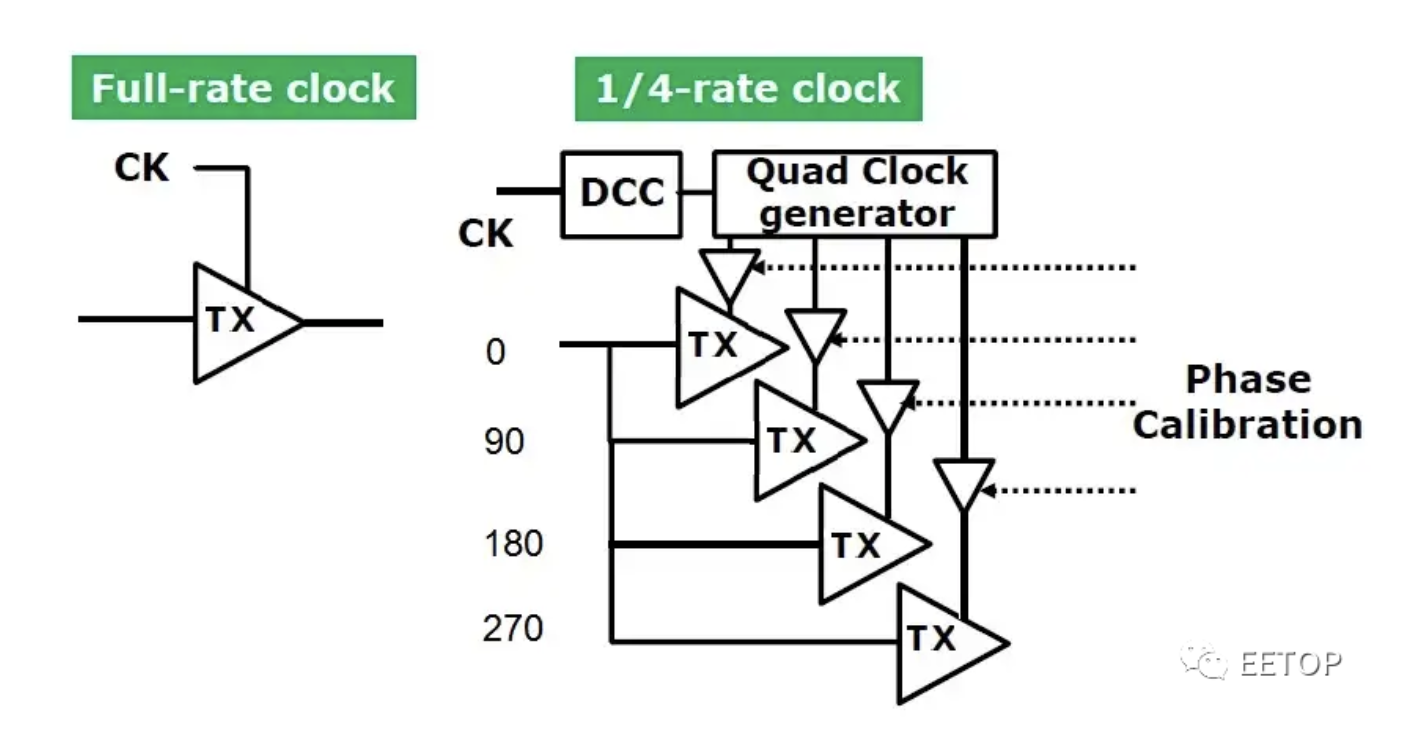

这种增长的关键是支持信道Tx和Rx端的接口电路的持续改进。相关的时钟生成(和Rx时钟恢复)技术一直是这些电路创新的核心,如下图所示,显示了数据中的嵌入式时钟和时钟转发选项。

时钟定义

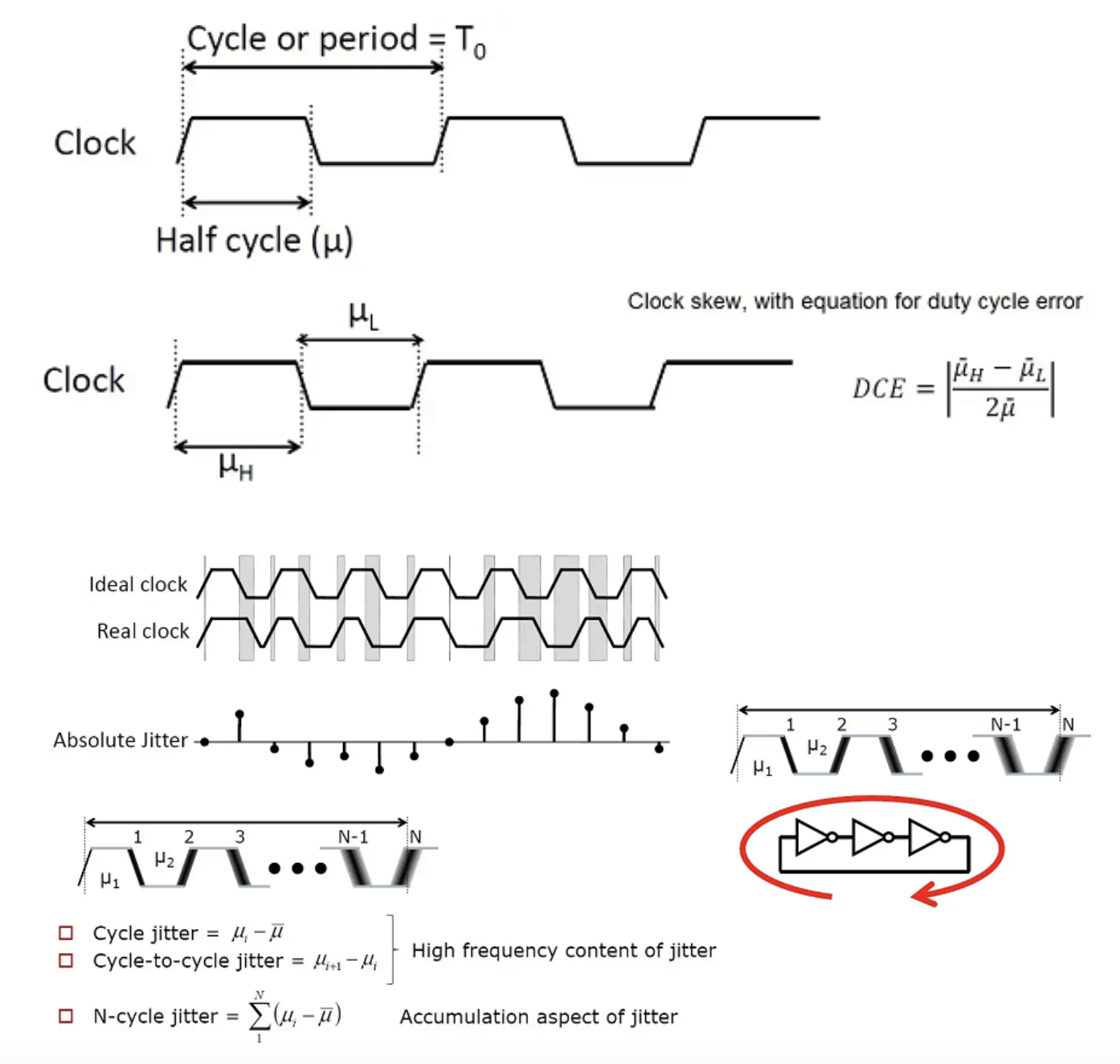

基本时钟定义如下所示:

- 时钟周期

- 占空比

- 时钟漂移(静态占空比误差,半个周期持续时间之差)

- 时钟周期之间的抖动

请注意,在上面的最后一个图中,抖动可能会随着时间的推移而累积,正如奇数逆变器、自由运行的振荡器时钟源所描述的那样。

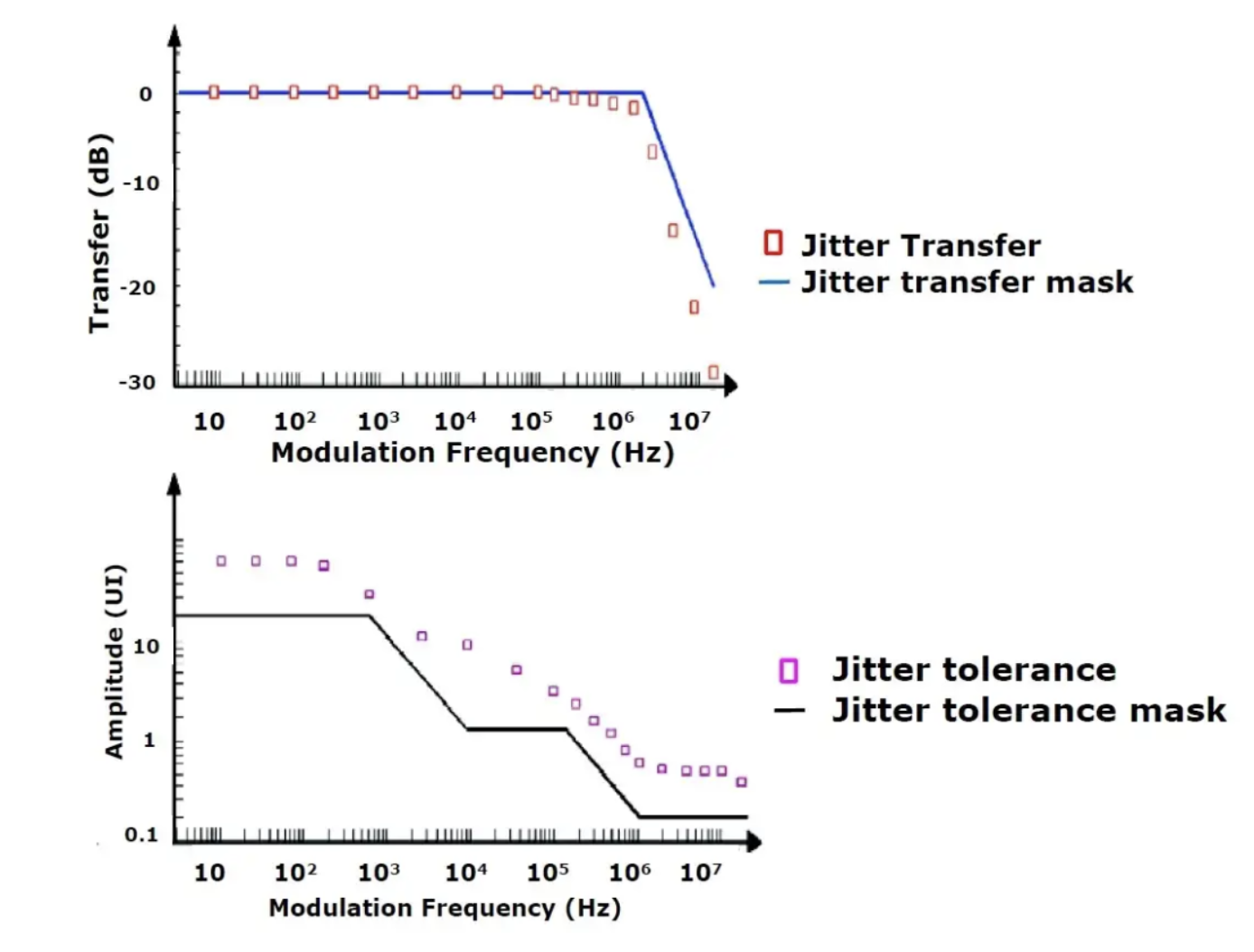

下图说明了时钟分布的两个关键测量(和规格)。图的前半部分说明了电路对抖动频率内容的频率响应;后半部分说明了Rx时钟恢复电路对抖动的 "容忍度"。

这些数字包括频率上的典型规格“掩模”。上面描述的“理想”抖动传递曲线通过时钟分布组件提供了一个“0分贝,无抖动放大”的目标掩码。抖动容忍掩码规范使设计者能够开发Rx时钟恢复电路,随后确保Tx抖动源不超过掩码限制。

时钟合成电路

为了在片上产生高频时钟,常用的方法是采用两种主要电路类型之一—PLL(phase-lockedloop)和DLL(delay-locked loop)。它们的主要功能是提供一个由低频(高质量)参考时钟衍生出来的 "倍增 "时钟输出,如下所述。另一个关键的时钟合成配置是用一个“注入锁定振荡器”(ILO)来对单个时钟进行相位校准。

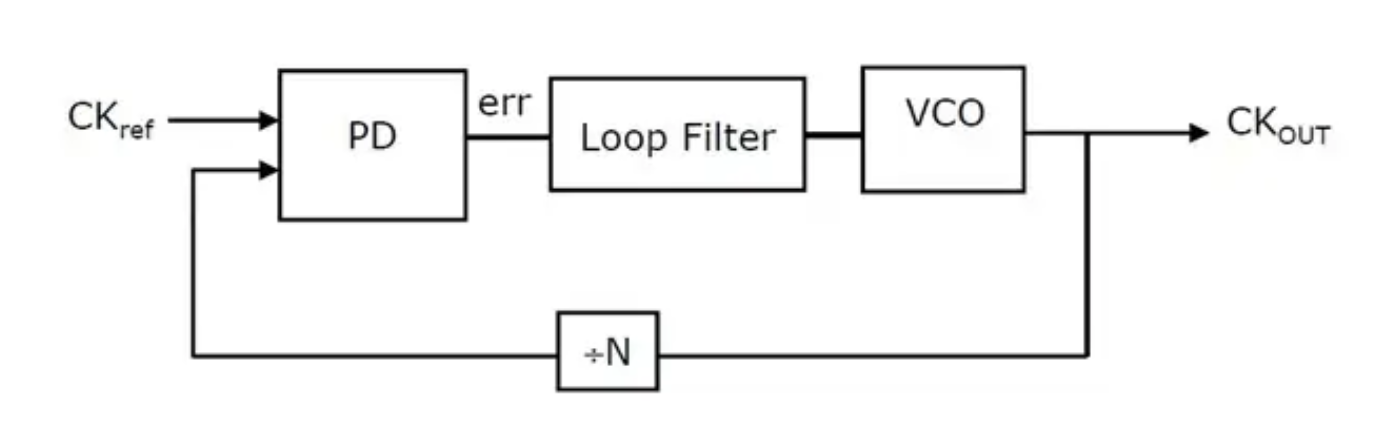

PLL

PLL由以下部分组成

- 一个压控振荡器

- N分频计数器

- 相位检测器,它提供的输出信号与参考时钟和分频VCO时钟之间的前导/后导相位差成正比。

- 一个低通滤波器,可以有效地阻止来自相位检测器的短时信号影响VCO的控制输入。

PLL的频率带宽响应定义了抖动响应,这是一个关键的设计权衡。例如,较低的带宽将降低参考时钟输入的抖动灵敏度。较高的带宽将降低对VCO抖动的灵敏度。

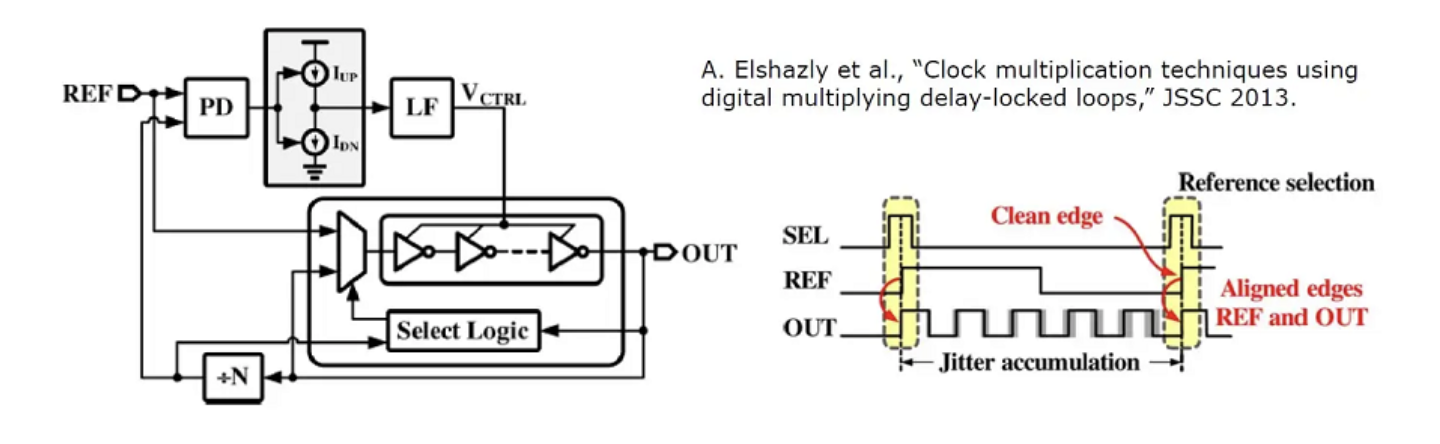

DLL

上图说明了DLL的基本原理。锁相环中自由运行的VCO振荡器被延迟线所取代,延迟线的单个延迟元件由鉴相器和低通滤波器输出控制-图中显示的是一个简单的变频延迟链。抖DLL时钟输出中的抖动通过每N个周期使用参考时钟边沿进行 "复位",使用多路复用器输出提供延迟链输入--见图中时序图。

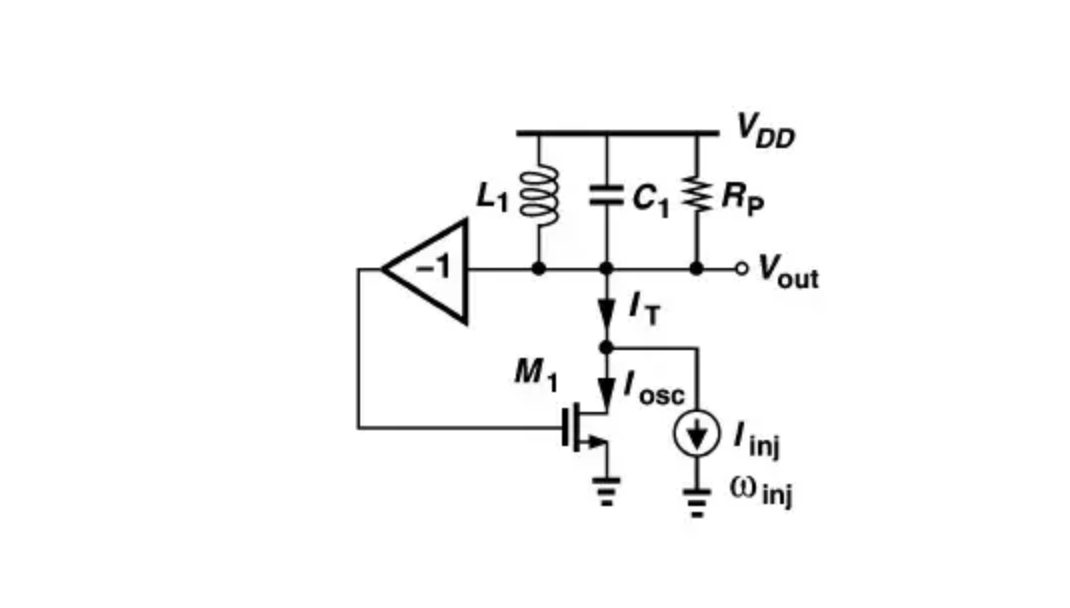

注入锁定振荡器(ILO)

时钟合成的另一种选择是使用注入电流到振荡系统,以提供输出时钟相位调节控制。

ILO高层框图如下所示,有三部分值得注意。

- 振荡器(简单描述为n FET和反相放大器)

- 一种调谐槽电路

- 注入电流源

让我们回忆一个有趣的物理实验(见视频),在这个实验中,相同时间段的多个节拍器是松散耦合的—但随着时间的推移,它们就会保持到同步。

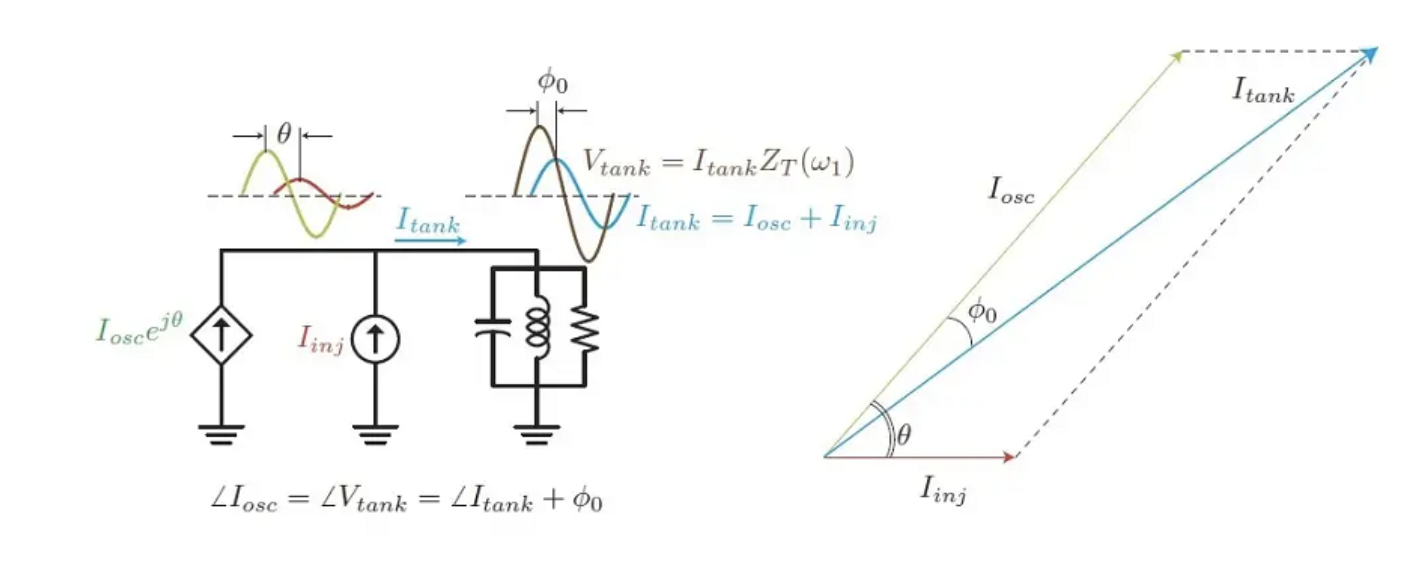

一个频率为f的注入电流同样会使组合系统的输出电压同步到这个频率。然而,由于三个分量的相对阻抗,系统输出电压与组成电流I_tank、I_osc和I_inj之间会产生相移,如下图所示。

简而言之,Vout = (Z_tank * I_tank),其中I_tank = (I_osc + I_inj)。这些都是具有幅度和相位的复杂量。ILO的主要特点是,注入电流的大小可以调整输出电压的相位。

因此,ILO是校准(或“旋转”)时钟输出相位的理想方法,相对于基准-相位差检测器增加/减少注入电流的大小相应。

考虑这样一种情况,希望从一个振荡器的多个内部阶段产生时钟,每个时钟通过一个特定的相位移位/对齐。下面的例子显示了4个相同频率的时钟,每个相位偏移了90度。

对这些移位时钟的逻辑运算产生独特的脉冲,例如,clock_0和clock_270。当提供了与这些移位时钟的逻辑操作对应的转换的数据训练模式时,数据和时钟脉冲之间的相位差可以通过注入锁定电流检测和校准。一旦校准,时钟就可以用于以高数据速率- 4X参考时钟频率发送/接收数据,如上面的例子。

前面的讨论提到了时钟生成电路的框图--Mozhgan在她的演讲中详细介绍了这些单元。

VCO

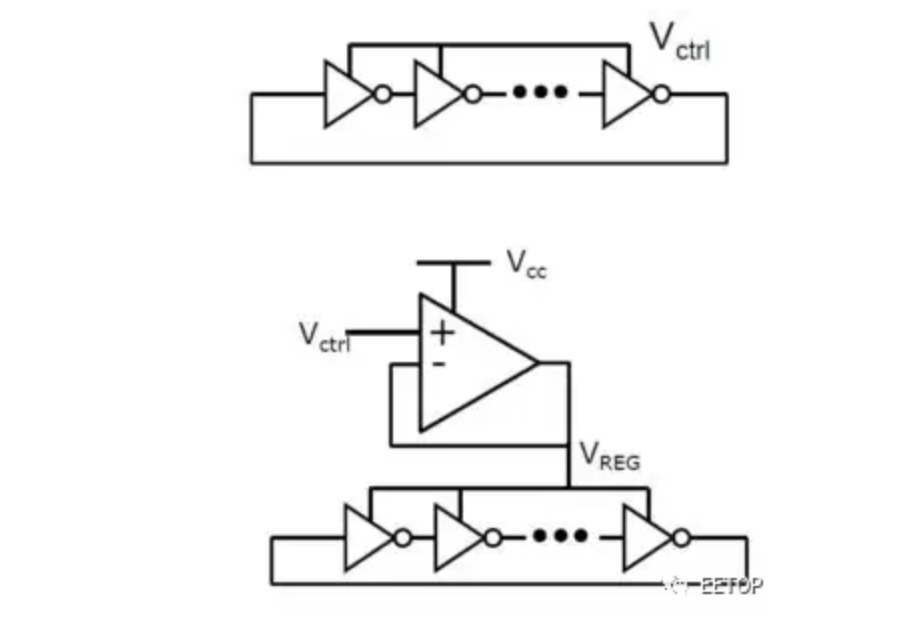

她演讲中的压控振荡器的例子如下图所示。

第一个例子是一个简单的(奇数)变频器环路,提供一个自由运行的振荡器--每级的延迟由电压控制信号修改。(也经常使用引入延迟控制的其他方法,例如,使用变容二极管给每个级增加可变容性负载;使用“电流缺乏”逆变器,在下拉/上拉堆栈中附加一个系列FET/p/FET,其器件门提供电压控制输入。)这种自由运行的拓扑结构的一个缺点是对电源/控制输入端的噪声敏感。

上图所示的第二个例子包括一个运算放大器/调节器作为低通滤波器,以改善电源噪声抑制。

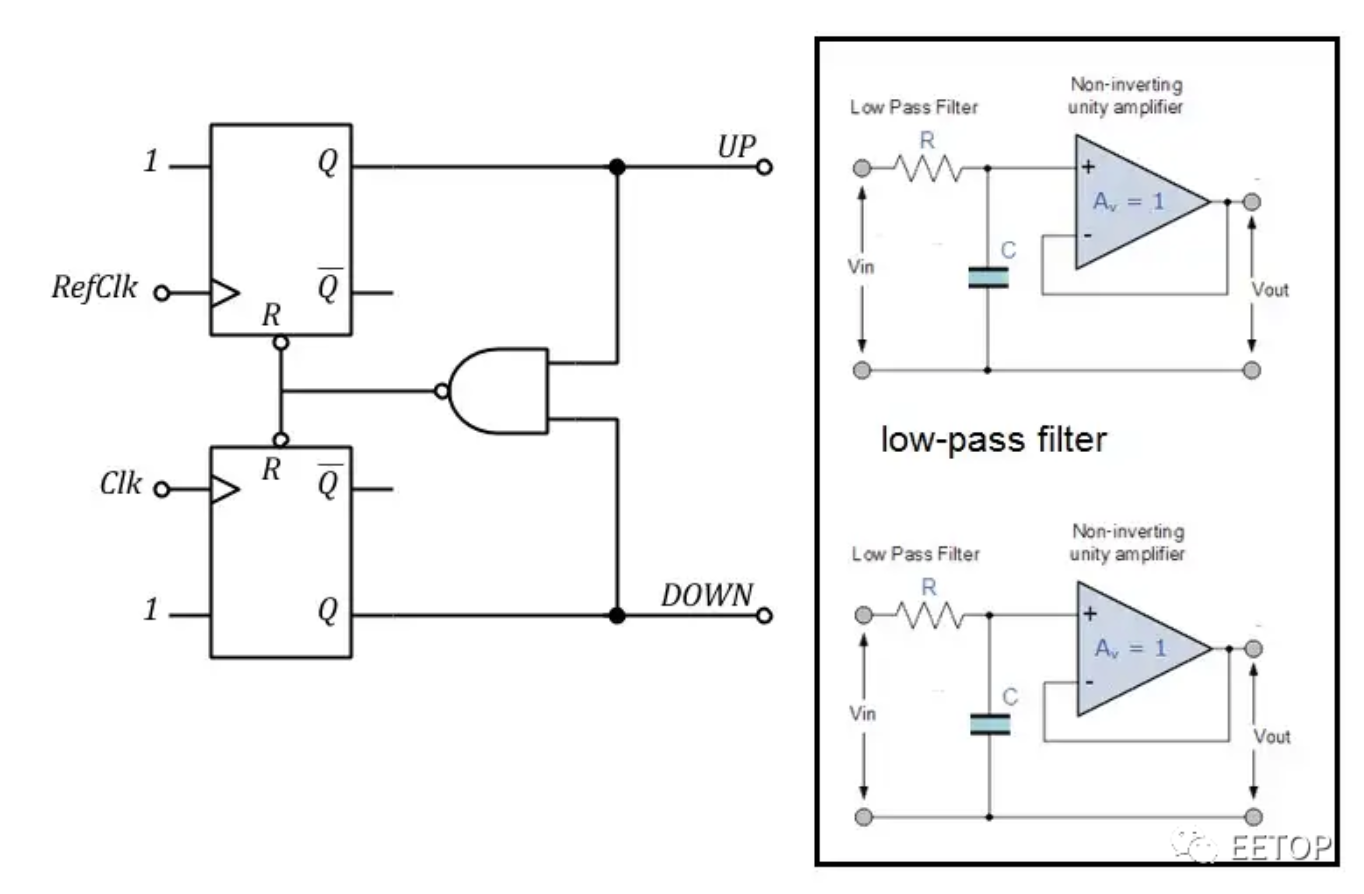

相位差检测器

将参考时钟与(分频)时钟进行比较的时钟生成电路使用相位差检测器向VCO提供控制信号。常用的检测器拓扑有很多--下面是一个简单的(数字)实例实现。

这种拓扑结构适合于使用两个输入--"UP "和 "DOWN "来代表参考时钟和生成时钟之间的滞后/领先相位差的振荡器控制电路。(需要一个低通滤波器来消除上升时钟和异步复位输入之间的任何杂散触发输出脉冲。)

时钟分配

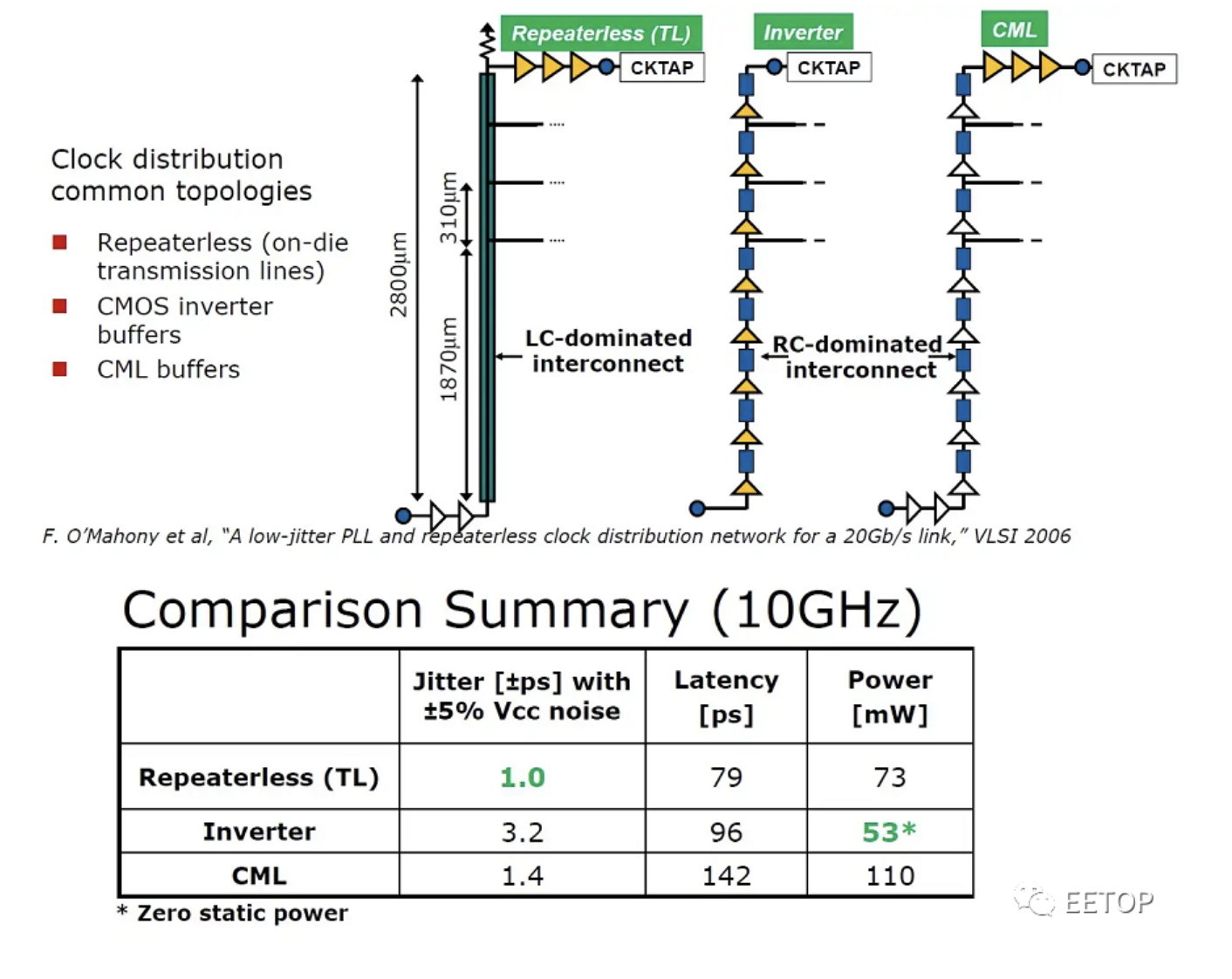

Mozhgan介绍了一些常见的设计拓扑,用于将one-die产生的时钟分配到(Tx或Rx)扇出。下图描述了三个例子,适用于单个(全局)时钟在被分接到一系列总线之前跨越相当长距离的情况。

- 无中继拓扑(差分、低摆信令),将互连视为LC传输线。

- 逆变再发电链

- 电流模式逻辑逆变器驱动链

此外Mozhgan的演讲还涵盖了大量额外的主题,这里没有重点介绍--例如,有线Rx时钟-数据对齐策略(适用于转发时钟和嵌入式SerDes时钟接口)、无线传输/接收机的时钟生成、时钟功率优化。

作者:EETOP编译

文章来源:EETOP

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。