【爱集微点评】紫光同创的FPGA专利,通过FPGA电路TILE层级连接检查方法以解决现有技术中TILE层级验证效率较低的技术问题。

集微网消息,虽然在后疫情时代,国产FPGA仍然在以往基础上持续发力,在2022年已经有了显著提效,展望未来,今年FPGA依然需要全面“提档”。

FPGA芯片在通信、安防、工业等领域有着举足轻重的作用,随着工艺水平的逐步提升,FPGA芯片的规模不断扩大、性能不断提升,同时验证工作量也随之增加。如何有效地提升大规模FPGA电路的验证效率,已经成为重要课题。FPGA电路规模的扩大,意味着模块的数量、电路网表的规模、连接的复杂度的增加,而TILE层级作为FPGA电路验证层次之一,编写断言检查文件用于连接检查趋于消耗更多时间,与此同时,TILE BMA(BehaviorMicroArchitecture)模型与TILE NETLIST网表的连接检查相互独立进行,存在一定的重复和冗余,使得TILE层级验证效率较低。

为此,紫光同创于2022年2月28日申请了一项名为“FPGA电路TILE层级连接检查方法、装置、电子设备及存储介质”的发明专利(申请号:202210190218.2),申请人为深圳市紫光同创电子有限公司。

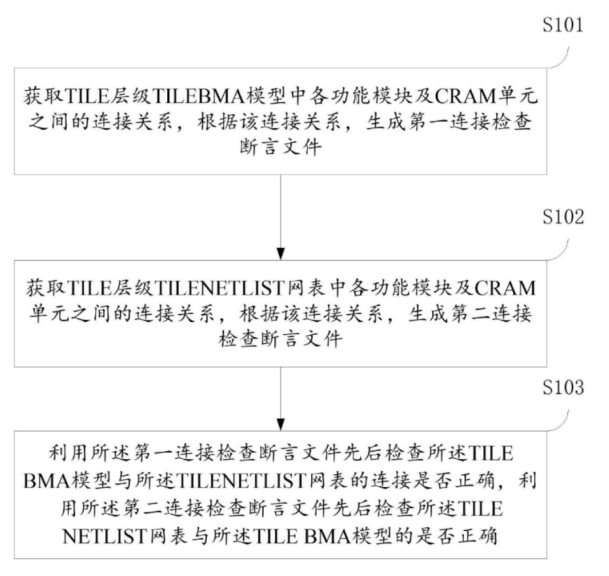

图1 FPGA电路TILE层级连接检查方法的流程示意图

图1是本发明提出的一种FPGA电路TILE层级连接检查方法的流程示意图。该FPGA电路TILE层级连接检查方法,主要包括以下步骤。首先获取TILE层级TILE BMA模型中各功能模块及CRAM单元之间的连接关系,根据该连接关系,生成第一连接检查断言文件(S101)。然后获取TILE层级TILE NETLIST网表中各功能模块及CRAM单元之间的连接关系,根据该连接关系,生成第二连接检查断言文件(S102)。接着利用第一连接检查断言文件先后检查所述TILE BMA模型与所述TILE NETLIST网表的连接是否正确,利用第二连接检查断言文件先后检查所述TILE NETLIST网表与所述TILE BMA模型的是否正确。

其中,FPGA电路TILE层级中包括多个功能模块及CRAM单元等基本模块,这些功能模块为能实现一些FPGA基本功能的模块,例如IOBD、IOBS、BSCR、BKCL、CCS等。而该CRAM单元用于存放能控制上述功能模块基本功能的配置点。

在生成连接检查断言文件时,使用脚本先基于TILE BMA模型提取内部各模块的第一连接检查断言文件,然后基于TILE NETLIST网表,提取出第二断言检查文件。

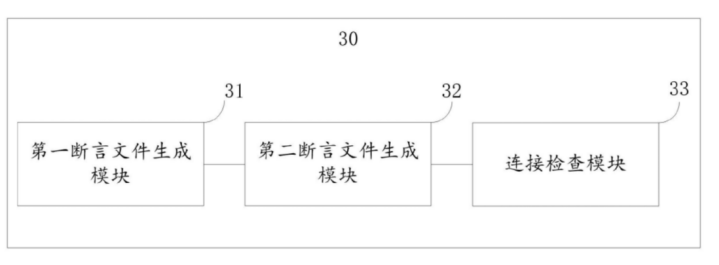

图2 FPGA电路TILE层级连接检查装置结构示意图

图2是本发明提出的一种FPGA电路TILE层级连接检查装置的结构示意图。该FPGA电路TILE层级连接检查装置包括第一断言文件生成模块31、第二断言文件生成模块32及连接检查模块33。其中,第一断言文件生成模块31用于获取TILE层级TILE BMA模型中各功能模块及CRAM单元之间的连接关系,根据该连接关系,生成第一连接检查断言文件。第二断言文件生成模块32,用于获取TILE层级TILE NETLIST网表中各功能模块及CRAM单元之间的连接关系,根据该连接关系,生成第二连接检查断言文件。而连接检查模块33,分别利用第一/二连接检查断言文件先后检查TILE BMA模型与TILE NETLIST网表的连接是否正确。

简而言之,紫光同创的FPGA专利,通过FPGA电路TILE层级连接检查方法以解决现有技术中TILE层级验证效率较低的技术问题。

随着Altera和Xilinx的收购,FPGA的格局发生了巨变,但国内各个厂商仍然精耕细作,其中紫光同创已经形成了覆盖高、中、低端的全系列FPGA和SoPC可编程系统芯片。相信在国产化的趋势下,紫光同创一定可以把握机会,在国外市场中,为国产FPGA开辟新天地。

关于爱集微知识产权

“爱集微知识产权”由曾在华为、富士康、中芯国际等世界500强企业工作多年的知识产权专家、律师、专利代理人、商标代理人以及资深专利审查员组成,熟悉中欧美知识产权法律理论和实务。依托爱集微在ICT领域的长期积累,围绕半导体及其智能应用领域,在高价值专利培育、投融资知识产权尽职调查、上市知识产权辅导、竞争对手情报策略、专利风险预警和防控、专利价值评估和资产盘点、贯标和专利大赛辅导等业务上具有突出实力。在全球知识产权申请、挖掘布局、专利分析、诉讼、许可谈判、交易、运营、一站式托管服务、专利标准化、专利池建设等方面拥有丰富的经验。我们的愿景是成为“ICT领域卓越的知识产权战略合作伙伴”。

(校对/赵月)